Integrated circuit package structure and manufacturing technology thereof

A technology of integrated circuit and packaging structure, which is applied in the direction of circuits, electrical components, and electrical solid devices, and can solve the problems of large thickness of QFN/DFN products, and achieve the effects of shortening the design cycle, increasing the bonding area, and dense I/O

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

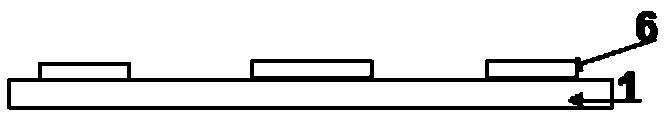

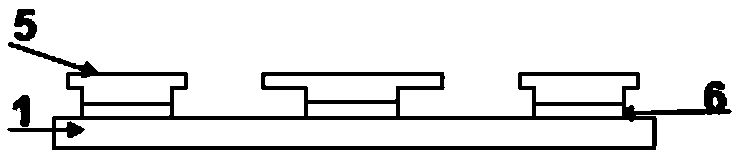

[0031] Such as Figure 9 As shown, a film-free and electroplating-free package based on bonding wire connection also includes metal bumps 2 . The chamfered silver-plated layer 5 is a mutually independent silver-plated layer segment, a part of the chamfered silver-plated layer 5 has a chip 3, and a part of the chamfered silver-plated layer 5 has a metal bump 2, and the chip 3 and the metal bump The point 2 is connected by the bonding wire 7, the plastic package 4 surrounds the metal bump 2, the chip 3, the chamfered silver-plated layer 5, the nickel-palladium-gold layer 6 and the bonding wire 7, the metal bump 2, the chip 3, the chamfered Angle silver plated layer 5, nickel palladium gold plated layer 6 and bonding wire 7 constitute the power supply and signal channel of the circuit. Such as Figure 13 As shown, a film-free and electroplating-free package based on bonding wire connection can also be used without metal bumps, and the bonding wire can be directly hit on the pad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com