A kind of array substrate and its preparation method and display device

An array substrate and display area technology, which is applied in semiconductor/solid-state device manufacturing, instrumentation, semiconductor/solid-state device testing/measurement, etc., can solve problems such as increased space occupied by test components, scattered distribution of test components, and reduced test efficiency. Achieve the effects of improving timeliness, saving space, and reducing process testing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

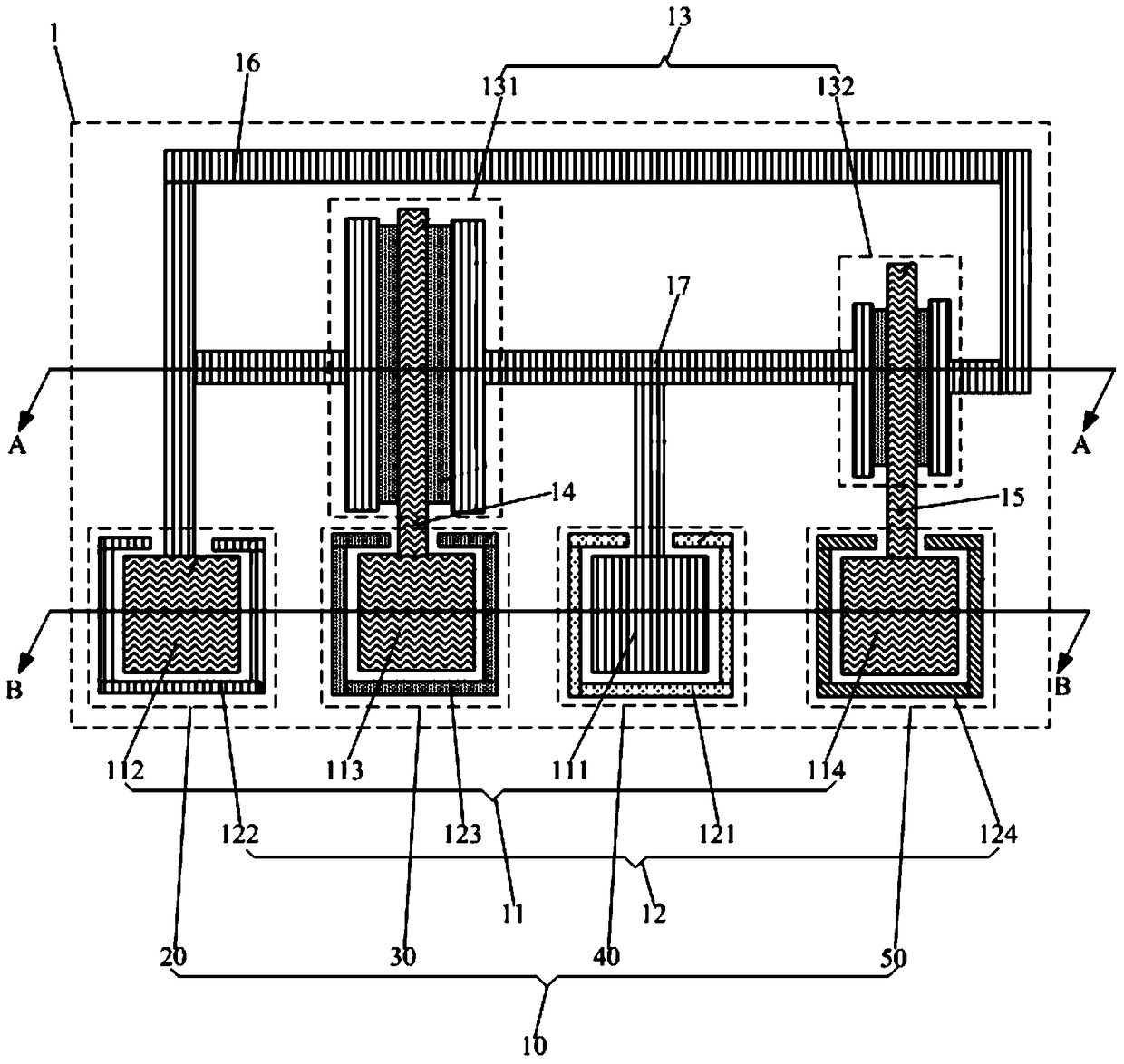

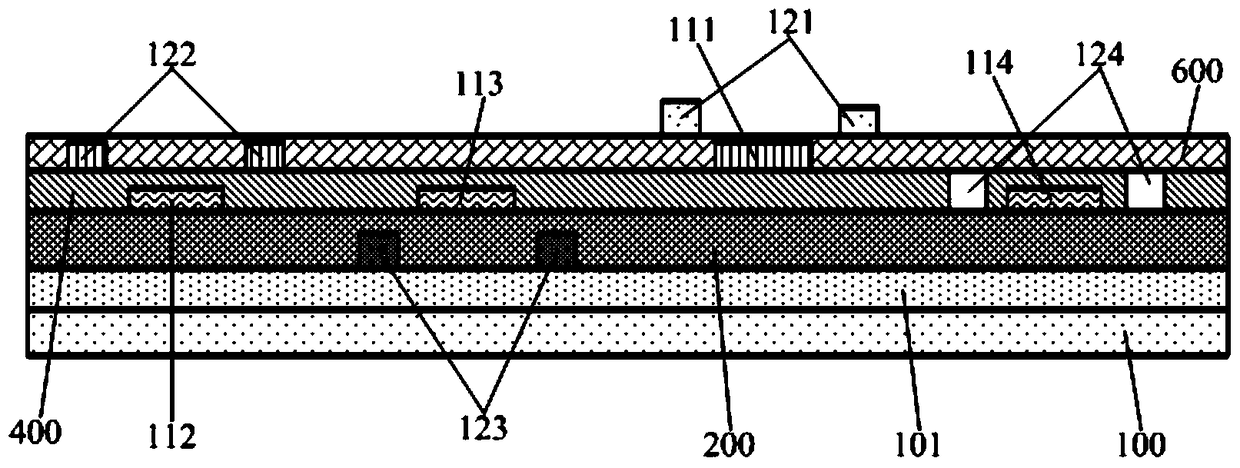

[0053] This embodiment provides an array substrate, such as figure 1 with figure 2 As shown, it includes a multi-layer pattern layer arranged in the display area and a test unit 1 arranged in a non-display area. The test unit 1 includes at least one test assembly 10 and a test transistor 13. The test assembly 10 includes a test block pattern 11 and a test line. Graphic 12; test block graphics 11 and one layer of the multi-layer pattern layer are arranged on the same layer, and one layer of the test line pattern 12 is set on the same layer as the multi-layer pattern layer, and the test block pattern 11 and the test line pattern 12 are different layers, The orthographic projection of the test line pattern 12 on the array substrate corresponds to the periphery of the orthographic projection of the test block pattern 11 on the array substrate; the test block pattern 11 is connected to the test transistor 13 .

[0054] In this embodiment, the orthographic projection of the test l...

Embodiment 2

[0086] This embodiment provides an array substrate. The difference from Embodiment 1 is that the test unit in this embodiment only includes one test component, and the test component can be the first test component, the second test component, the second test component, The third test component or the fourth test component; it can also be other test components similar to the first test component, the second test component, the third test component or the fourth test component in the arrangement.

[0087] In this embodiment, the test unit may or may not include a test transistor. The gate, source and drain of the test transistor can be connected to different test block patterns or test line patterns respectively, and the test signal is sent from the test block pattern or test line pattern; they can also not be connected to the test block pattern or test line pattern , directly sent to the test signal by the external test equipment.

[0088] It should be noted that the test unit i...

Embodiment 3

[0092] This embodiment provides a display device, including the array substrate in Embodiment 1 or 2.

[0093] By adopting the array substrate in Embodiment 1 or 2, not only the cost of the process capability test of the display device is reduced, but also the timeliness of the process capability test of the display device is improved.

[0094] The display device may be any product or component with a display function such as a mobile phone, a tablet computer, a television, a monitor, a notebook computer, a digital photo frame, a navigator, and the like.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More