Clock circuit used for high-speed high-precision SHA-less pipelined analog-to-digital converter

An analog-to-digital converter and pipeline technology, applied in the direction of analog-to-digital converter, analog-to-digital conversion, code conversion, etc., can solve the problems of compression and amplification phase time, difficulty in the design of operational amplifiers in the first-stage pipeline, etc. Design pressure, reduce design complexity, and increase the effect of design margins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the technical means, creative features, goals and effects achieved by the present invention easy to understand, the present invention will be further described below in conjunction with specific illustrations.

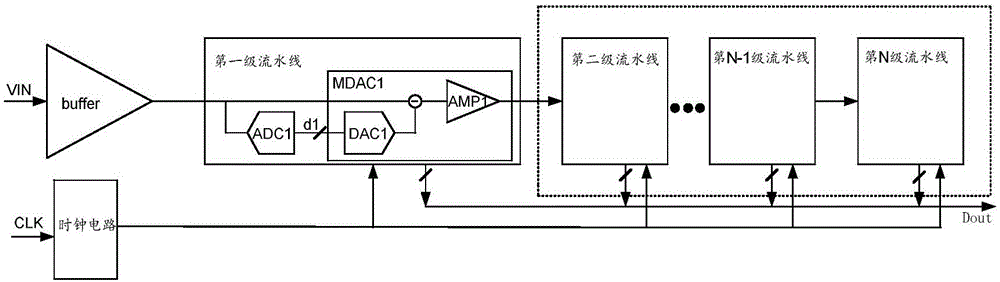

[0040] Please refer to Figure 5 As shown, the present invention provides a clock circuit for a high-speed, high-precision pipeline-type analog-to-digital converter without mining protection, including a first duty cycle stabilization circuit DCS1 (DCS, DutyCycleStabilizer), a second duty cycle stabilization circuit DCS2 and the first to The Nth output clock buffer Buffer1-BufferN, N is the number of stages of the pipeline; where,

[0041] The first duty cycle stabilization circuit DCS1 is adapted to adjust the duty cycle of any externally input duty cycle clock signal CLK to generate an adjustable clock with a duty cycle of less than 50%, which is used for the first-stage pipeline timing control;

[0042] The second duty cycle stabilization c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More