Patents

Literature

118results about How to "Increase design margin" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

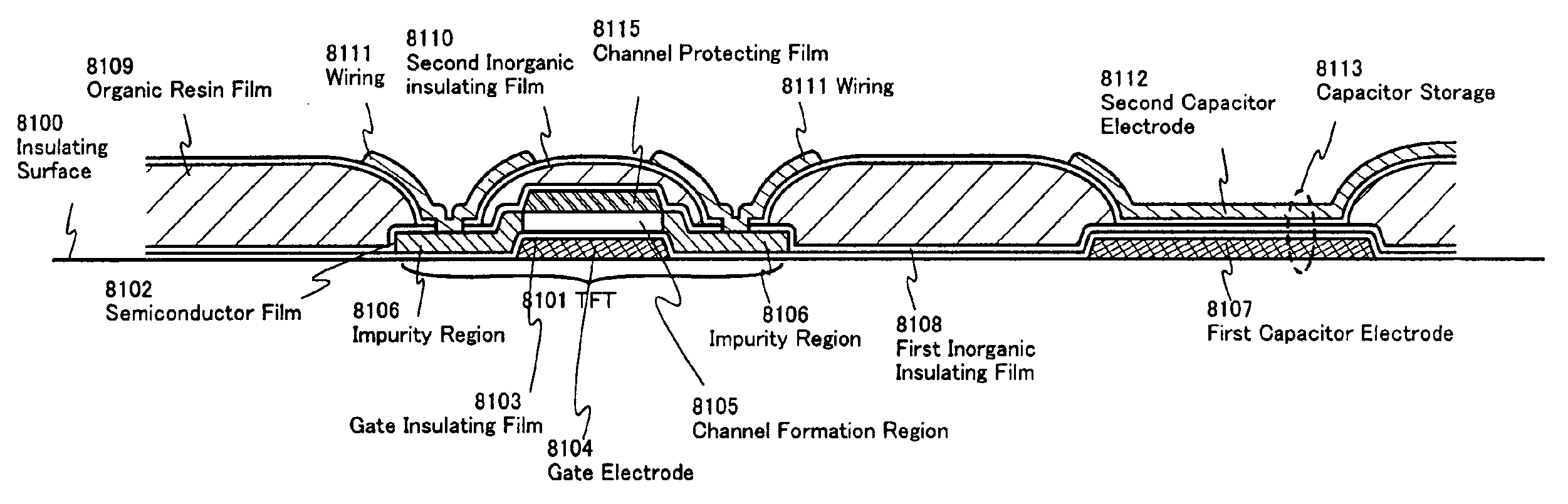

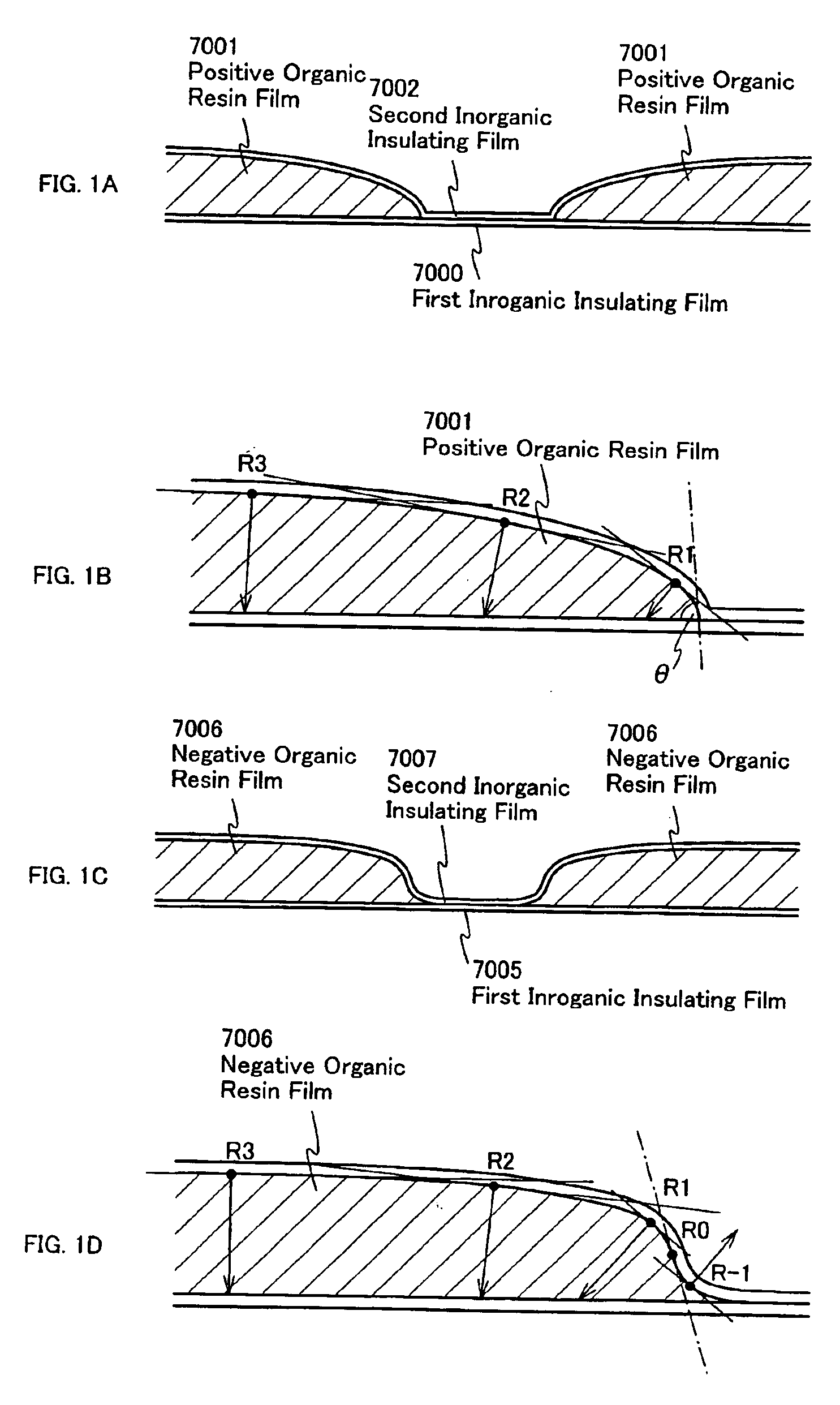

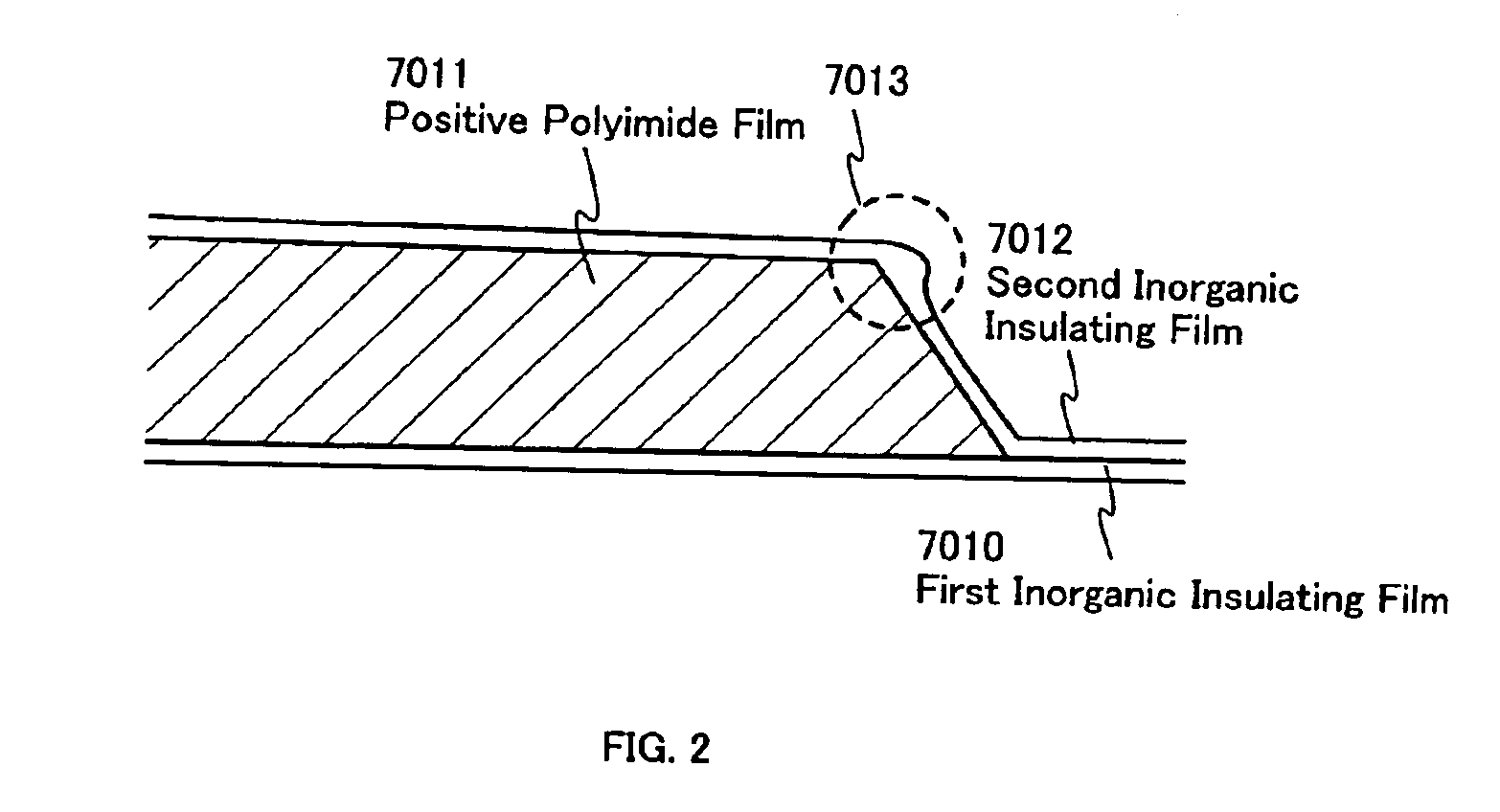

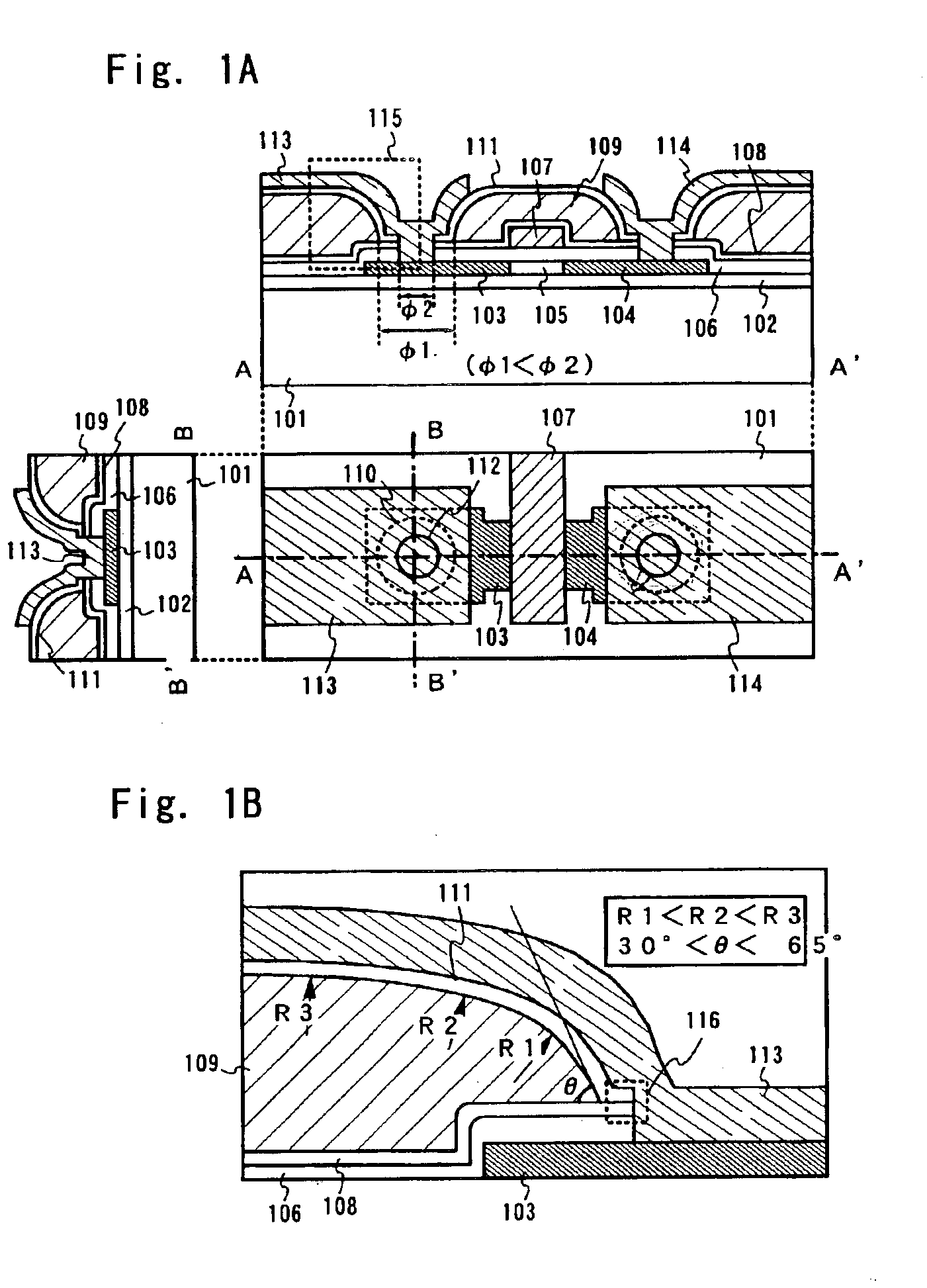

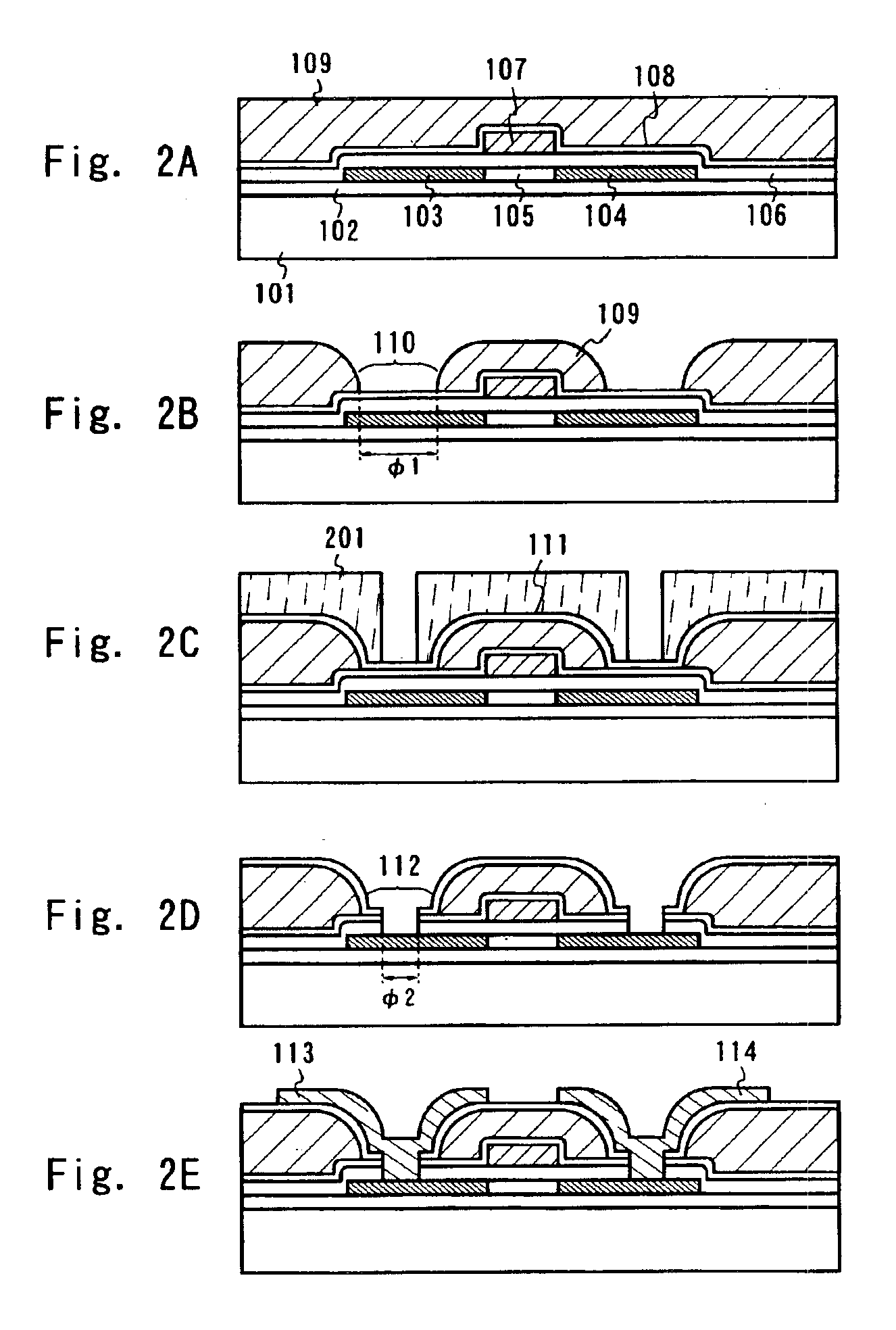

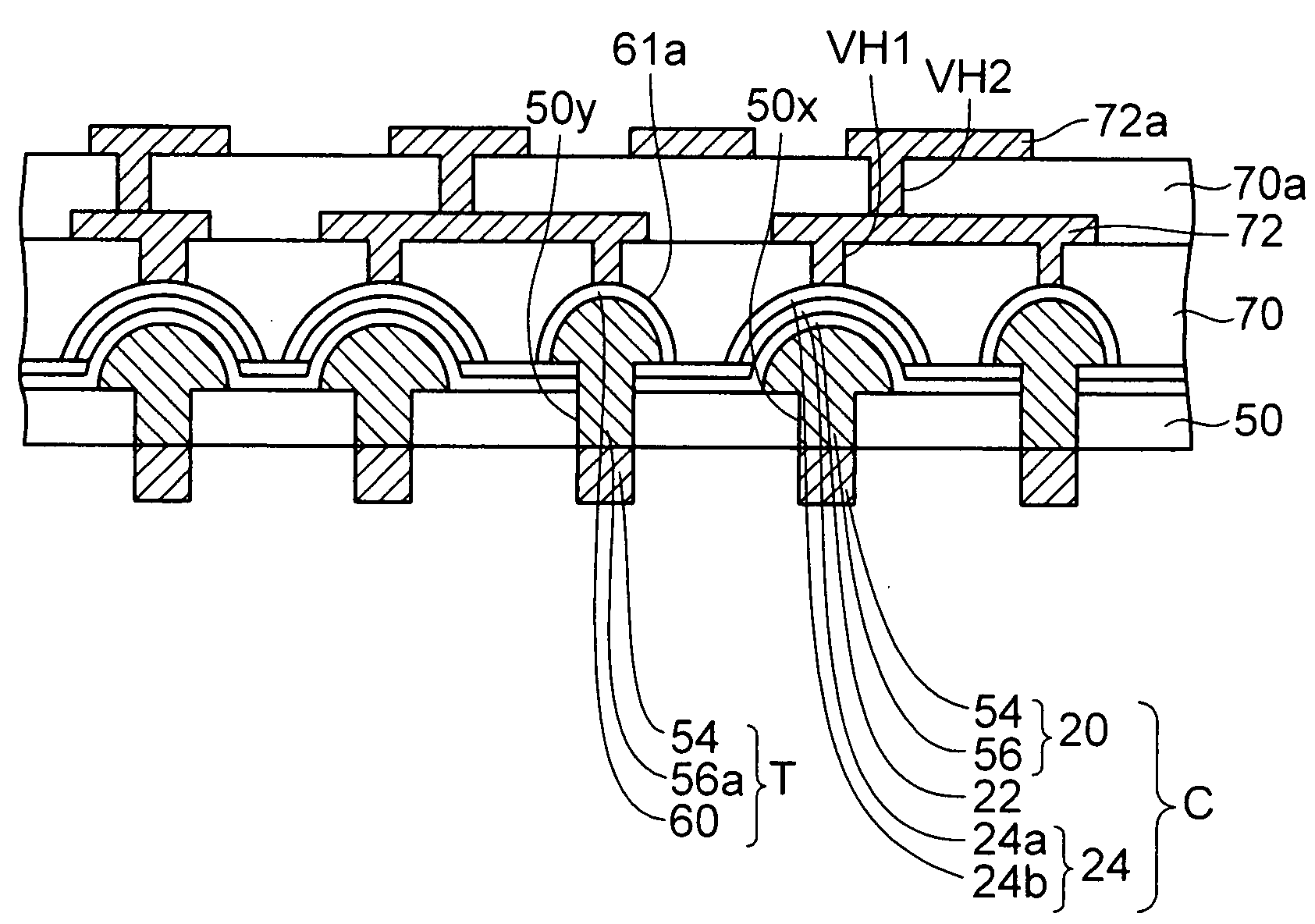

Semiconductor display device and manufacturing method thereof

InactiveUS6911688B2Limited film formation timeSurface levelnessTransistorSemiconductor/solid-state device detailsAcrylic resinDisplay device

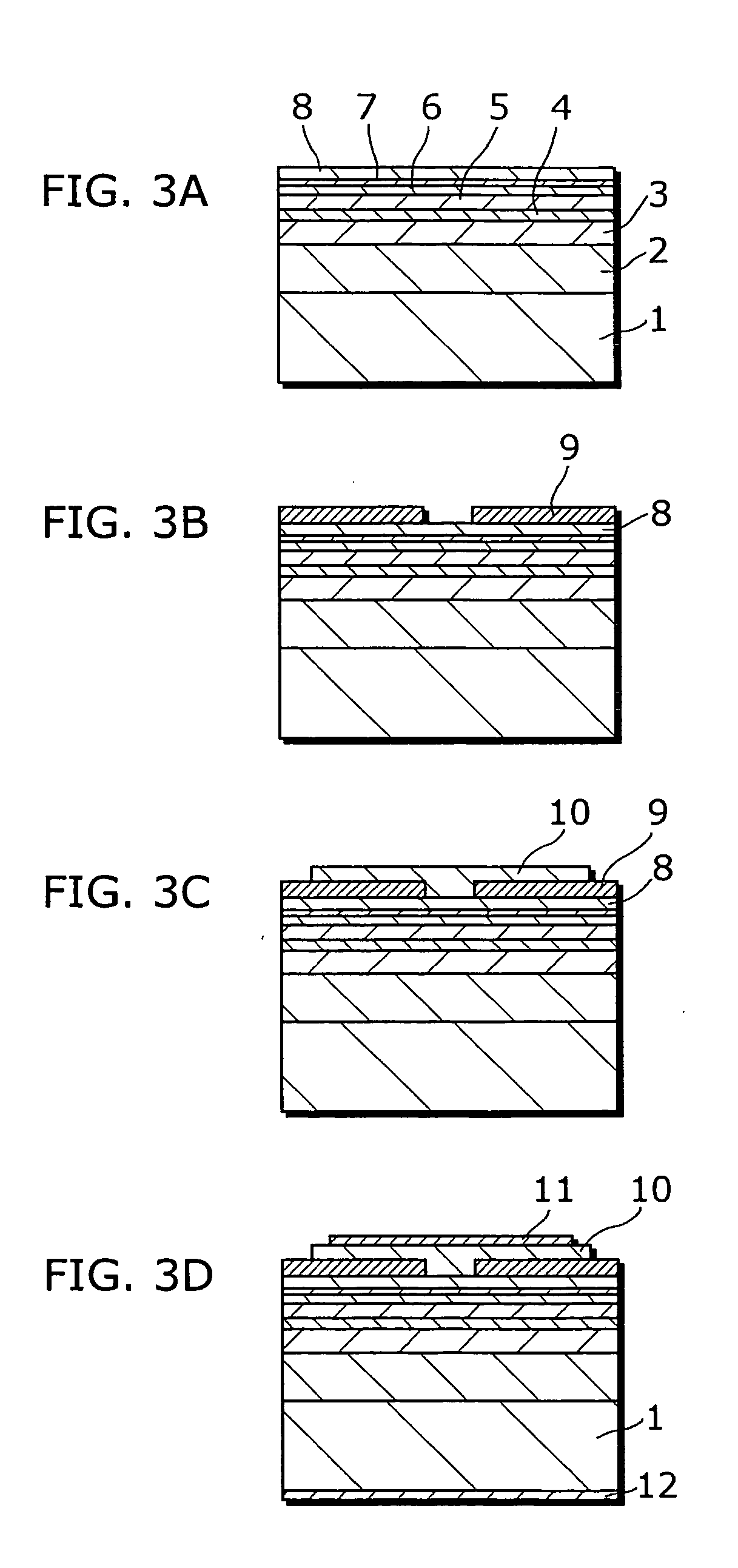

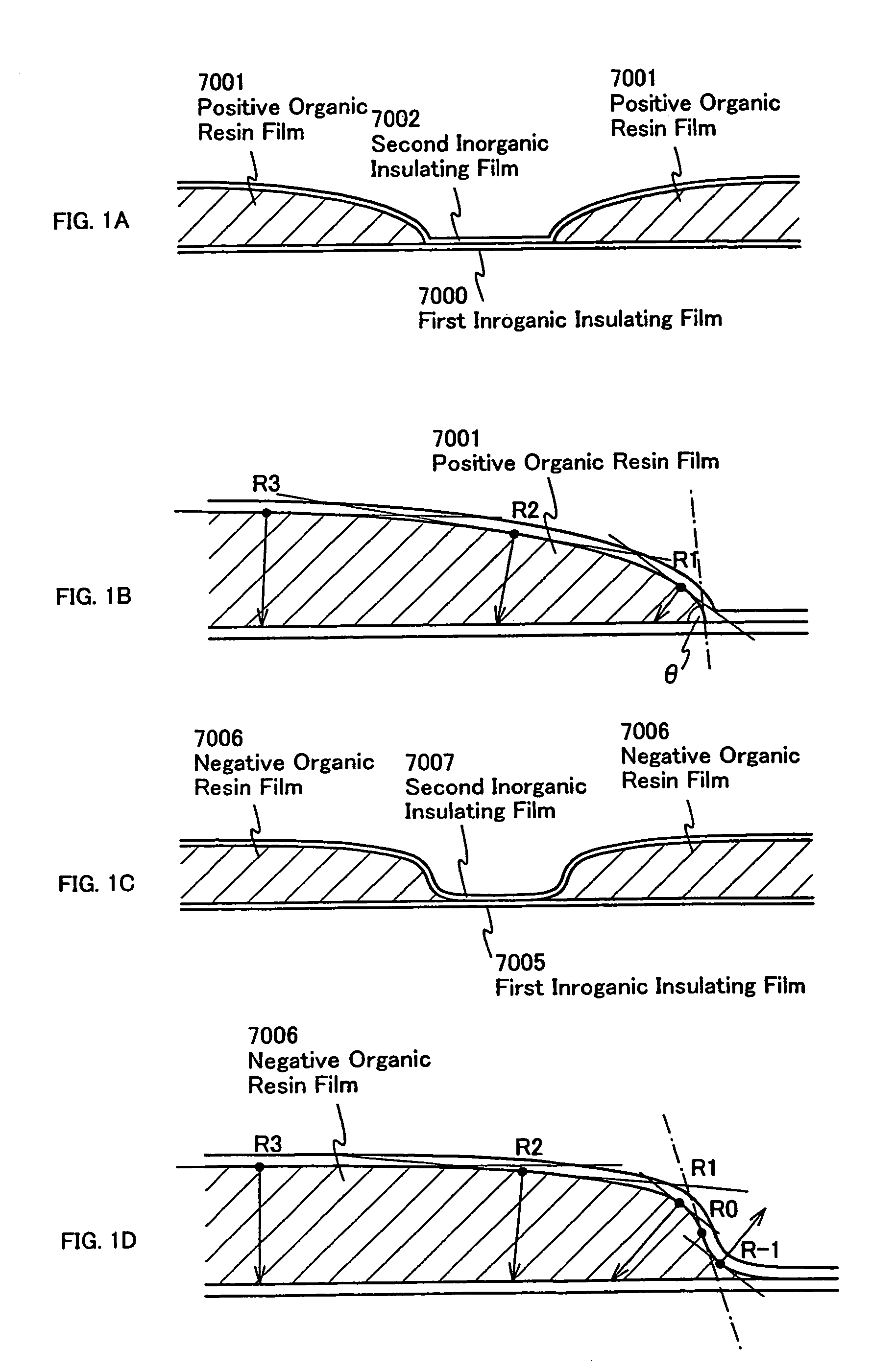

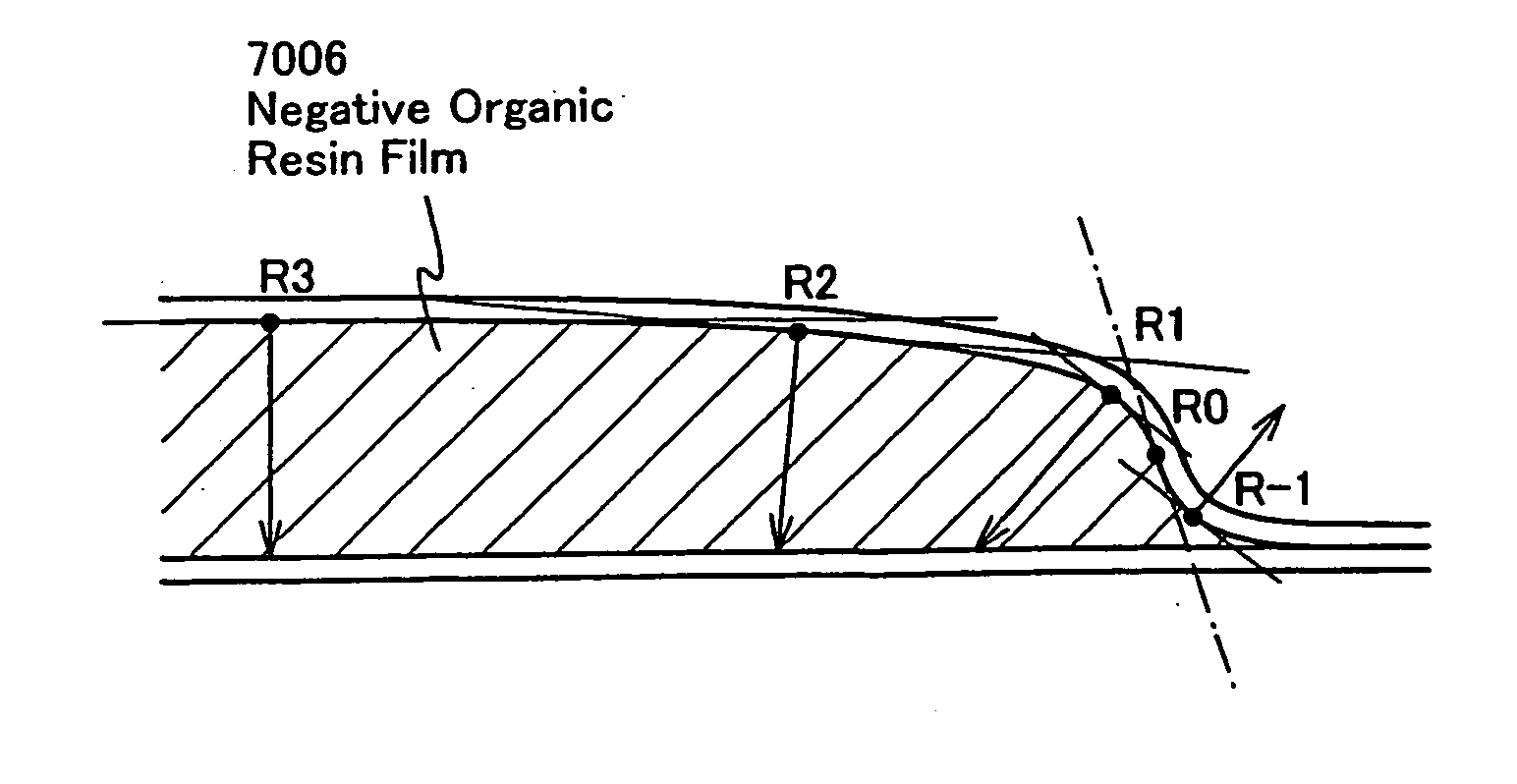

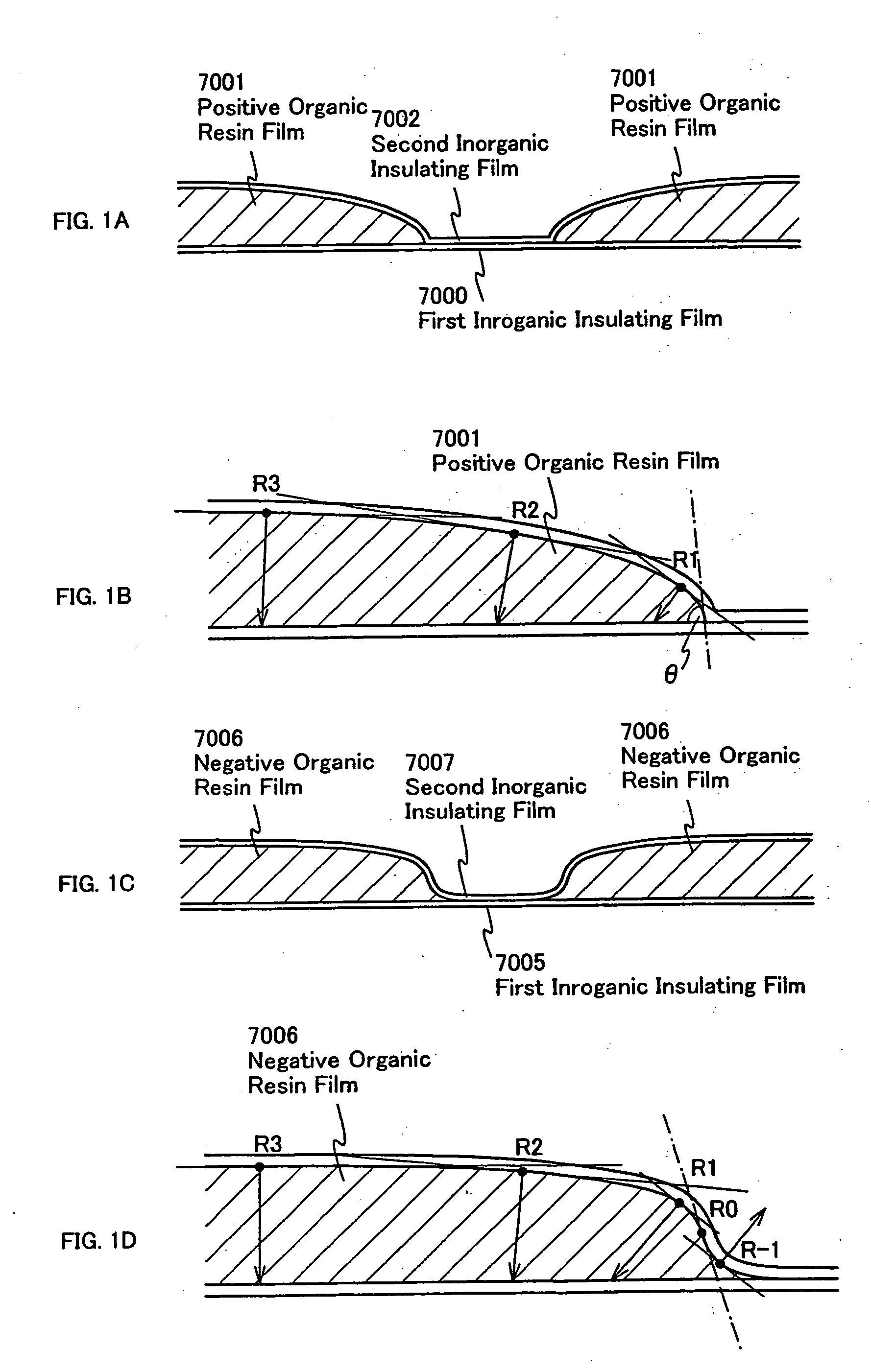

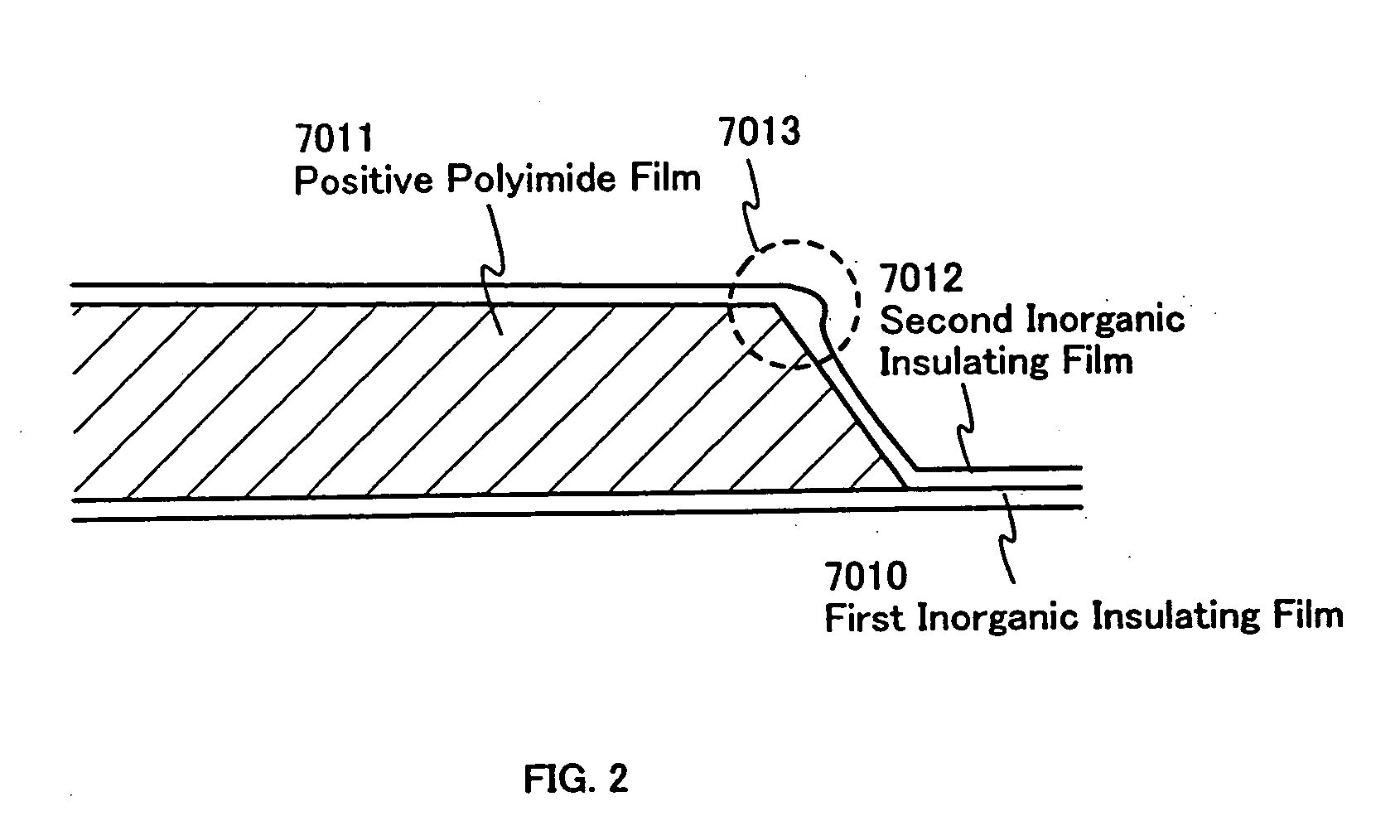

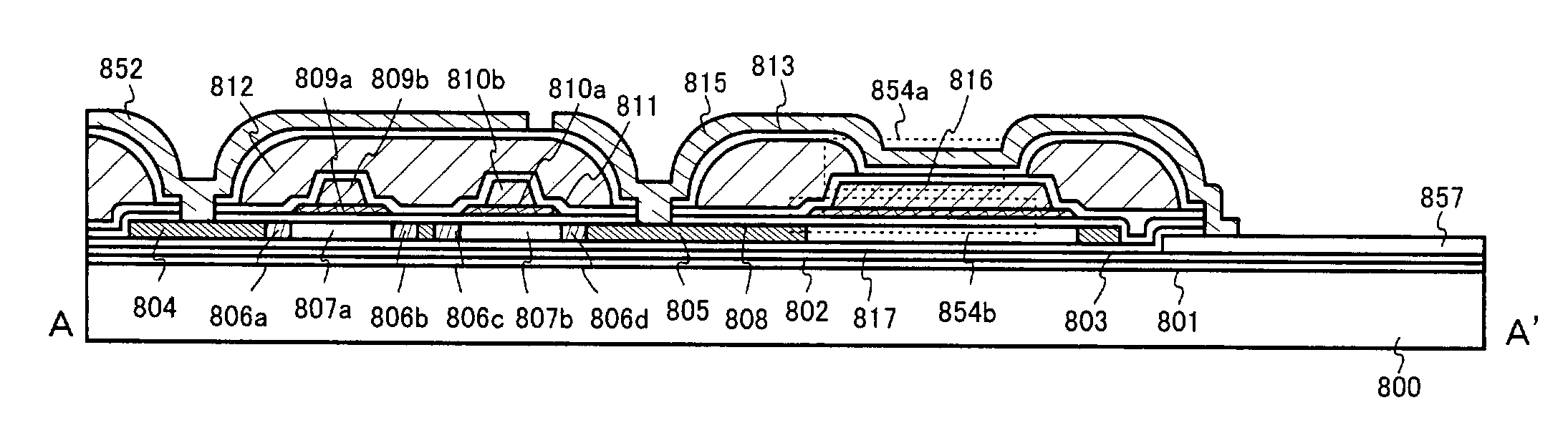

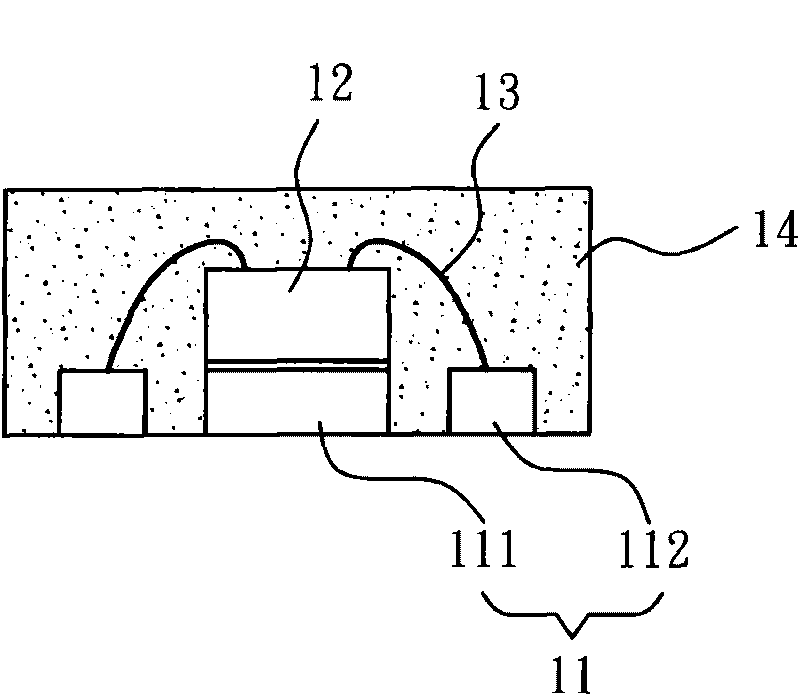

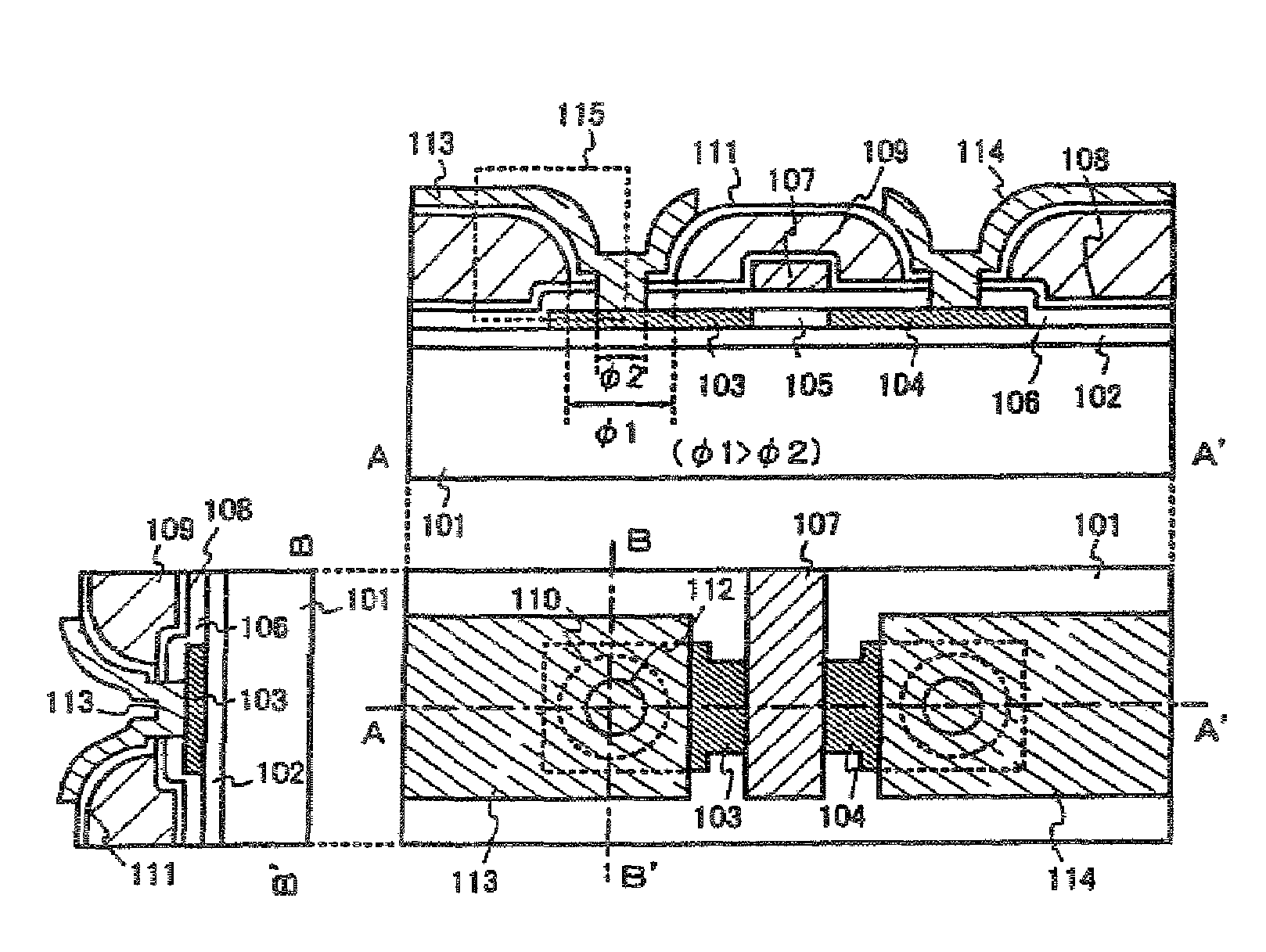

A semiconductor display device with an interlayer insulating film in which surface levelness is ensured with a limited film formation time, heat treatment for removing moisture does not take long, and moisture in the interlayer insulating film is prevented from escaping into a film or electrode adjacent to the interlayer insulating film. A TFT is formed and then a nitrogen-containing inorganic insulating film that transmits less moisture compared to organic resin film is formed so as to cover the TFT. Next, organic resin including photosensitive acrylic resin is applied and an opening is formed by partially exposing the organic resin film to light. The organic resin film where the opening is formed, is then covered with a nitrogen-containing inorganic insulating film which transmits less moisture than organic resin film does. Thereafter, the gate insulating film and the two layers of the nitrogen-containing inorganic insulating films are partially etched away in the opening of the organic resin film to expose the active layer of the TFT.

Owner:SEMICON ENERGY LAB CO LTD

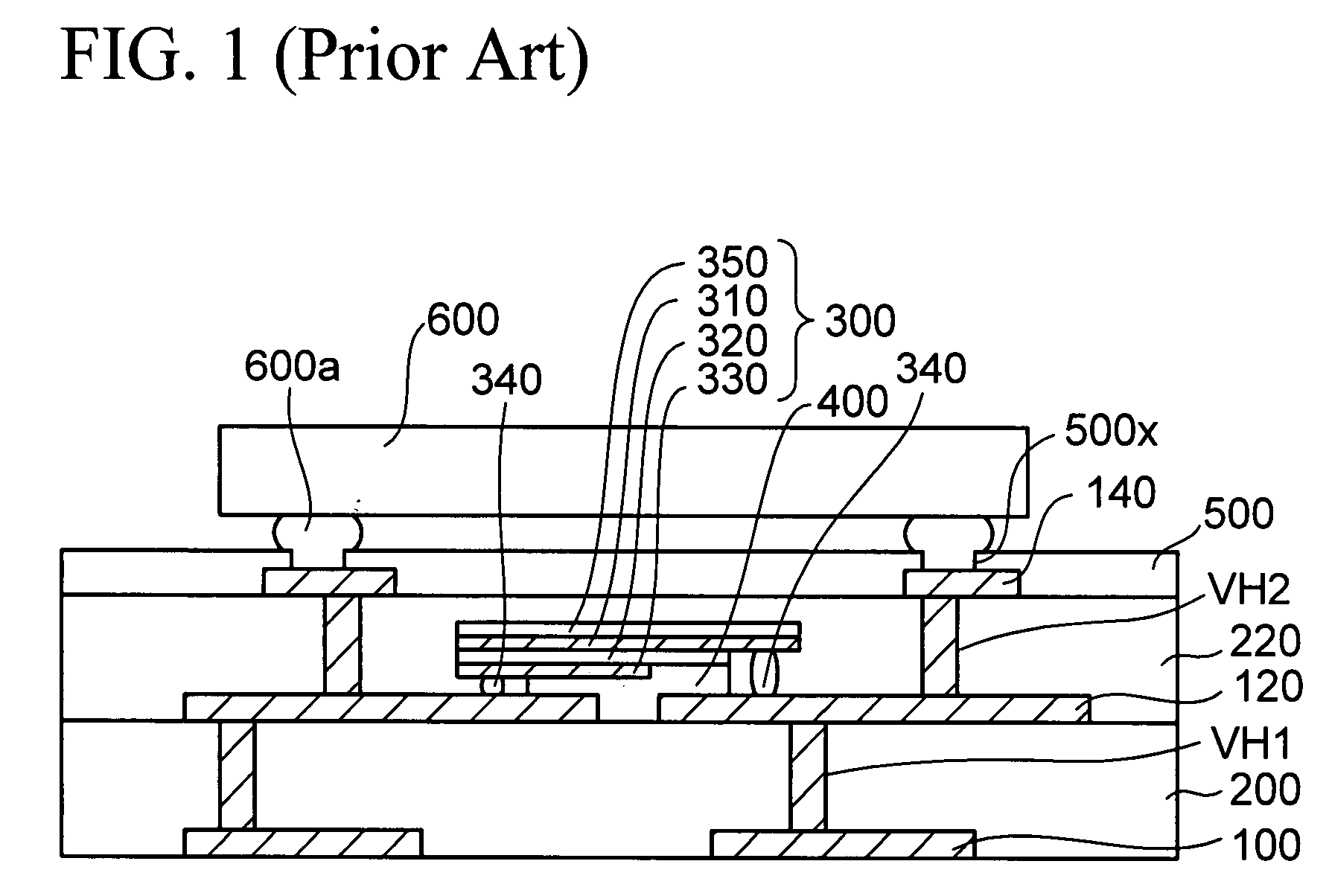

Semiconductor element and display device using the same

InactiveUS7038239B2Improvement of operating performance stabilityIncrease design marginTransistorSemiconductor/solid-state device detailsDisplay deviceActive layer

Owner:SEMICON ENERGY LAB CO LTD

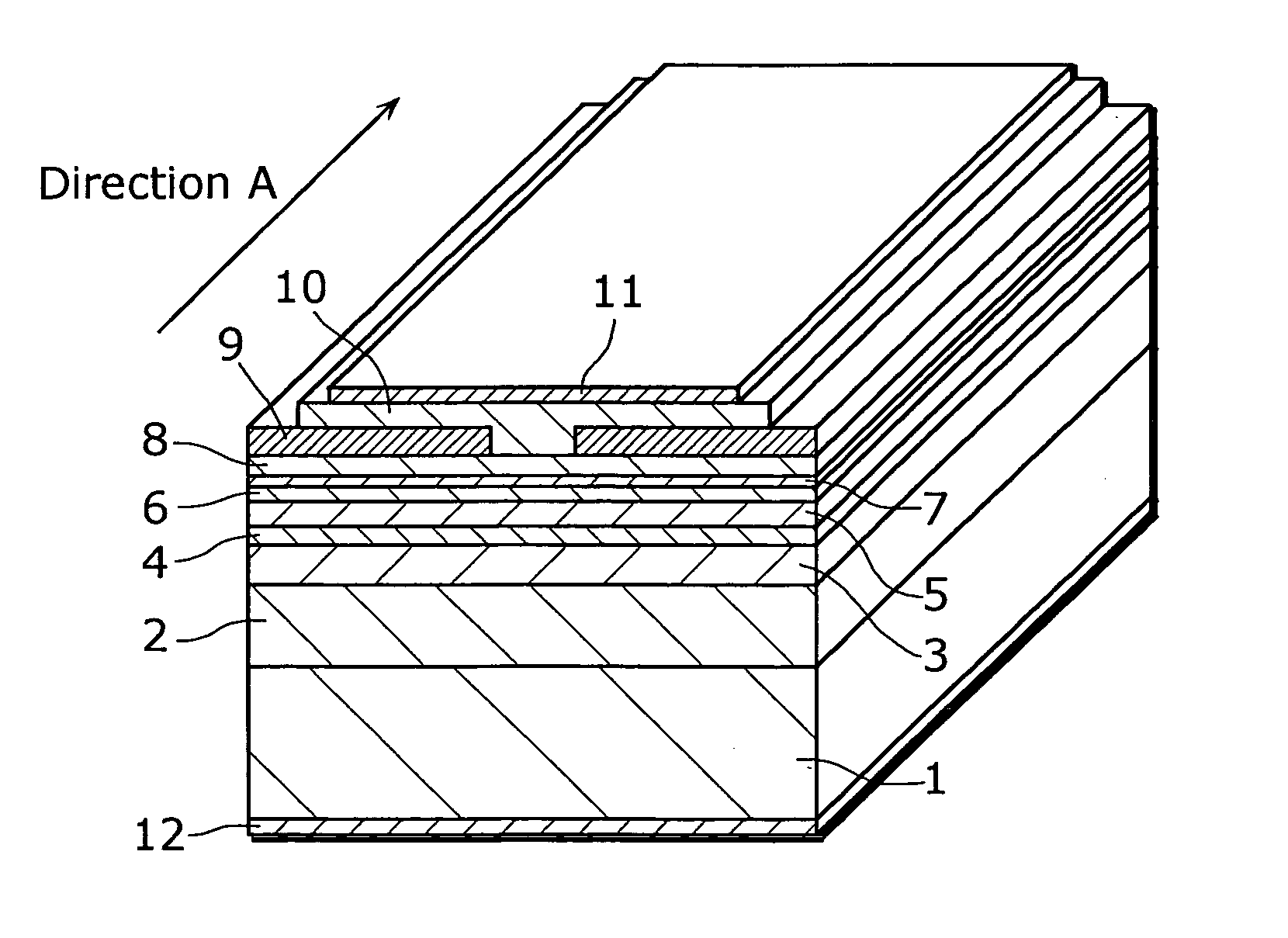

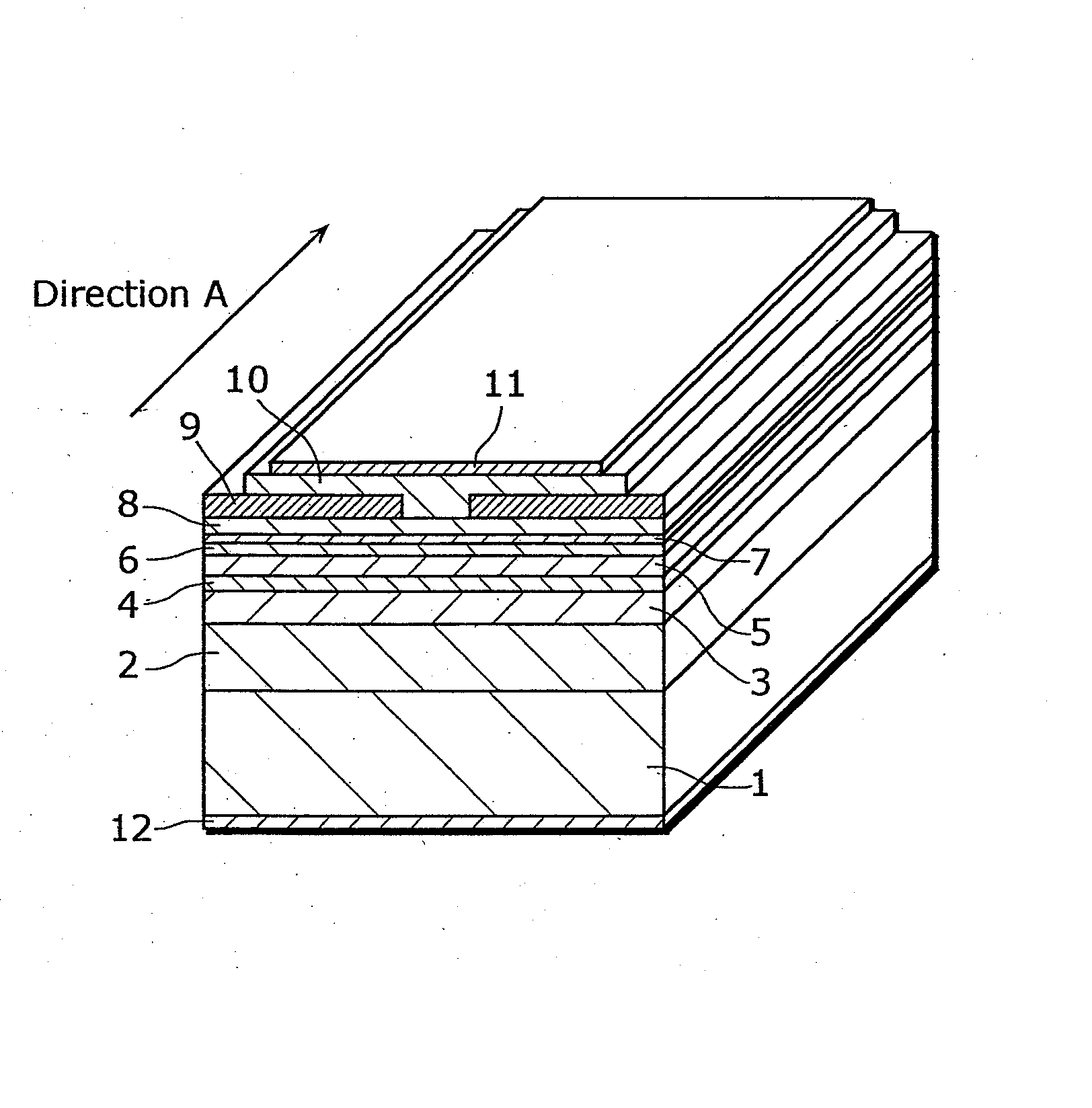

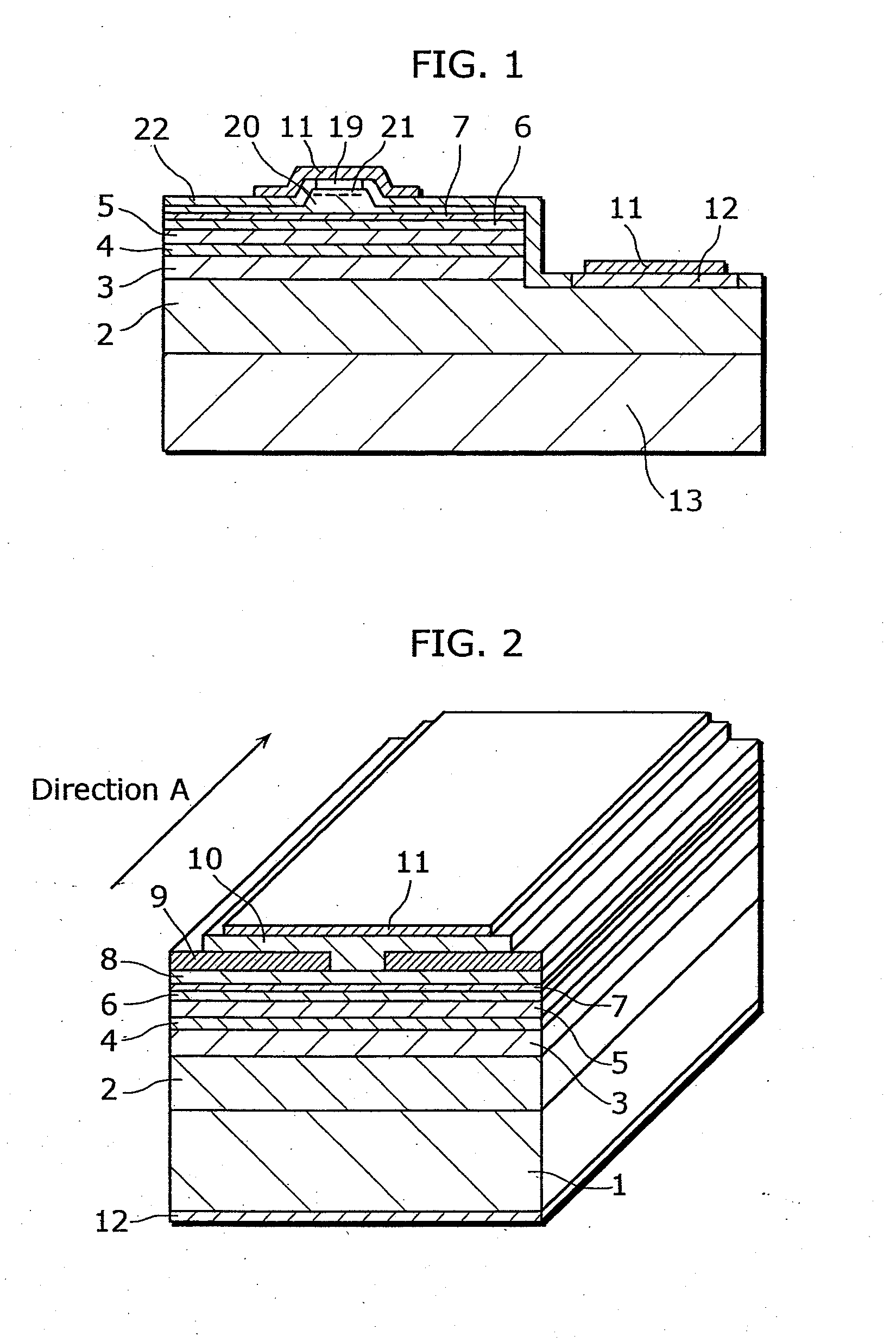

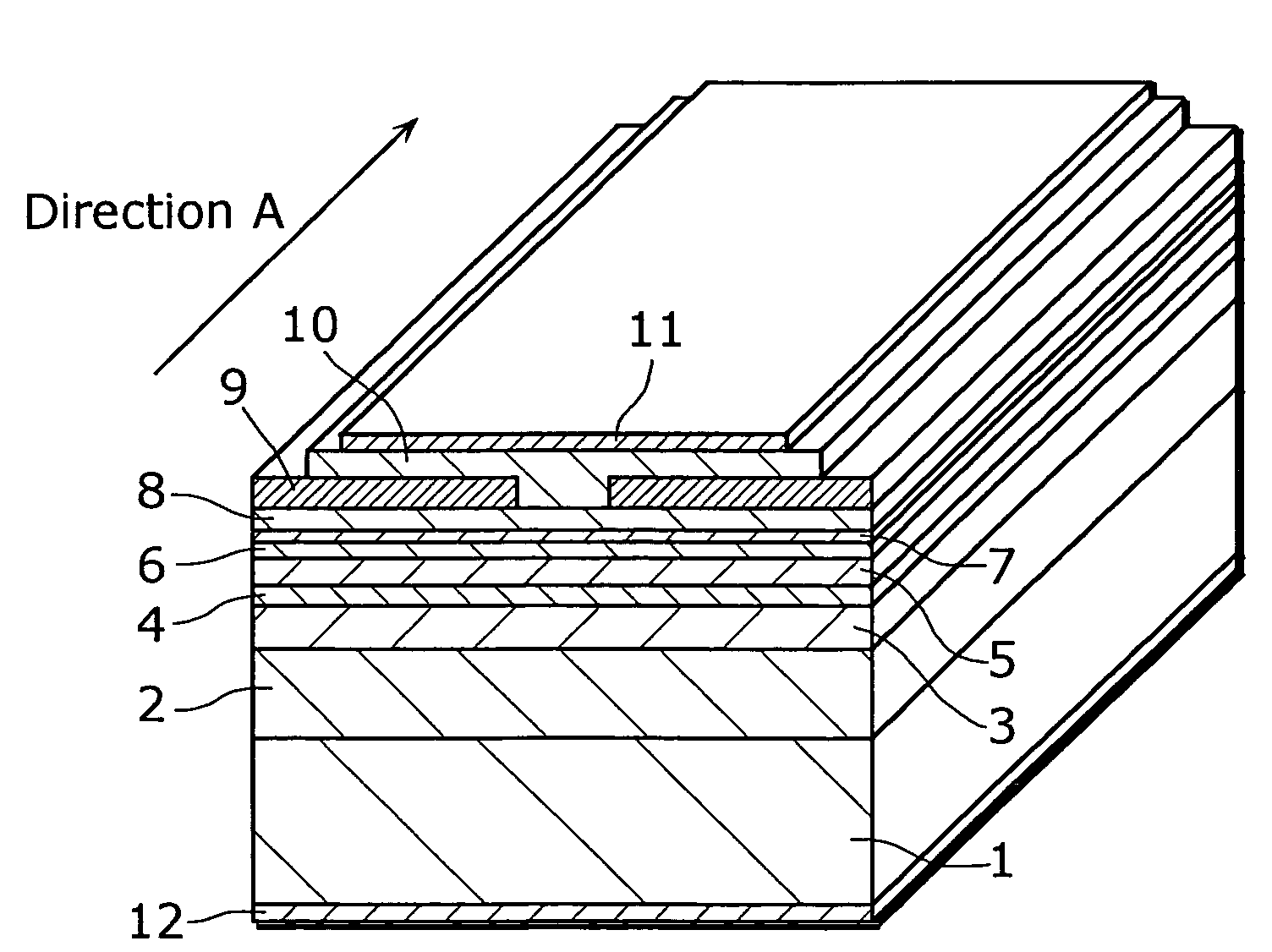

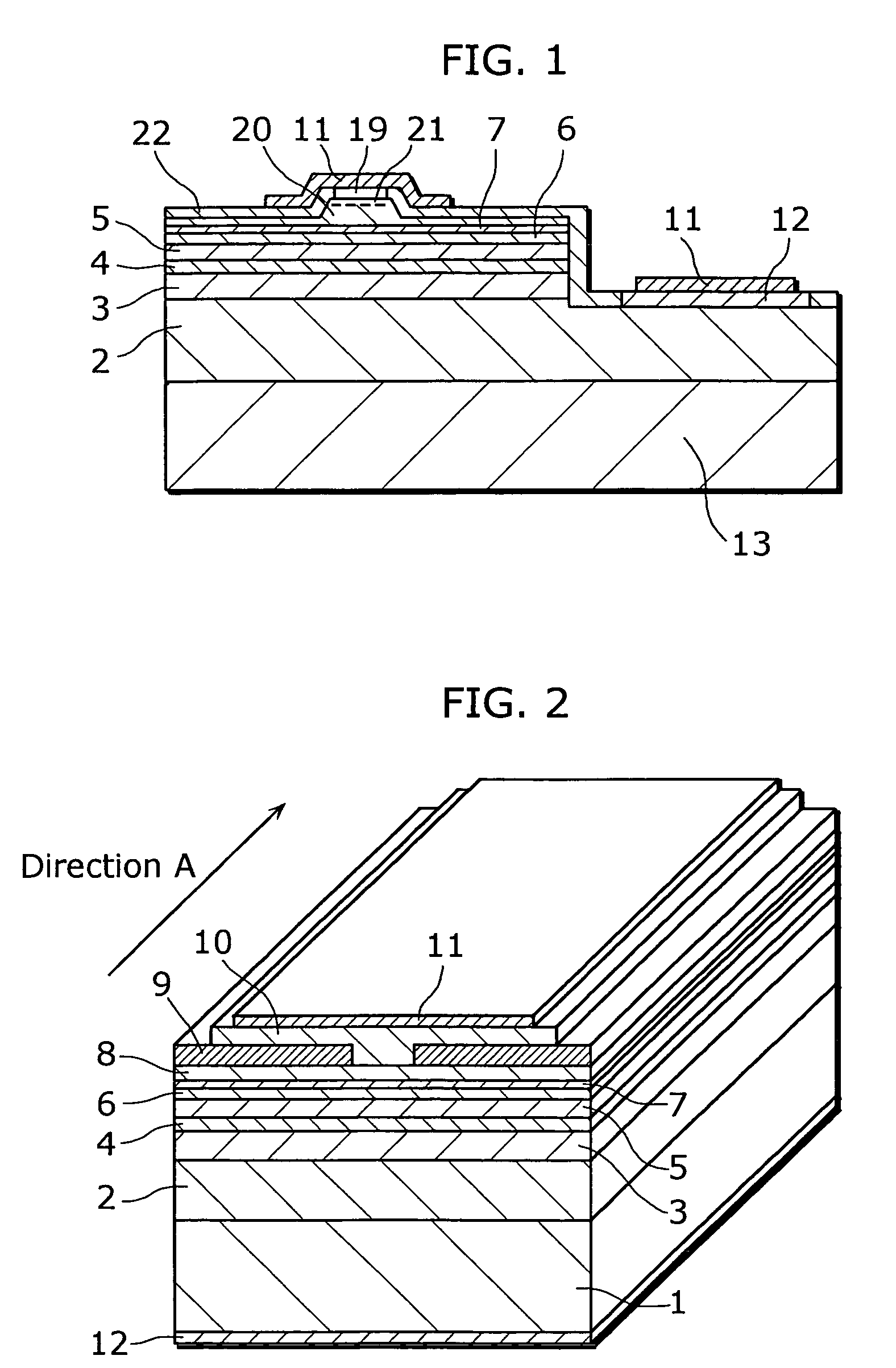

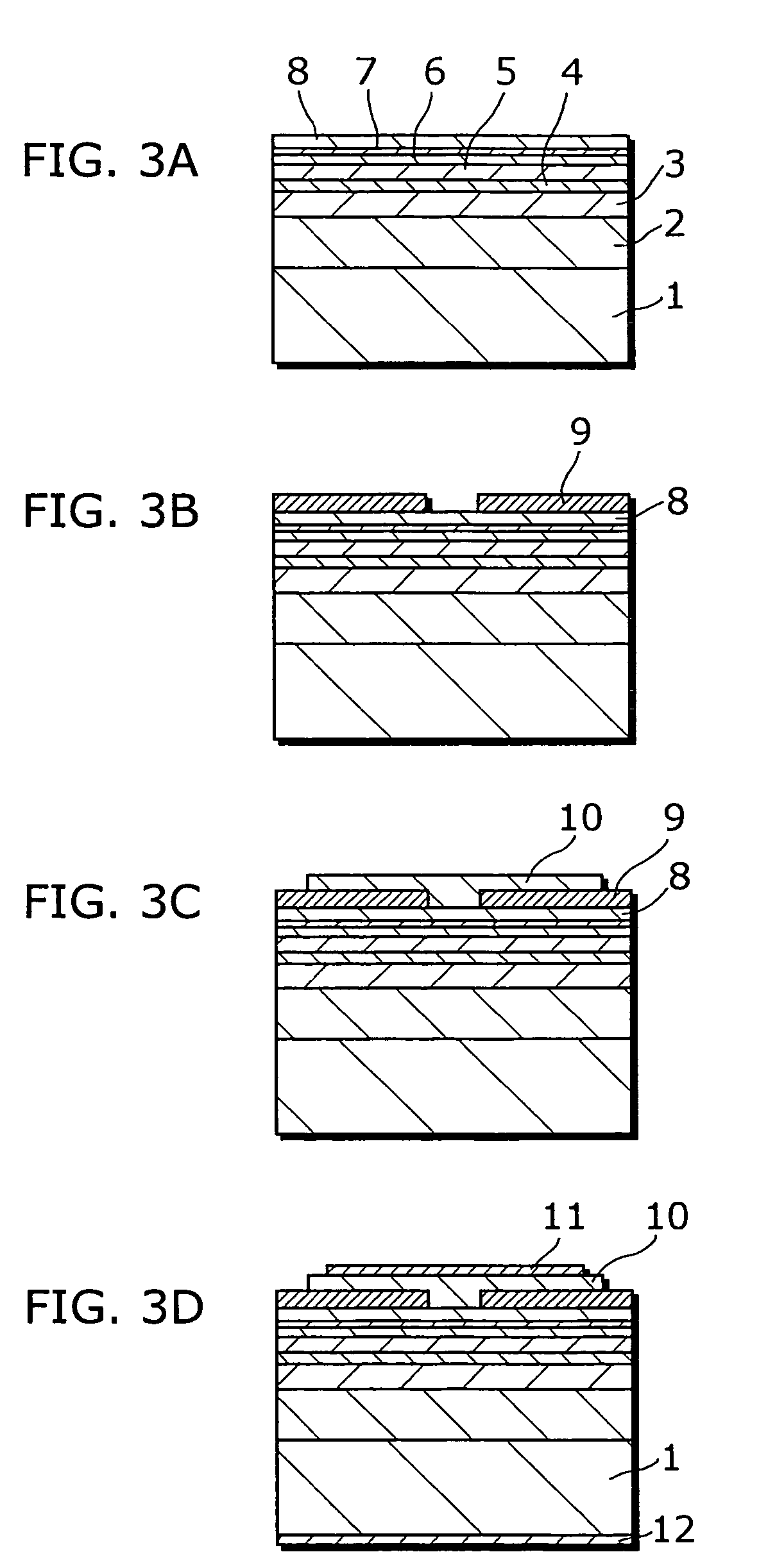

Semiconductor laser device and manufacturing method thereof

ActiveUS20050279994A1High yieldLow costOptical wave guidanceLaser detailsActive layerSilicon dioxide

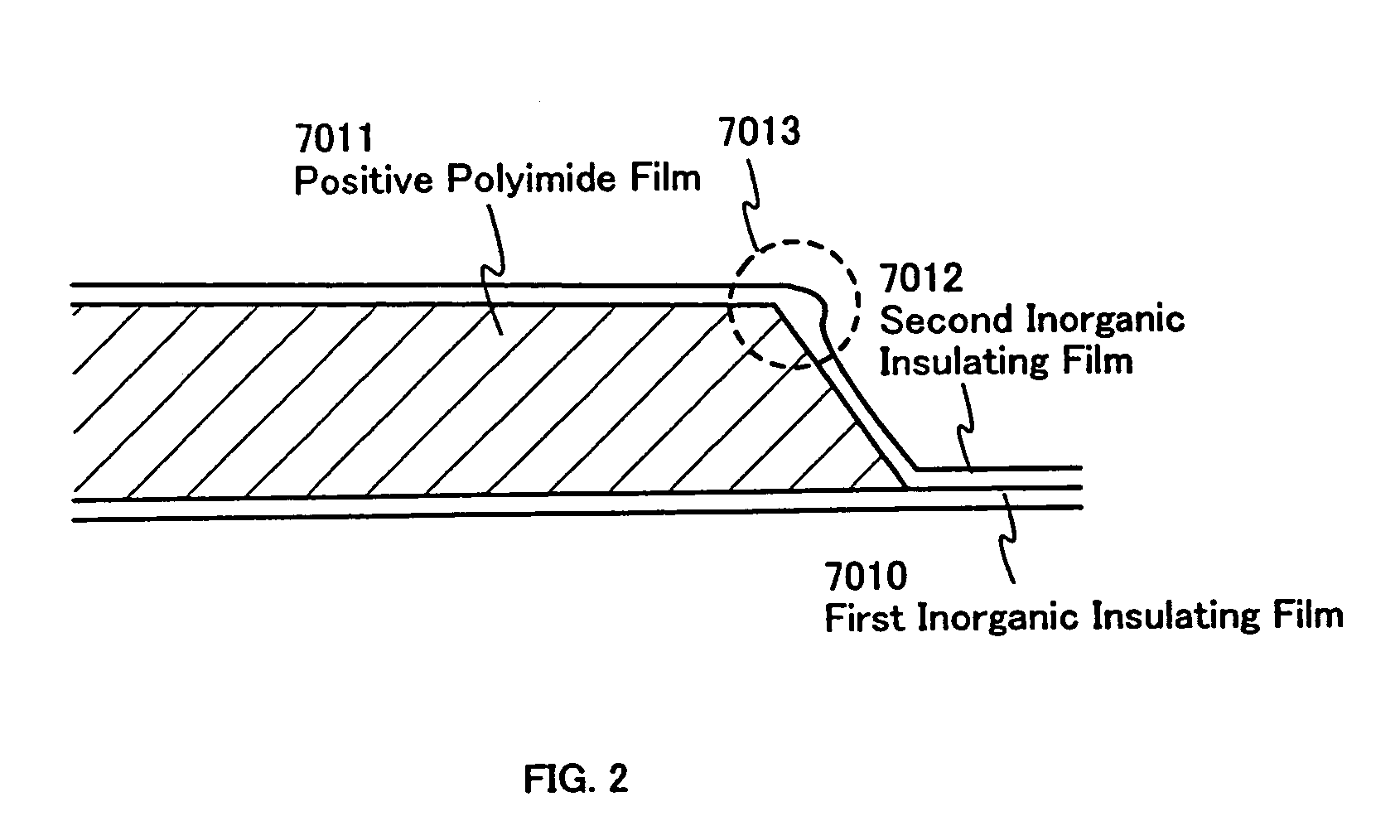

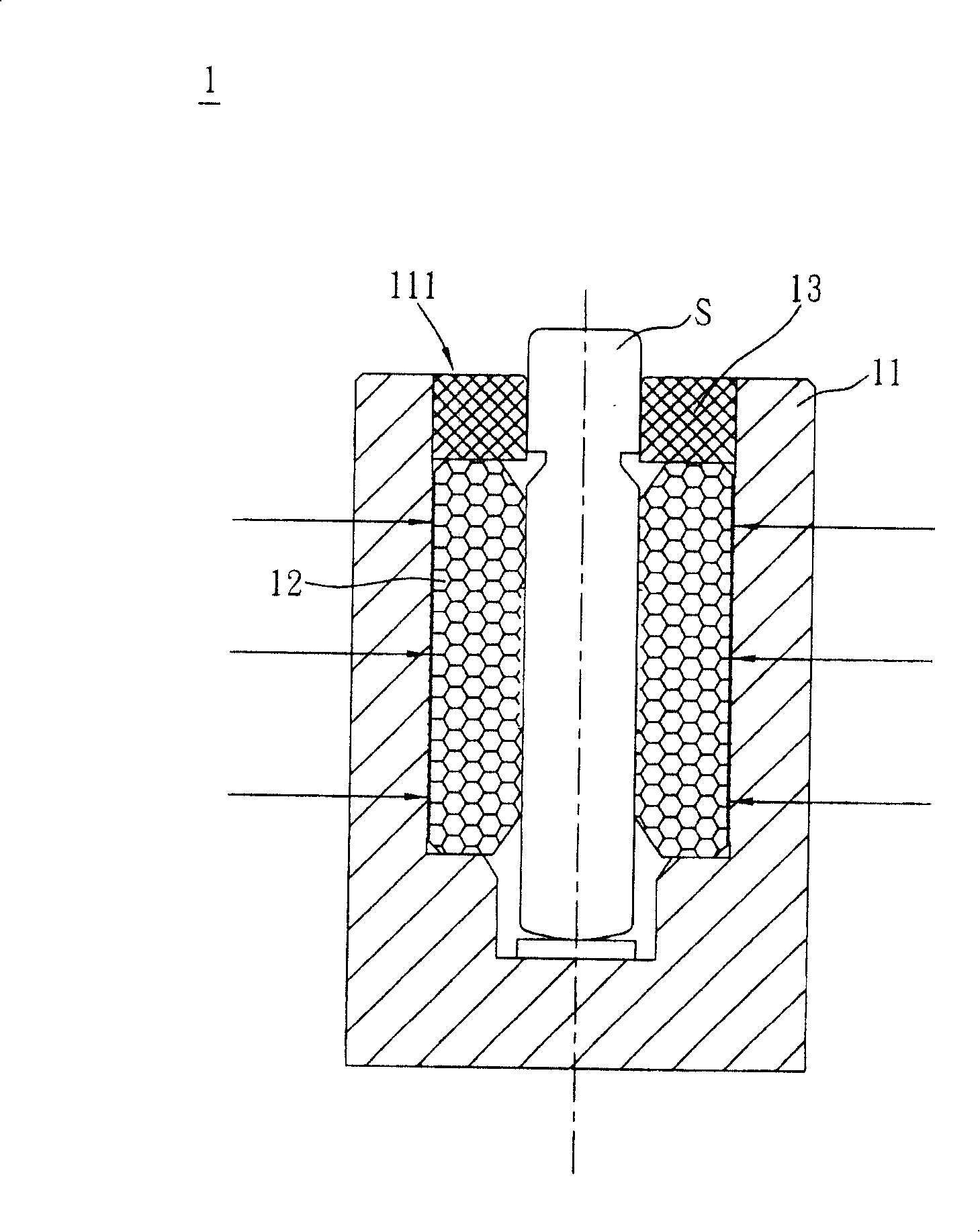

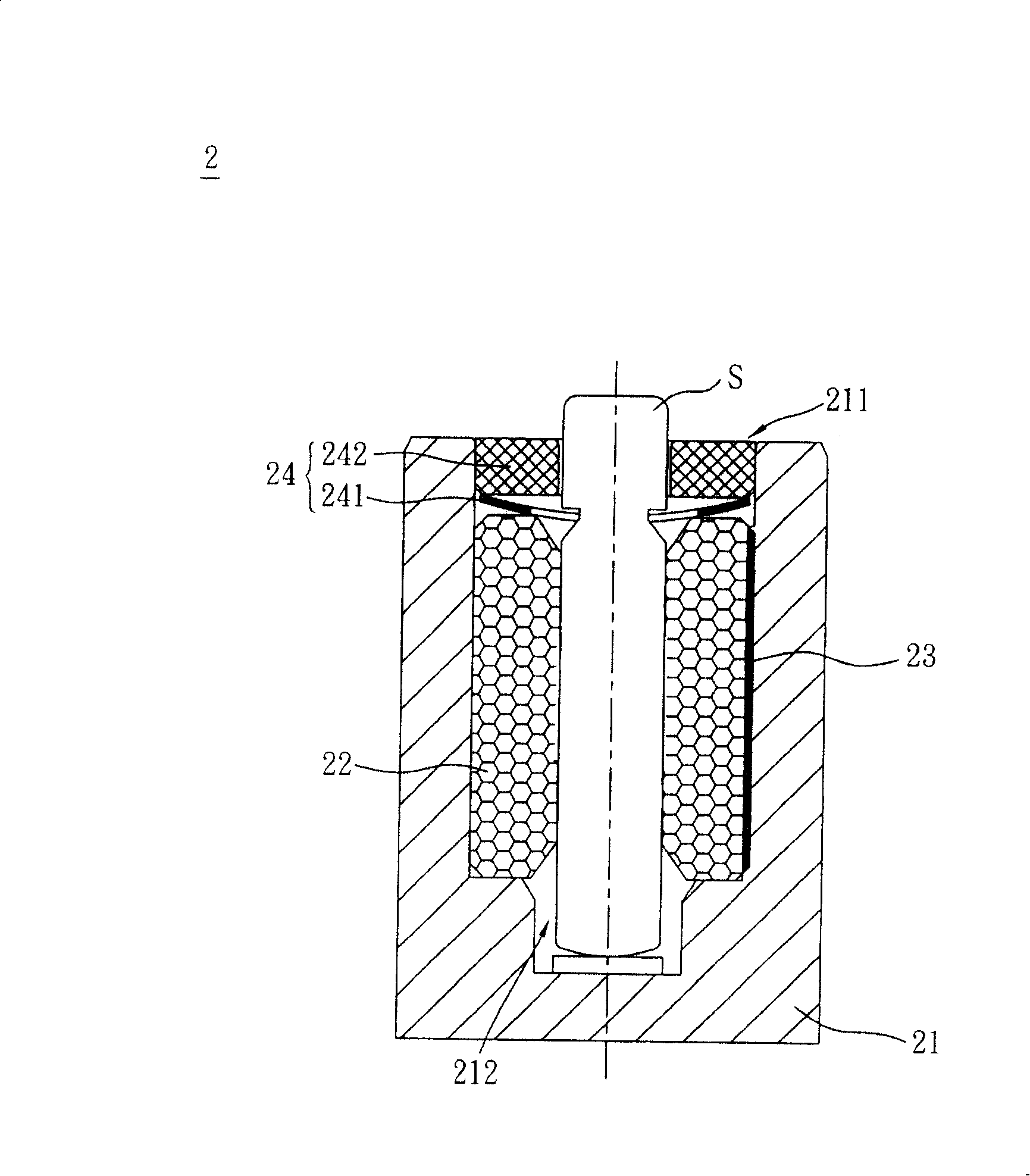

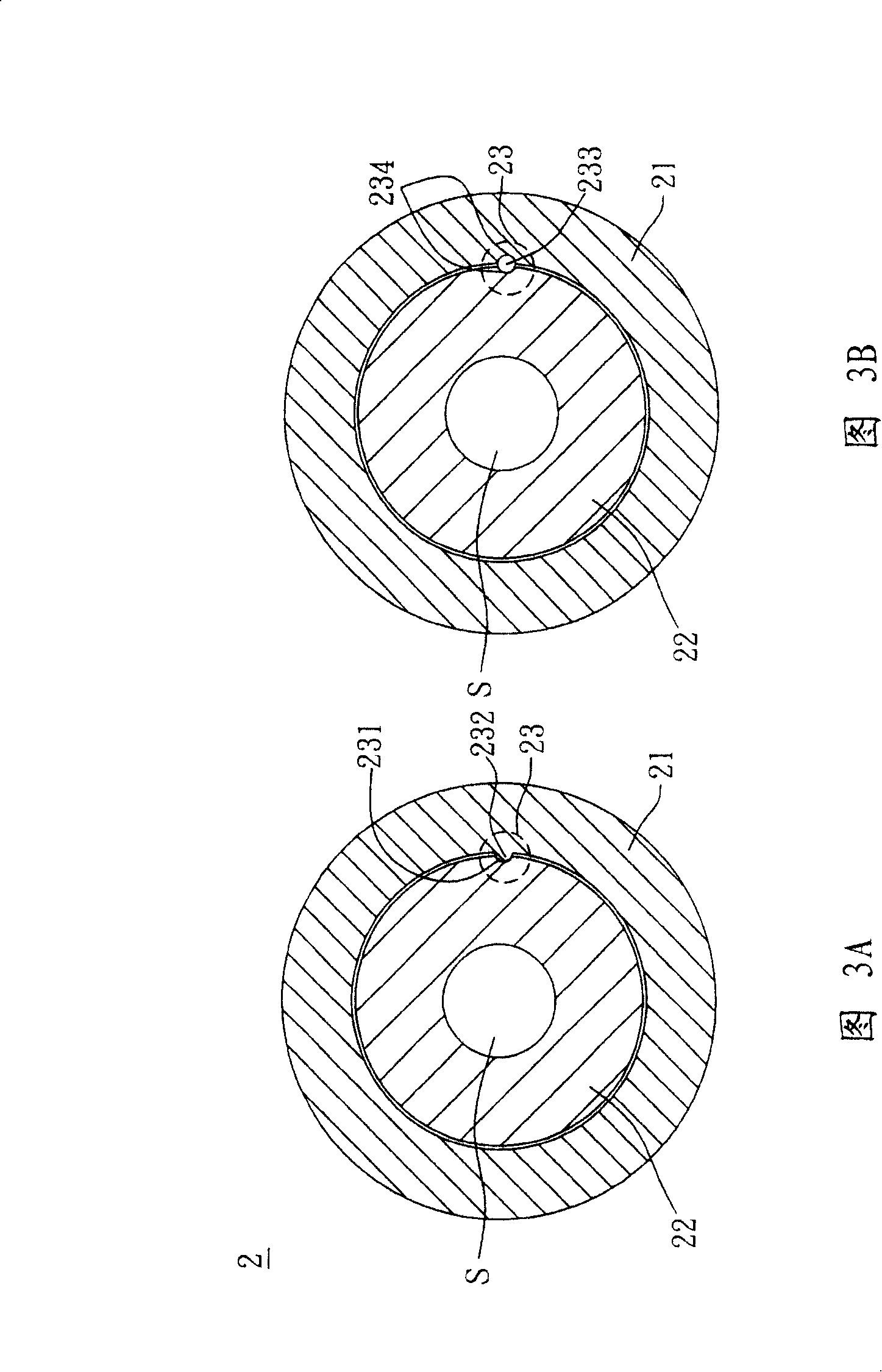

It is an object of the present invention to provide a semiconductor laser device with high-yielding in which a clack generated in an epitaxial growth layer is restrained and to the manufacturing method thereof, the semiconductor laser device includes a GaN substrate 1, an n-type GaN layer 2, an n-type AlGaN cladding layer 3, a n-type GaN guide layer 4, an InGaN multiple quantum well active layer 5, an undoped-GaN guide layer 6, a p-type AlGaN electron overflow suppression layer 7, a p-type GaN guide layer 8, a SiO2 blocking layer 9, an Ni / ITO cladding layer electrode 10 as a transparent electrode, a Ti / Au pad electrode 11, and a Ti / Al / Ni / Au electrode 12. The SiO2 blocking layer 9 is formed above the InGaN multiple quantum well active layer 5 so as to have an opening. The Ni / ITO cladding layer electrode 10 is formed inside the opening, and which is transparent for the light from the InGaN multiple quantum well active layer, and serves as a cladding layer.

Owner:PANASONIC CORP

Electronic apparatus having a protective circuit

A semiconductor display device with an interlayer insulating film in which surface levelness is ensured with a limited film formation time, heat treatment for removing moisture does not take long, and moisture in the interlayer insulating film is prevented from escaping into a film or electrode adjacent to the interlayer insulating film. A TFT is formed and then a nitrogen-containing inorganic insulating film that transmits less moisture compared to organic resin film is formed so as to cover the TFT. Next, organic resin including photosensitive acrylic resin is applied and an opening is formed by partially exposing the organic resin film to light. The organic resin film where the opening is formed, is then covered with a nitrogen-containing inorganic insulating film which transmits less moisture than organic resin film does. Thereafter, the gate insulating film and the two layers of the nitrogen-containing inorganic insulating films are partially etched away in the opening of the organic resin film to expose the active layer of the TFT.

Owner:SEMICON ENERGY LAB CO LTD

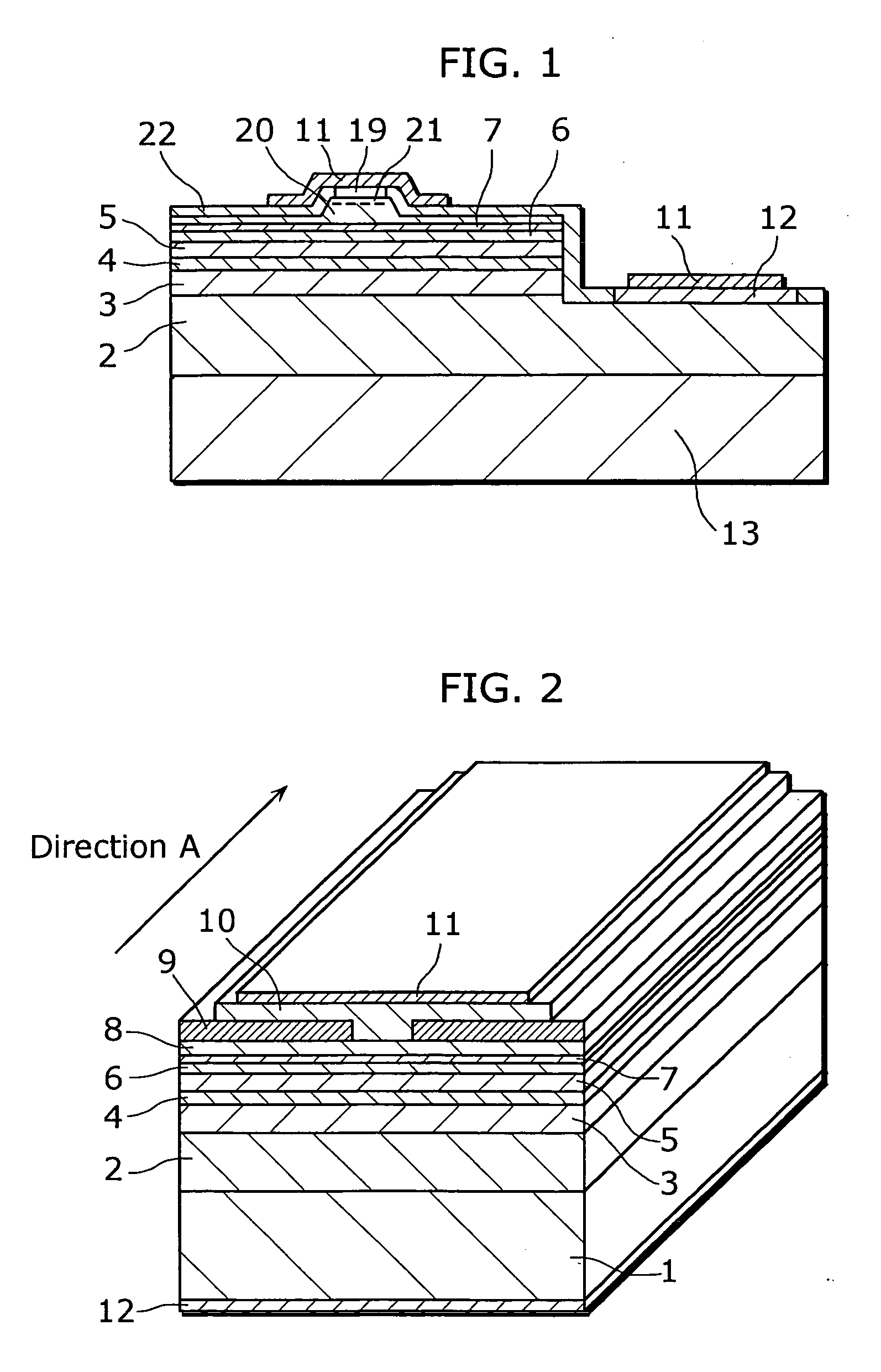

Organic light emitting diode display device and method of fabricating the same

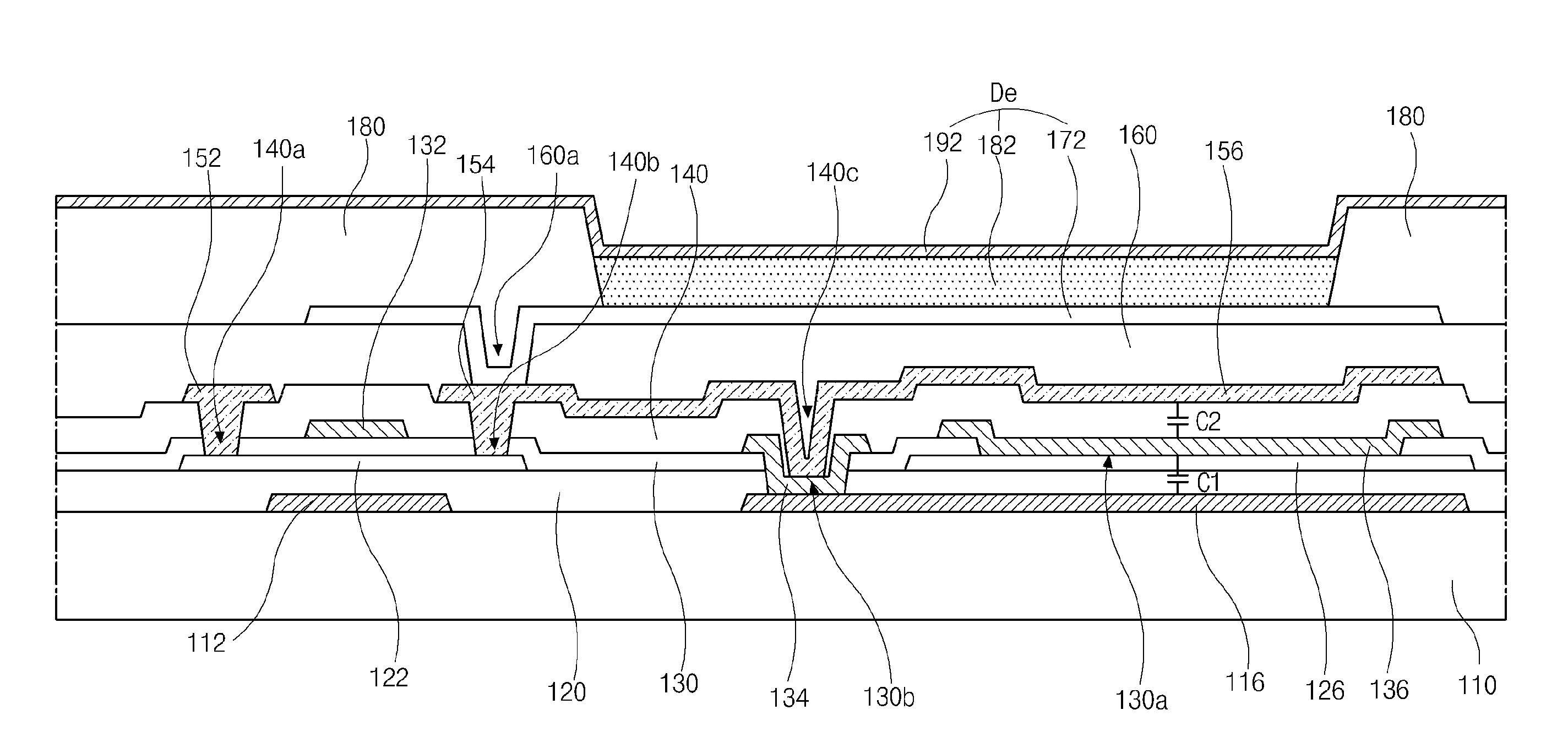

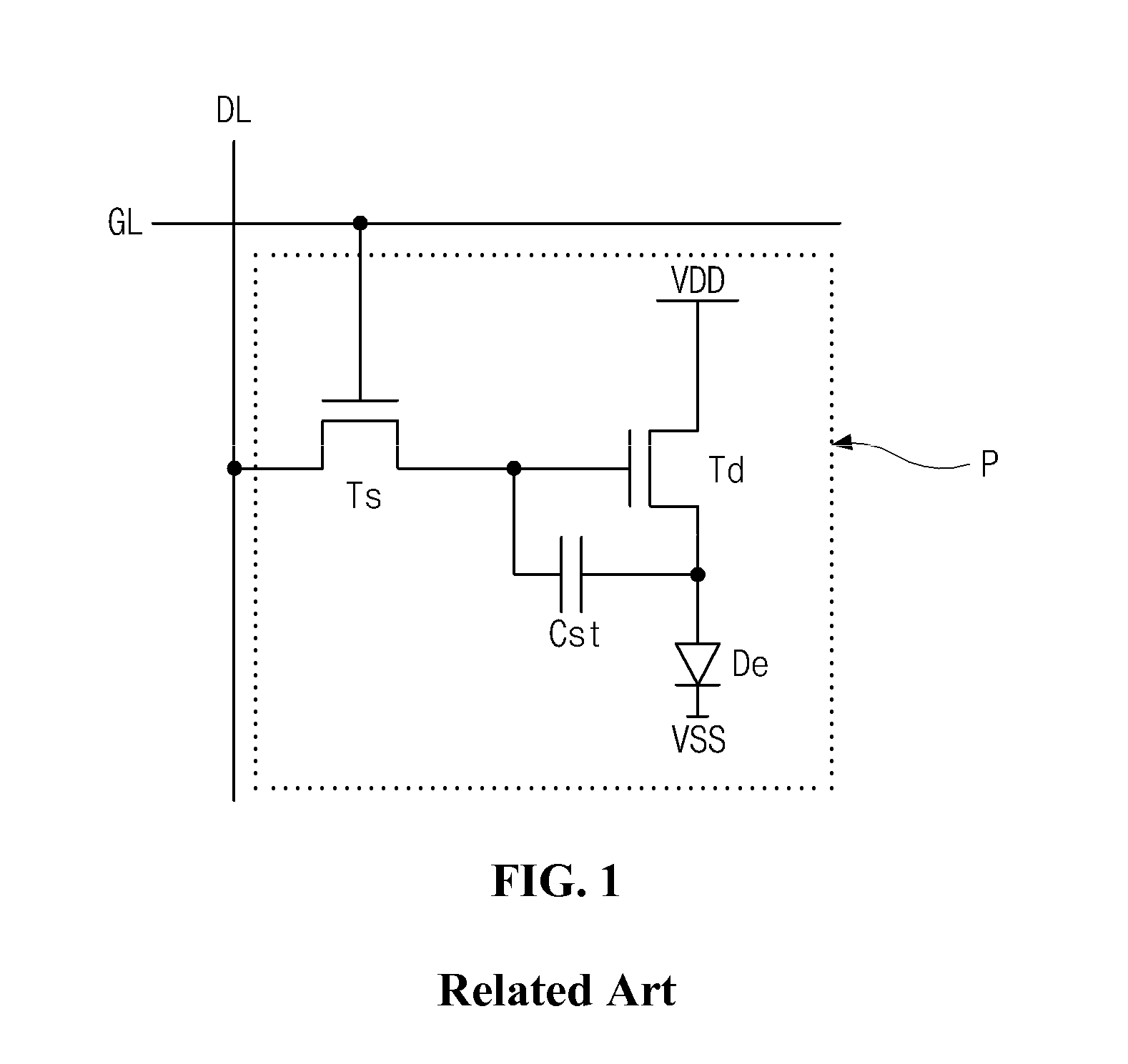

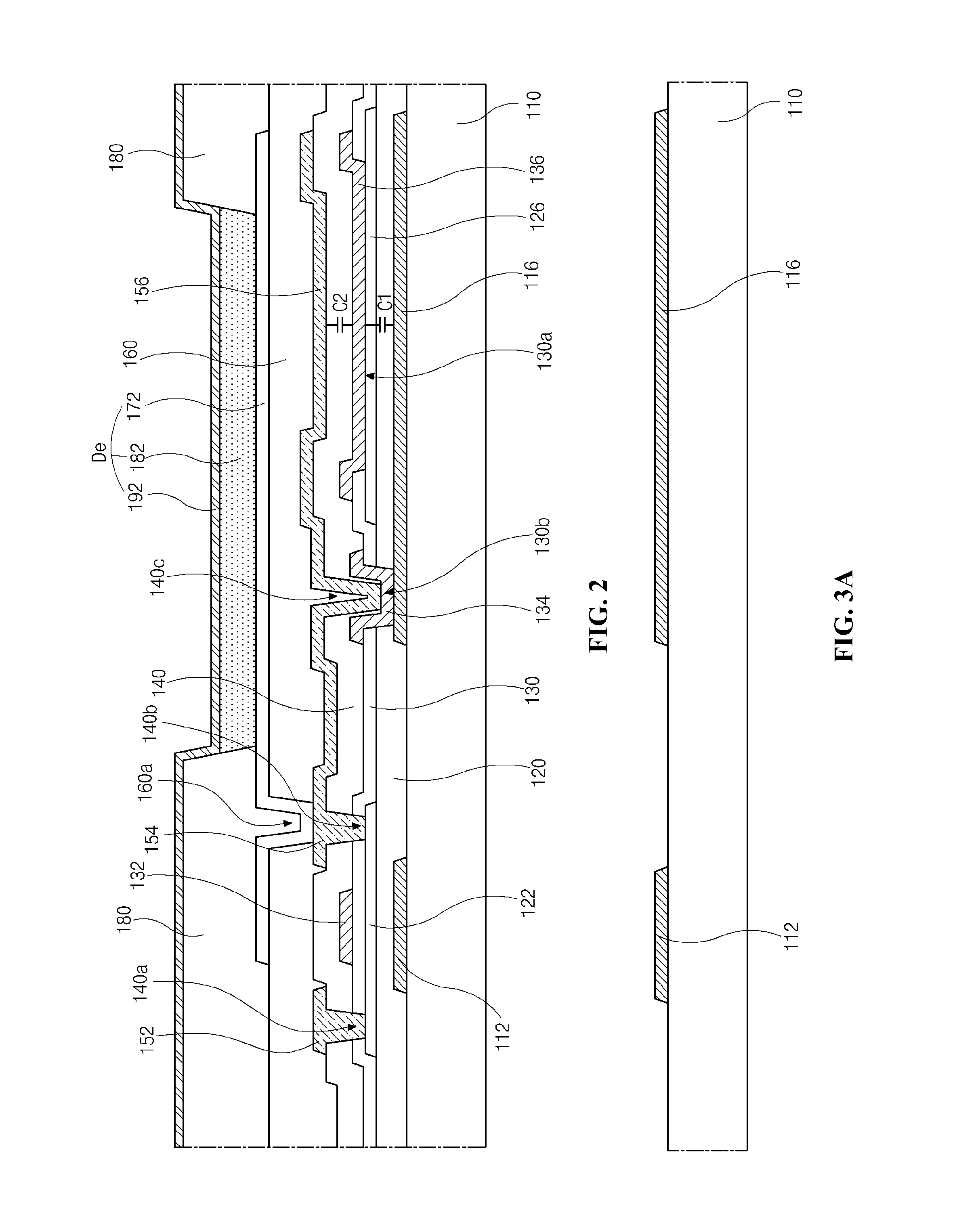

ActiveUS20150179724A1Increase capacitanceIncrease brightnessTransistorSolid-state devicesElectrical conductorDisplay device

An organic light emitting diode display device comprises a driving thin film transistor including a first semiconductor layer, a gate insulating layer formed on the first semiconductor layer. The device further includes a storage capacitor including a first capacitor electrode electrically coupled to a drain electrode of the driving thin film transistor, a buffer layer formed on the first capacitor electrode, a second semiconductor layer formed on the buffer layer, and a second capacitor electrode formed on the second semiconductor layer and electrically coupled to a gate electrode of the driving thin film transistor. The device also includes an organic light emitting diode connected to the drain electrode of the driving transistor. The gate insulating layer has at least one hole in a region where the gate insulating layer overlaps the second semiconductor layer, thereby exposing the second semiconductor layer to the second capacitor electrode.

Owner:LG DISPLAY CO LTD

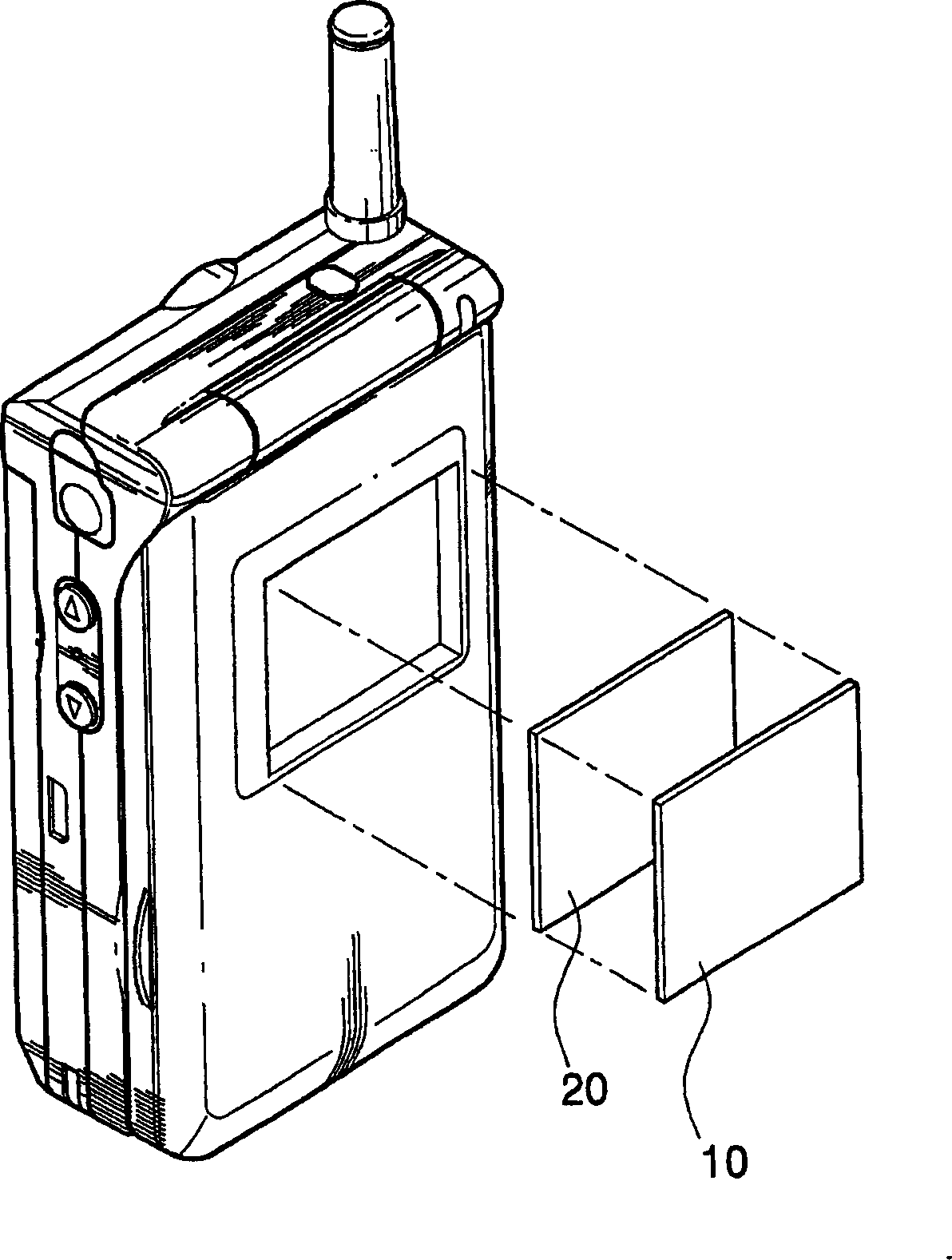

Liquid crystal display device built-in finger printing device and method of manufacturing the same

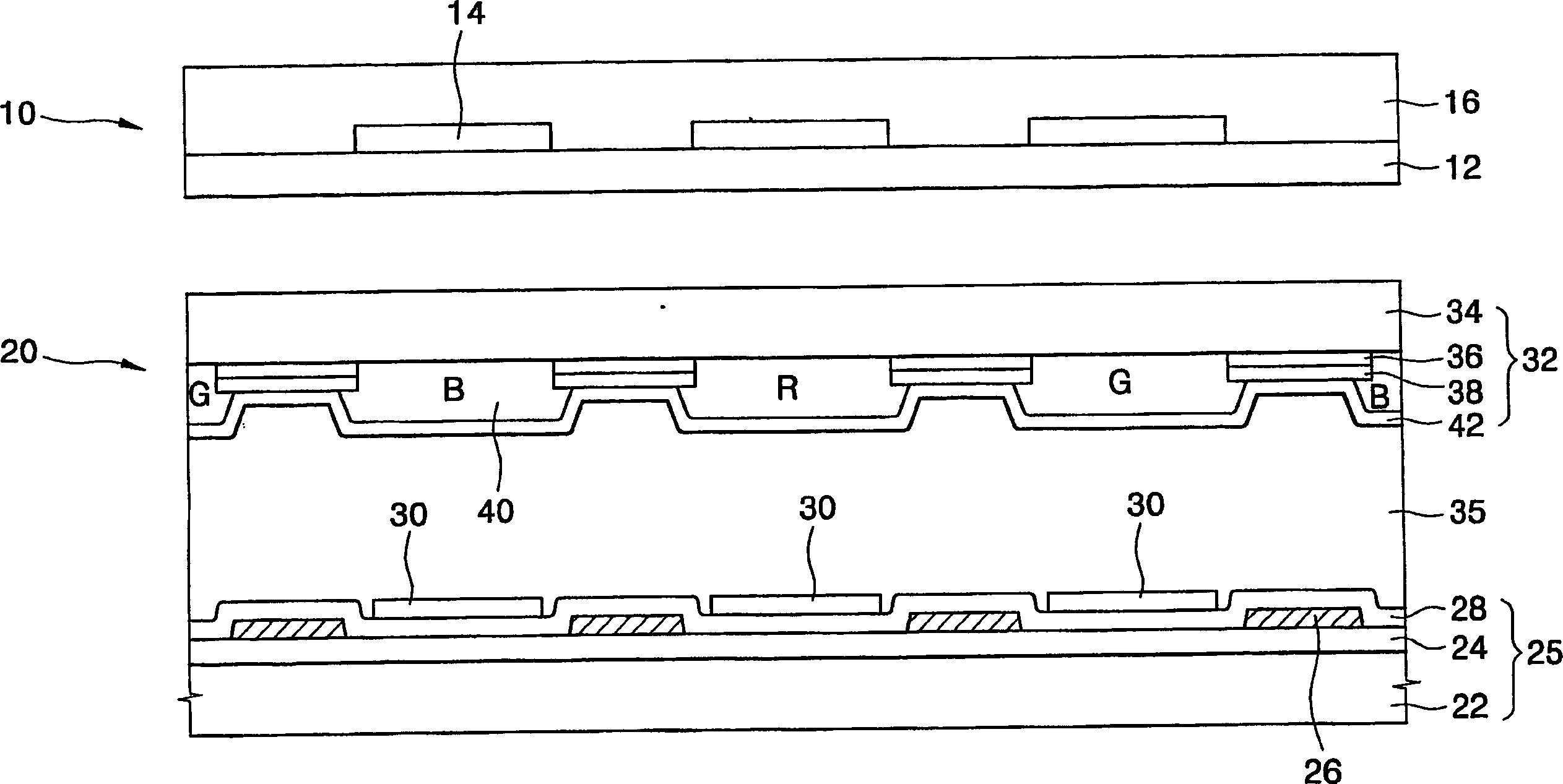

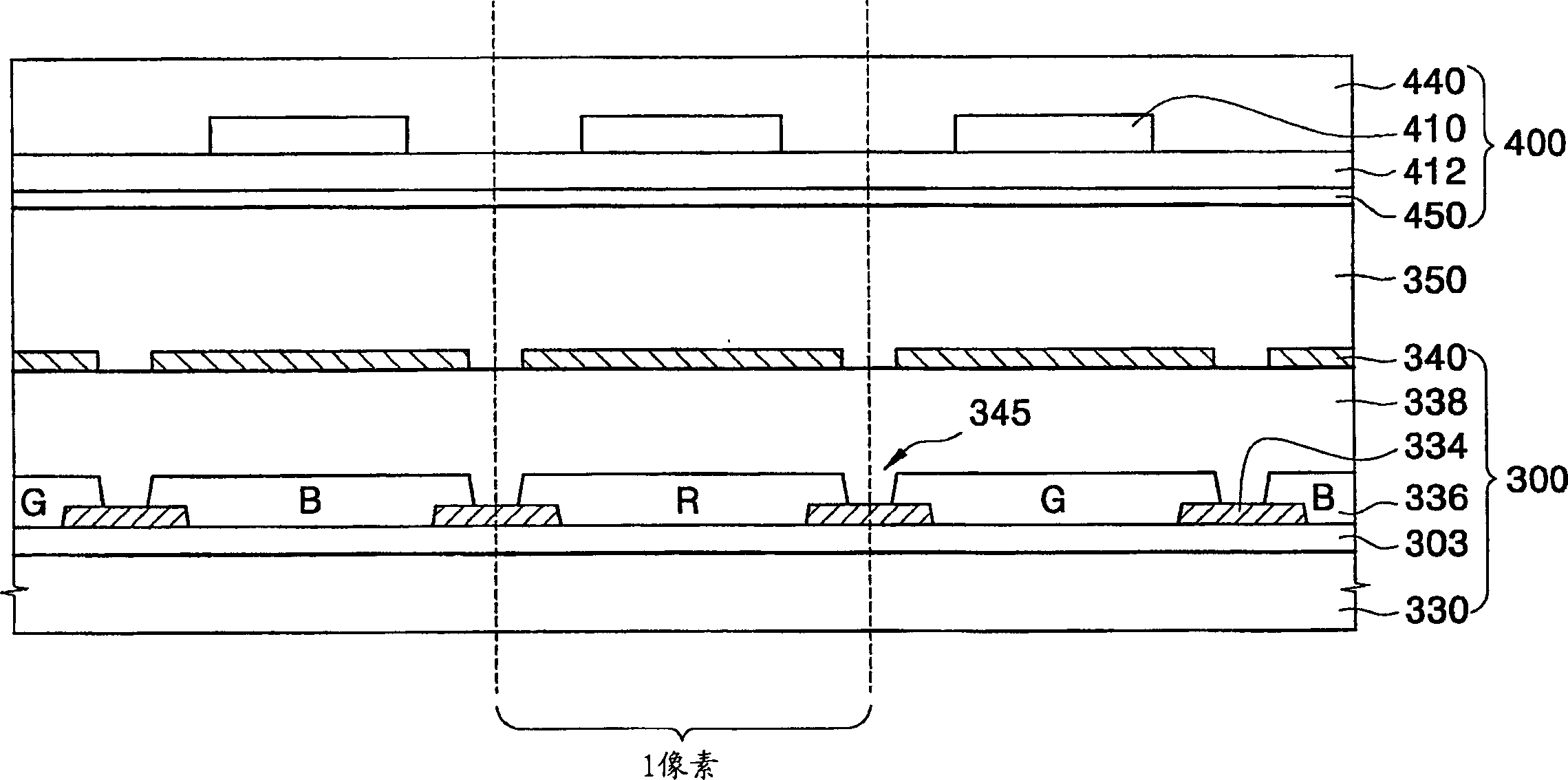

InactiveCN1689025AReduce in quantityReduce thicknessStatic indicating devicesPrint image acquisitionColor gelTransmittance

A liquid crystal display device having fingerprint identification device for enhancing aperture ratio and transmissivity of a TFT-LCD panel is disclosed. A fingerprint identification substrate (400) is attached to a TFT substrate (300). The TFT substrate has color-filter-on-array structure in which the color filters (336) and the thin film transistors can be eliminated, the aperture ratio is increased, and the quality of image display is enhanced. In addition, the transmissivity is increased according to the decrease of the number of glass substrate used in the liquid crystal display device, so that the sensitivity of fingerprint identification is enhanced.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor display device and method of manufacturing the same

InactiveUS20050233507A1Timely controlPrevent moistureTransistorSolid-state devicesAcrylic resinDisplay device

A semiconductor display device with an interlayer insulating film in which surface levelness is ensured with a limited film formation time, heat treatment for removing moisture does not take long, and moisture in the interlayer insulating film is prevented from escaping into a film or electrode adjacent to the interlayer insulating film. A TFT is formed and then a nitrogen-containing inorganic insulating film that transmits less moisture compared to organic resin film is formed so as to cover the TFT. Next, organic resin including photosensitive acrylic resin is applied and an opening is formed by partially exposing the organic resin film to light. The organic resin film where the opening is formed, is then. covered with a nitrogen-containing inorganic insulating film which transmits less moisture than organic resin film does. Thereafter, the gate insulating film and the two layers of the nitrogen-containing inorganic insulating films are partially etched away in the opening of the organic resin film to expose the active layer of the TFT.

Owner:SEMICON ENERGY LAB CO LTD

Mesa-shaped piezoelectric resonator element

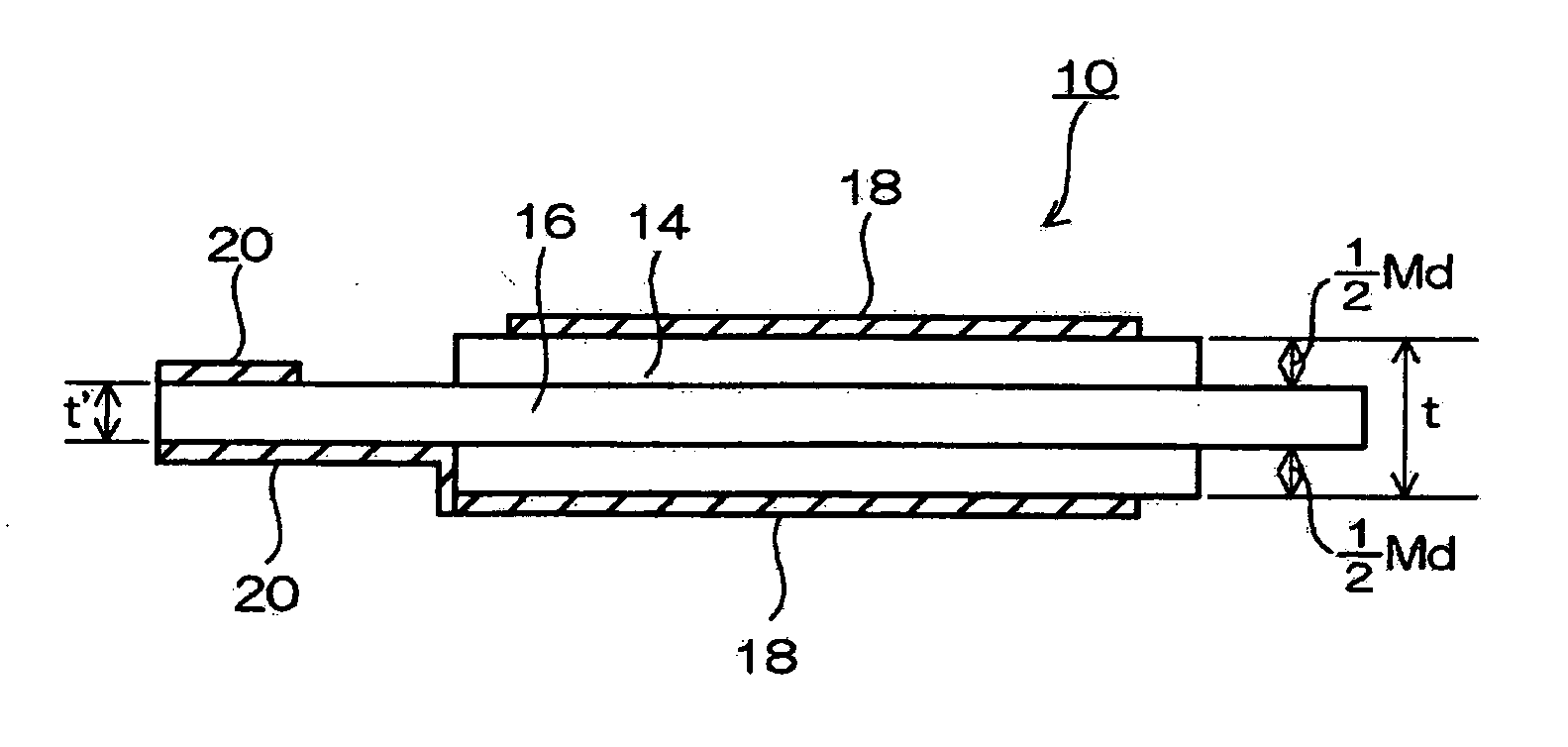

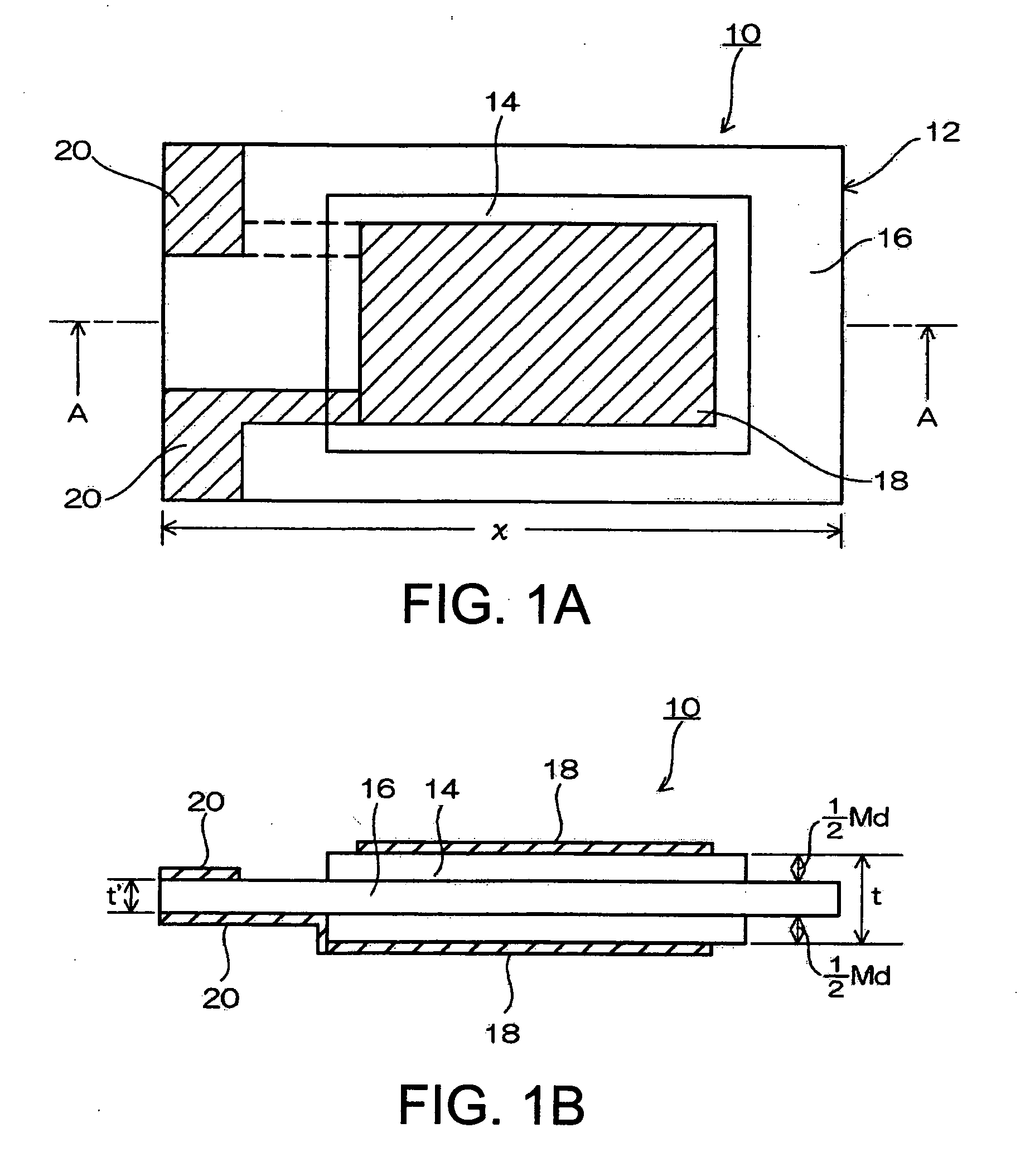

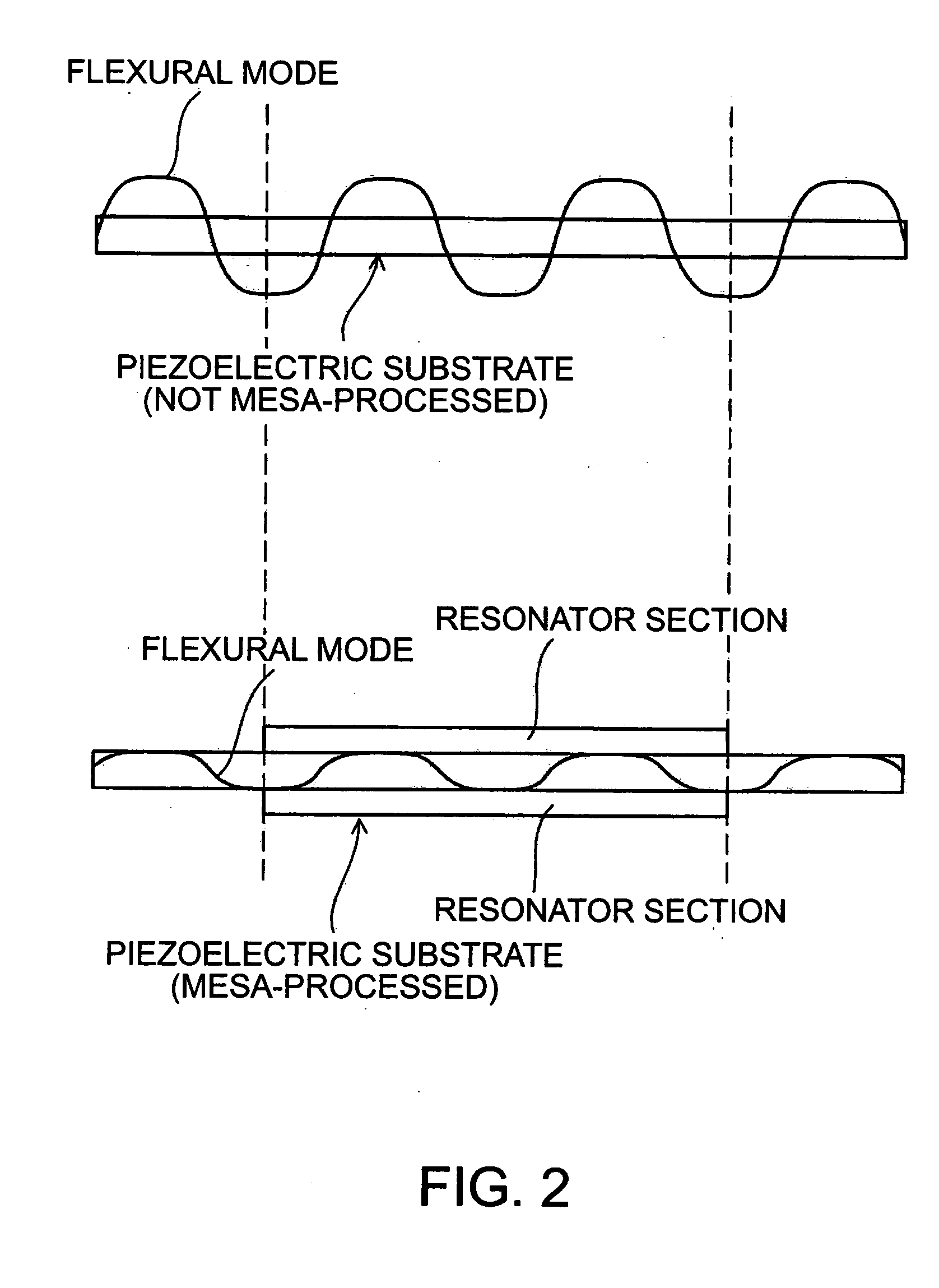

ActiveUS20070096596A1Small sizeIncreasing the thicknessPiezoelectric/electrostriction/magnetostriction machinesImpedence networksPiezoelectric resonatorsPhysics

A mesa-shaped piezoelectric resonator element including a resonator section having a thicker thickness than a peripheral section on the board surface of a piezoelectric substrate formed in a rectangular shape, wherein, when the length of the long side of the piezoelectric substrate is x and the board thickness of the resonator section is t, etching depth y of a level-difference section is set to fulfill a relationship in the following equation, based on the board thickness t. y=-1.32×(xt)+43±5(%)

Owner:SEIKO EPSON CORP

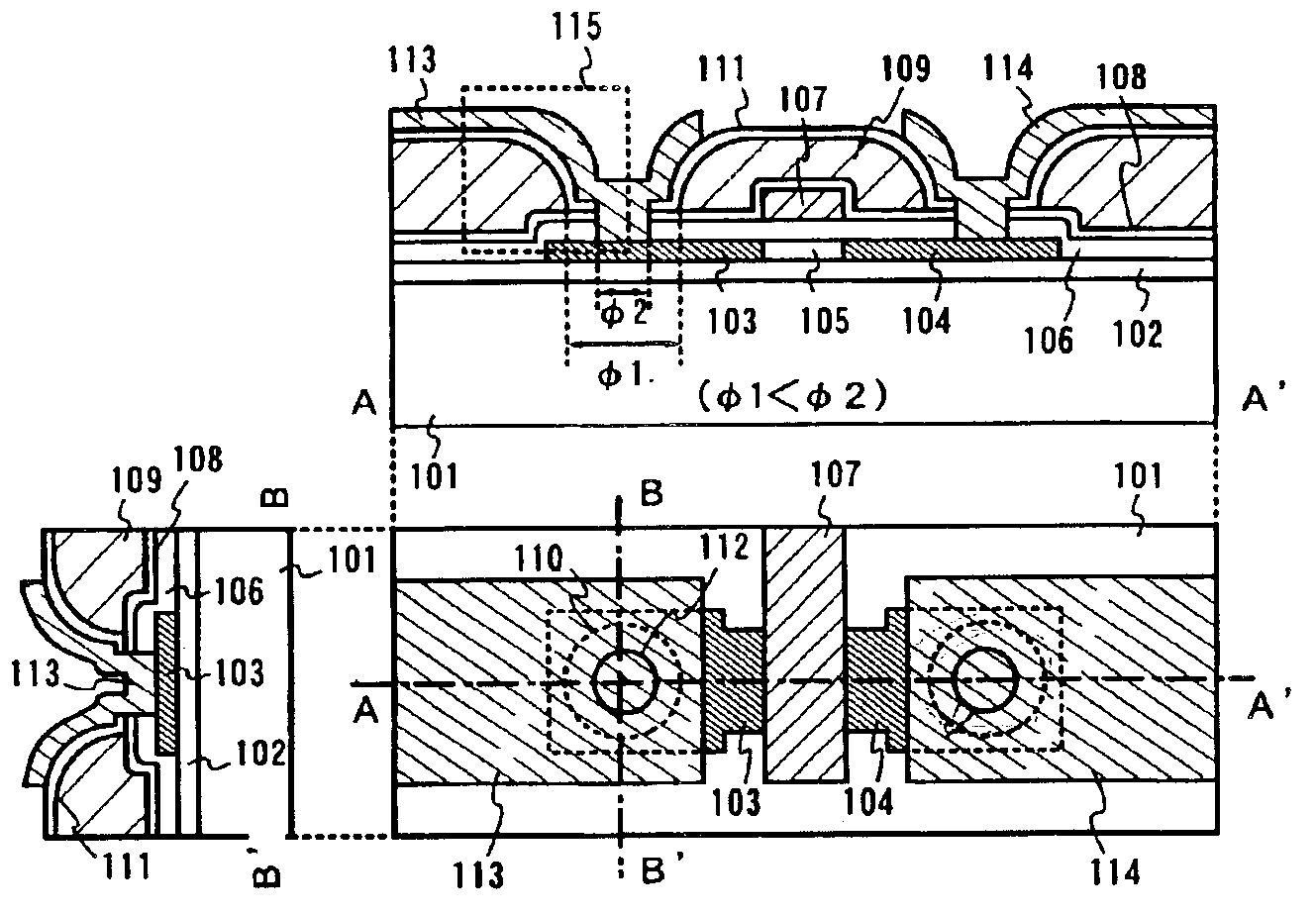

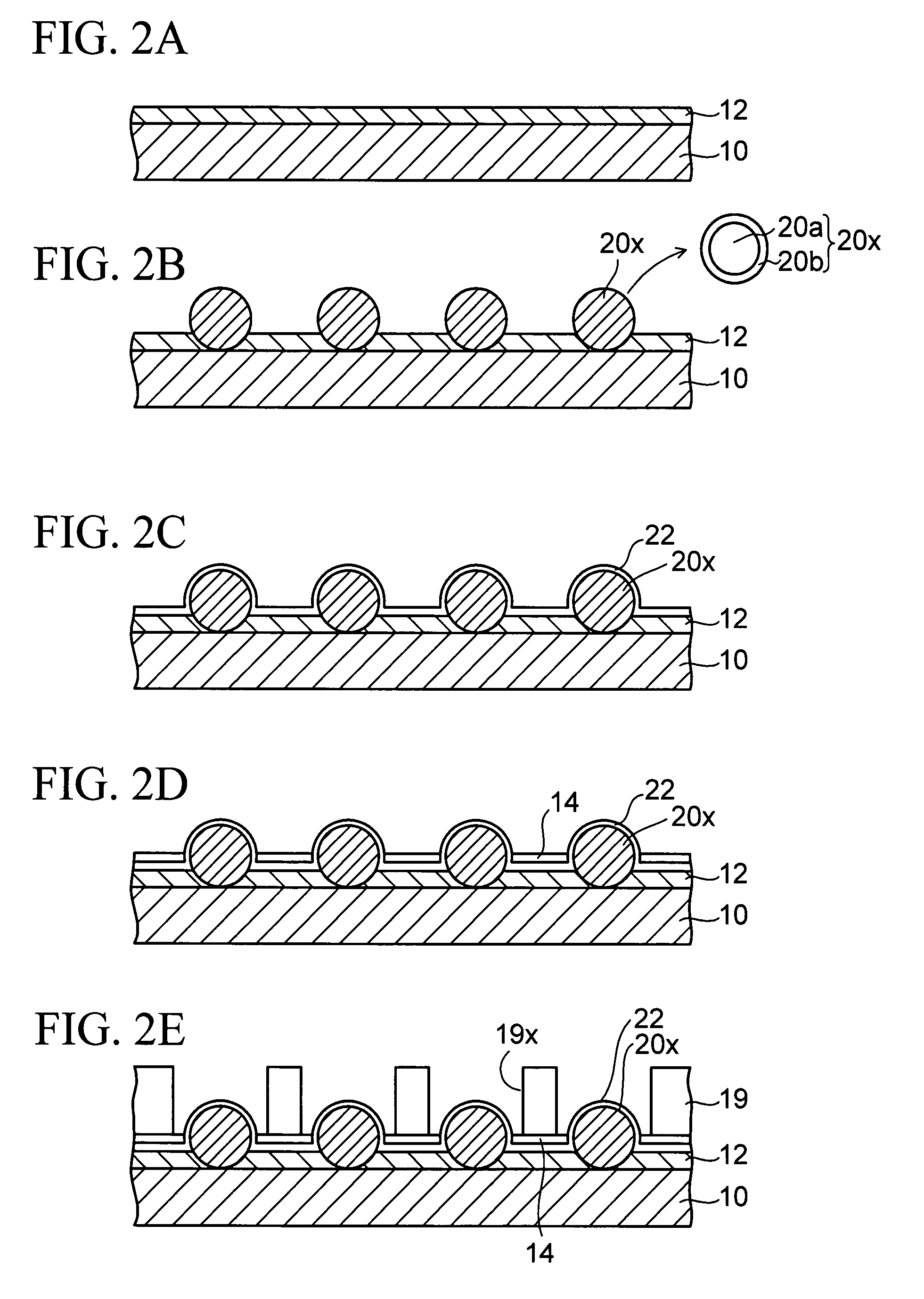

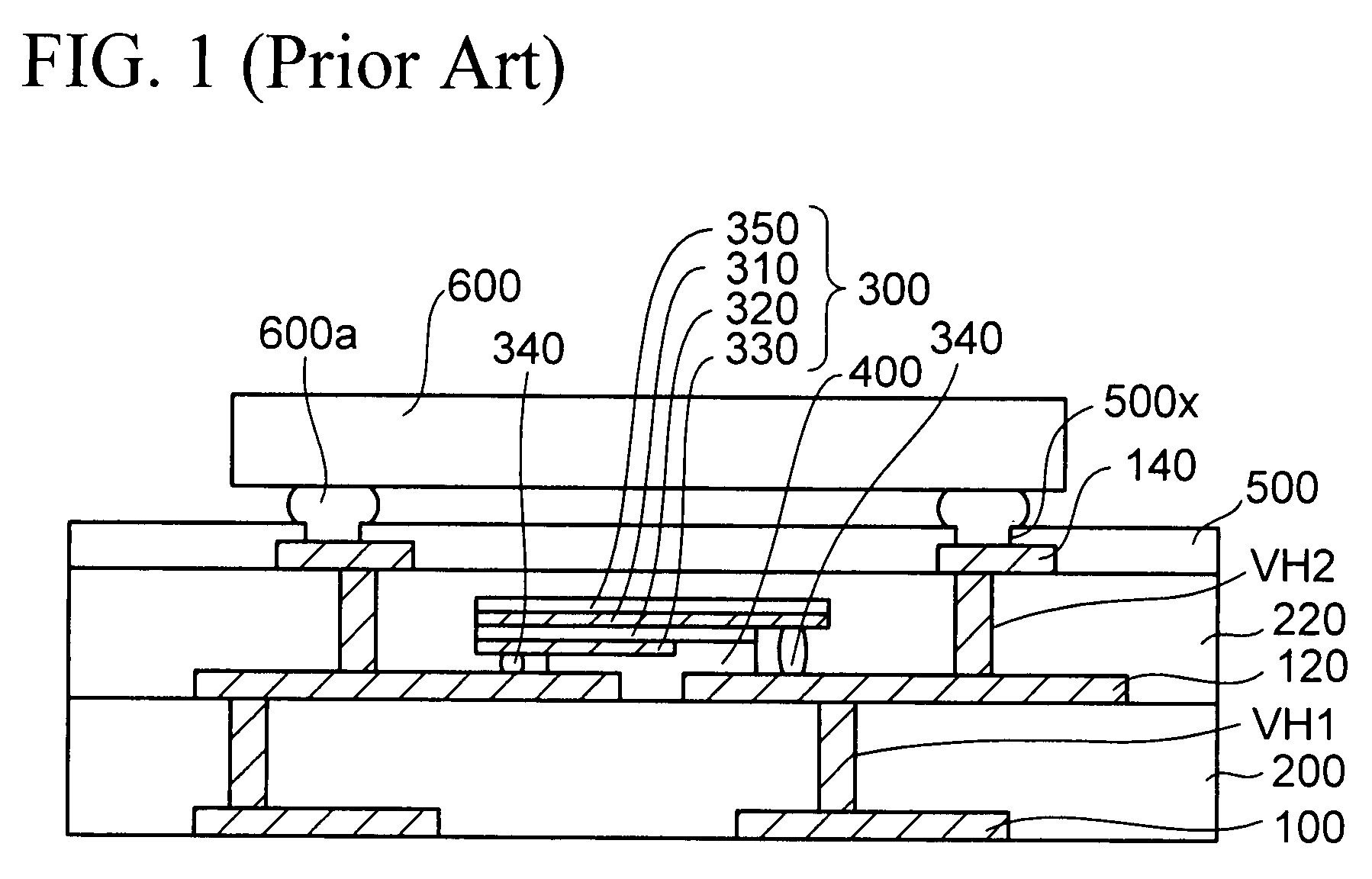

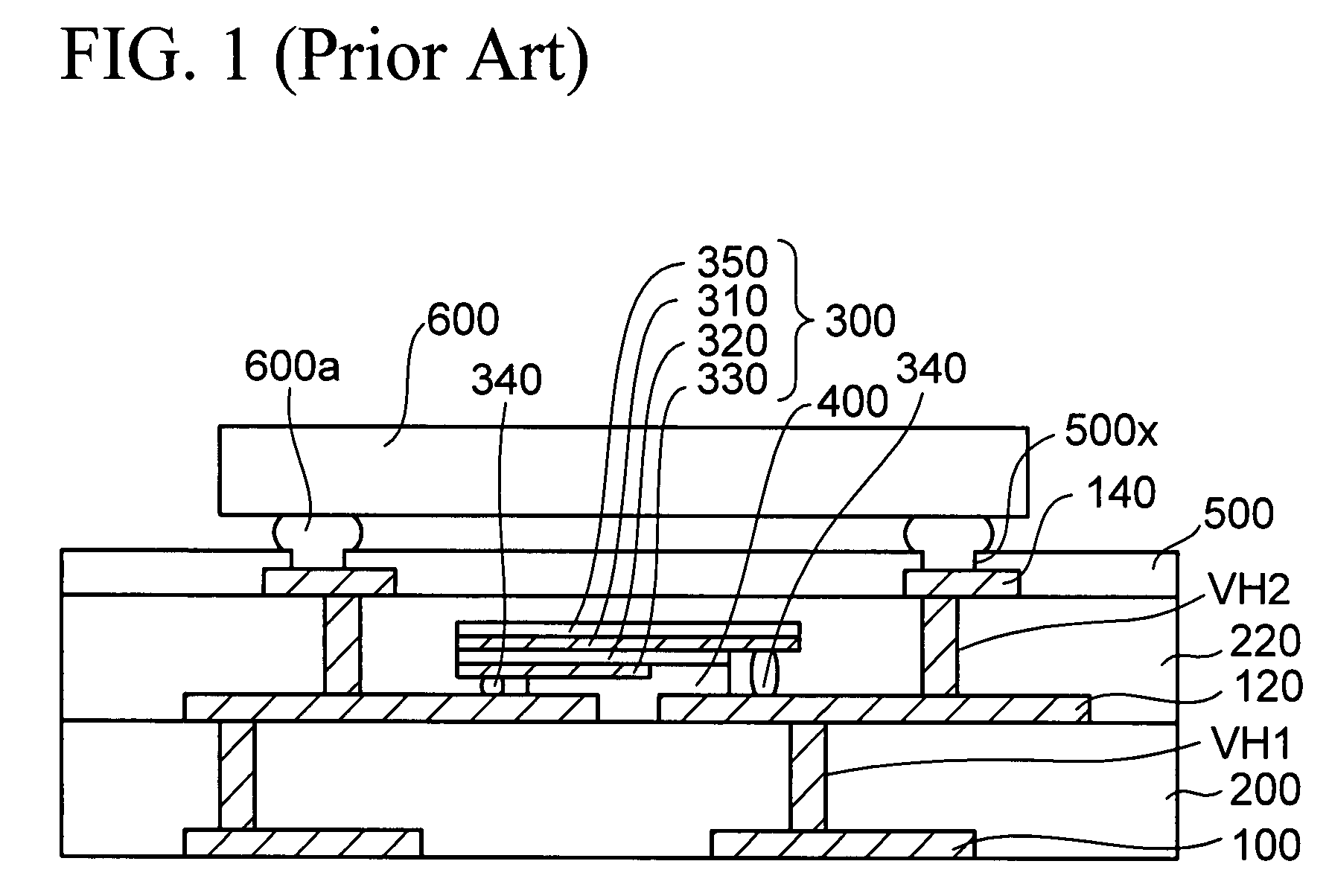

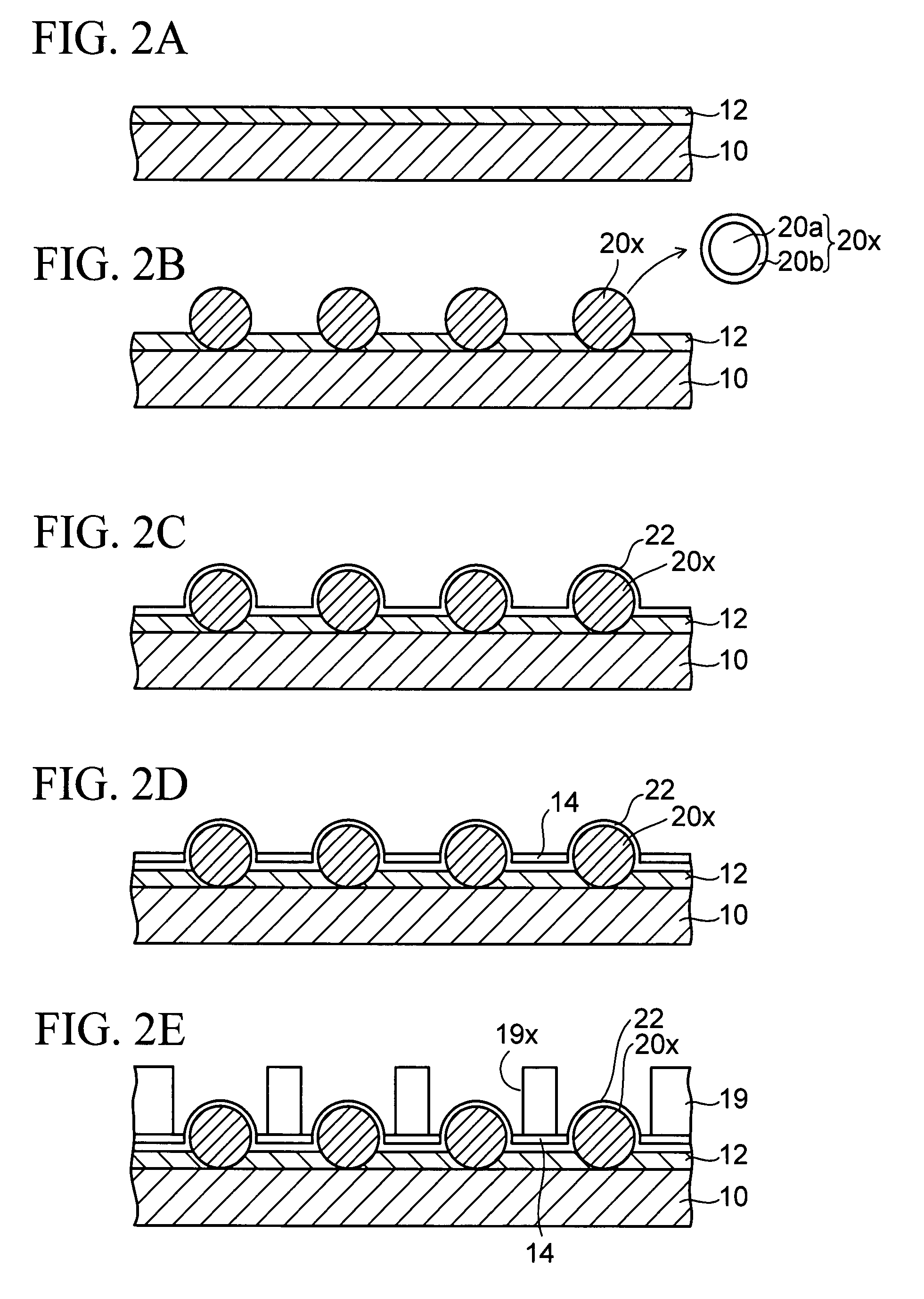

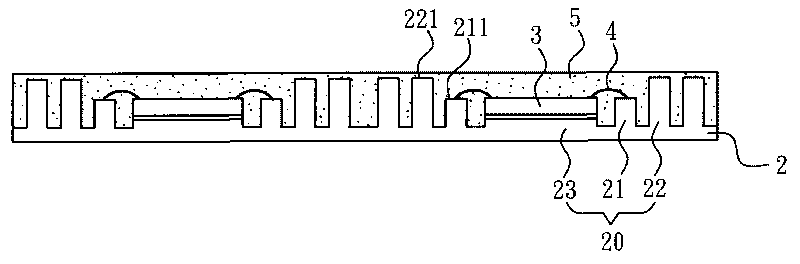

Display device and method of fabricating the same

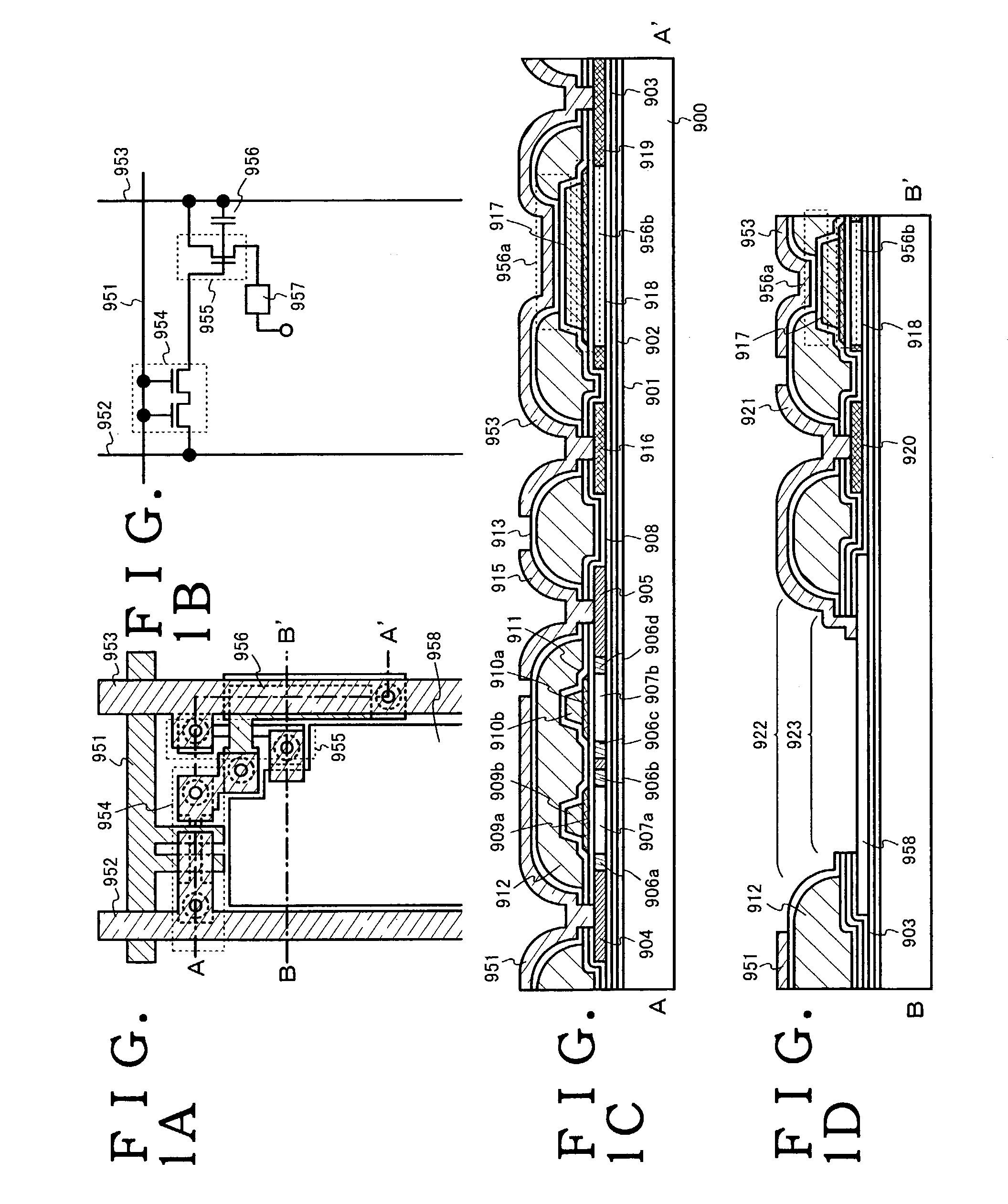

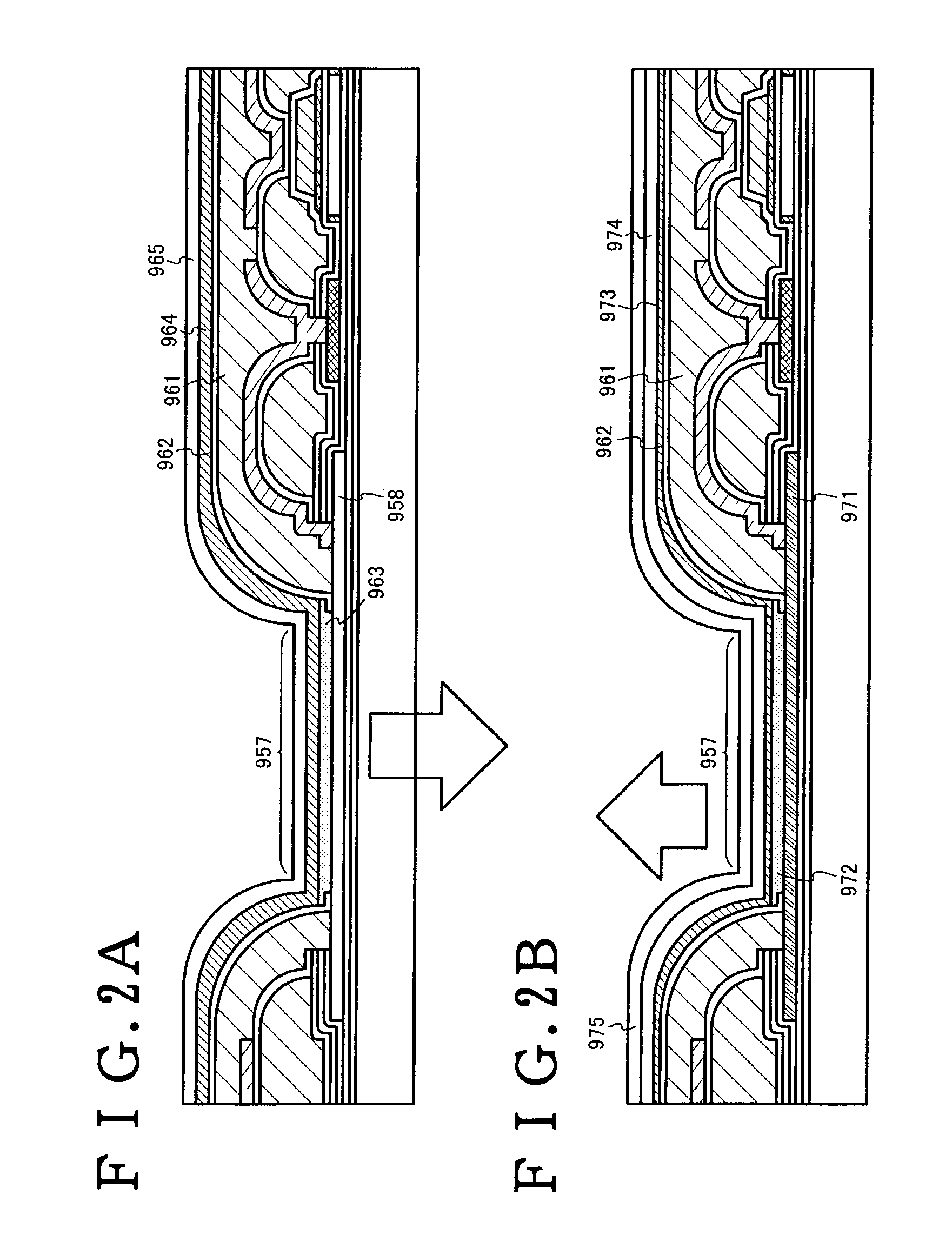

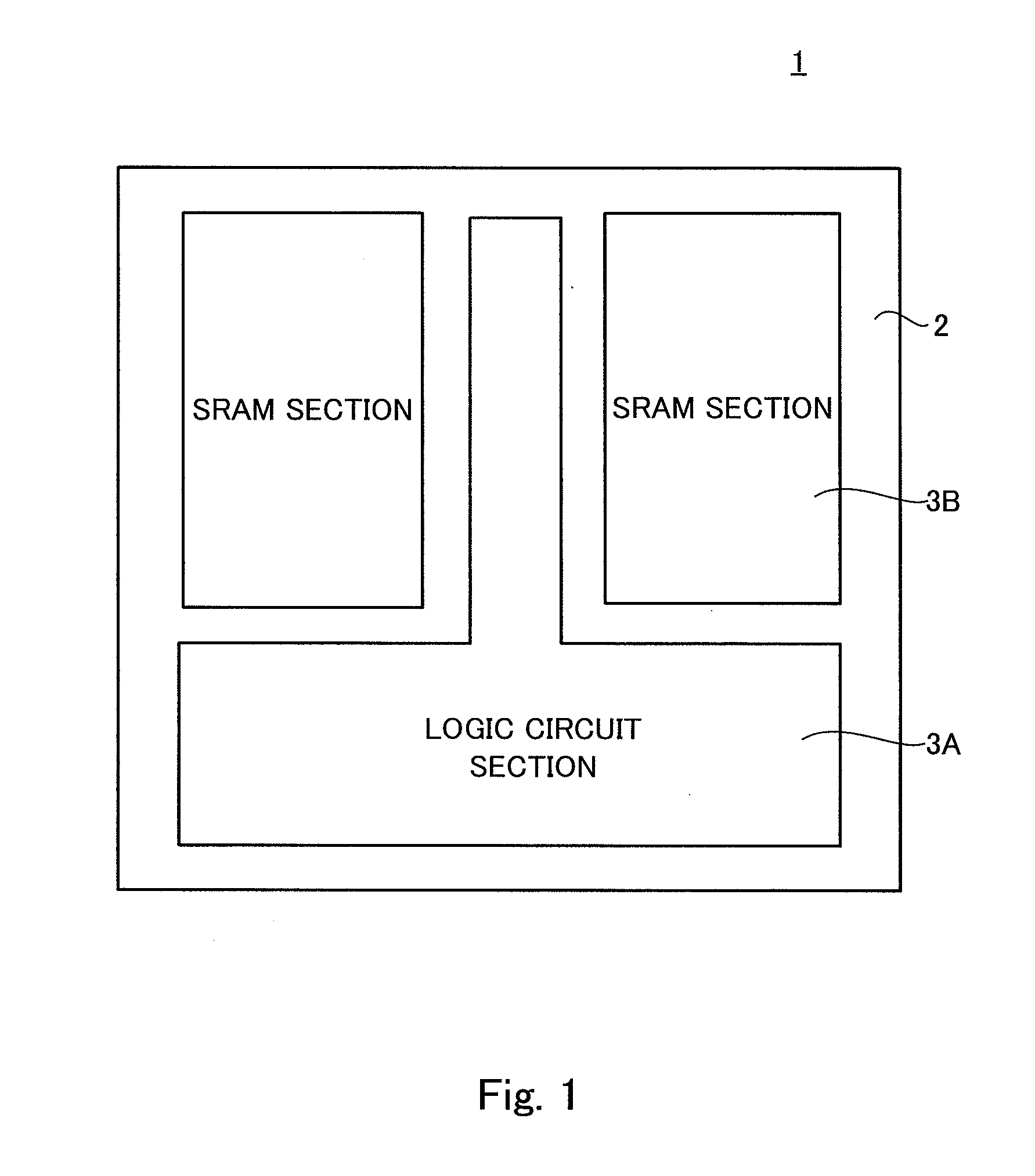

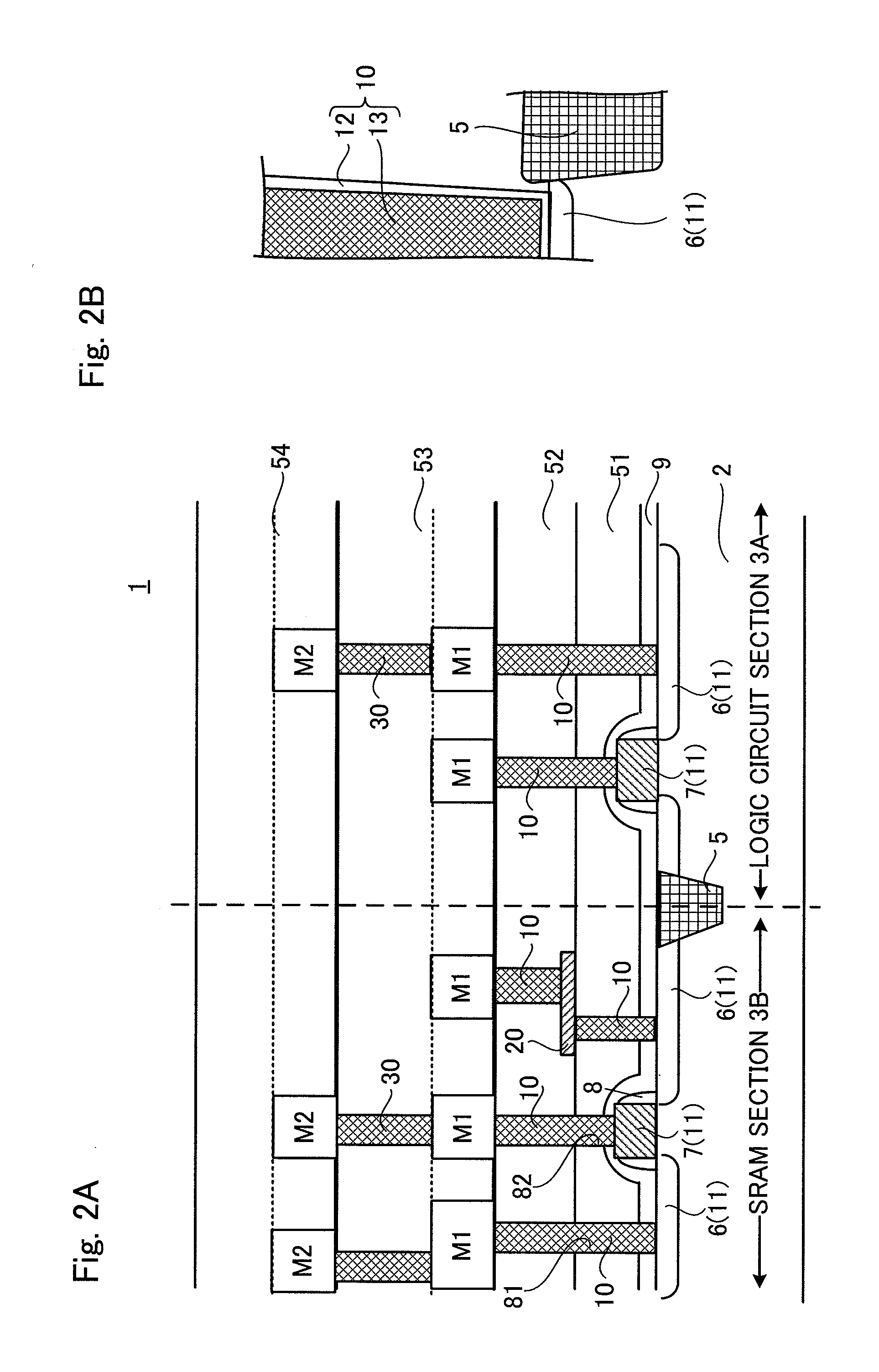

InactiveUS7411215B2Fabrication process can be shortenedReduce manufacturing costTransistorElectroluminescent light sourcesDisplay deviceEngineering

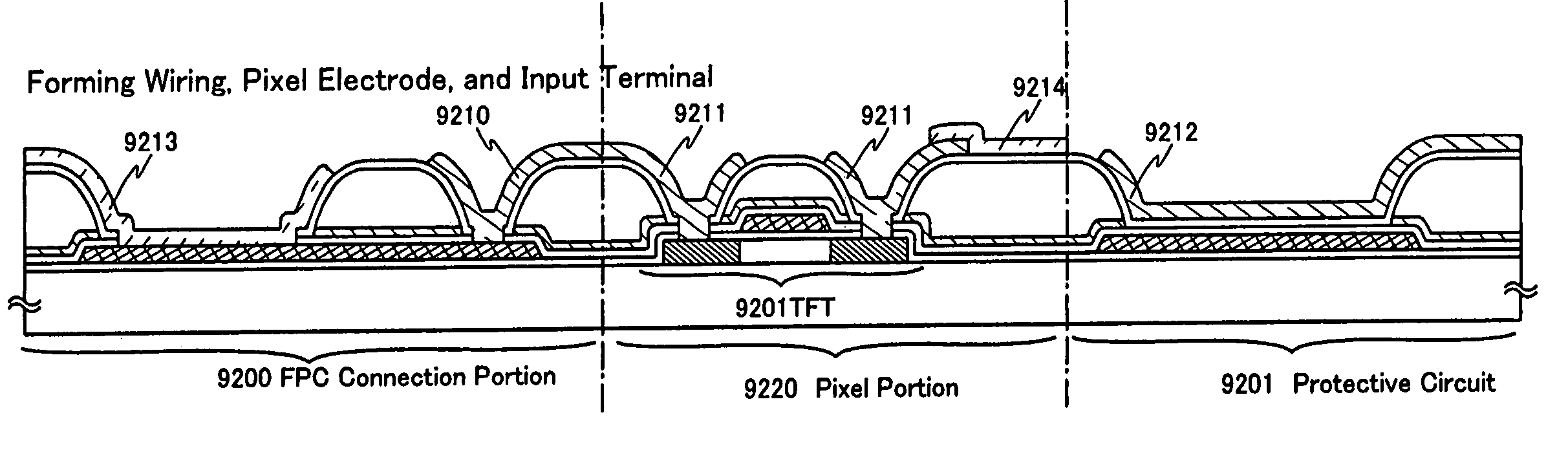

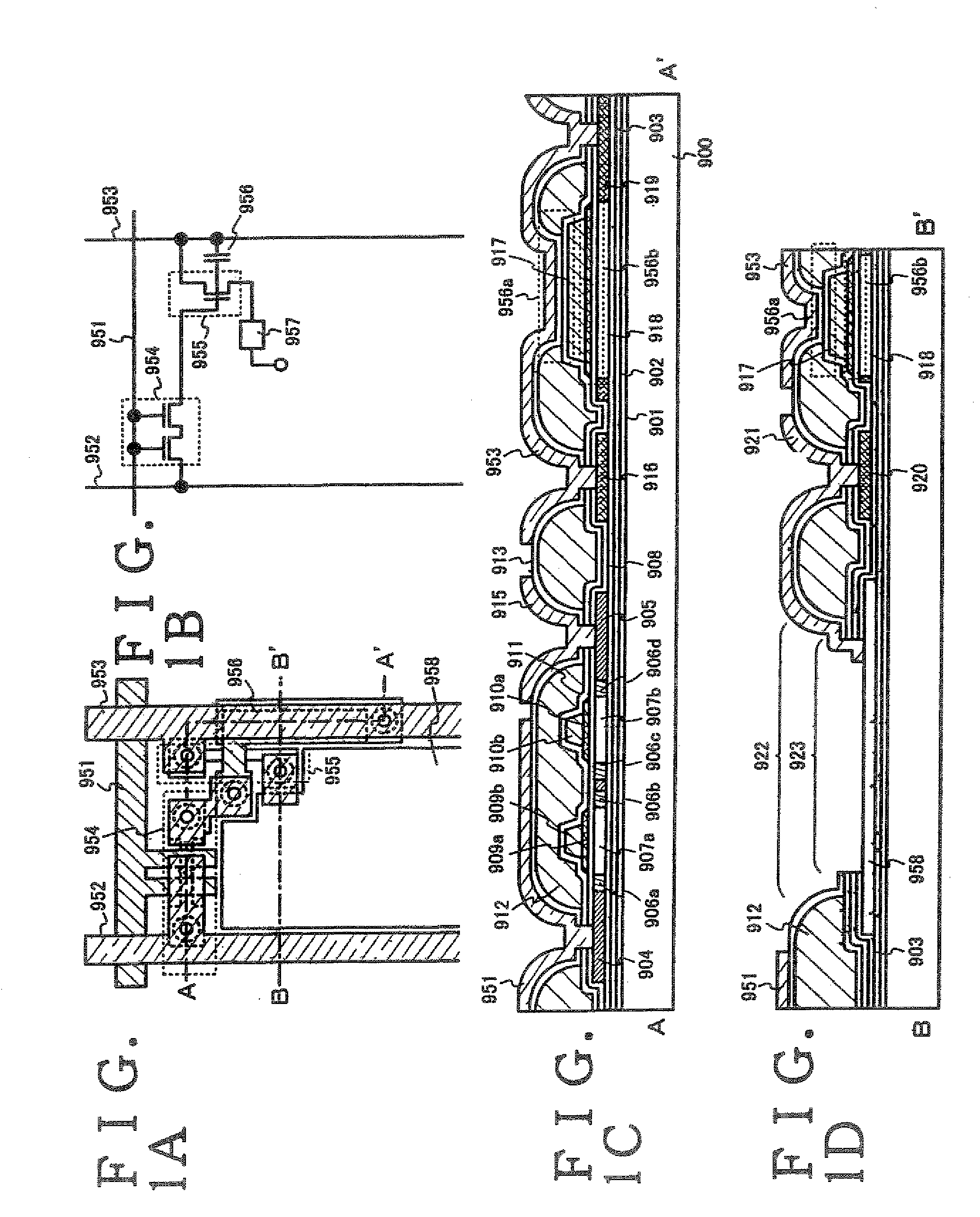

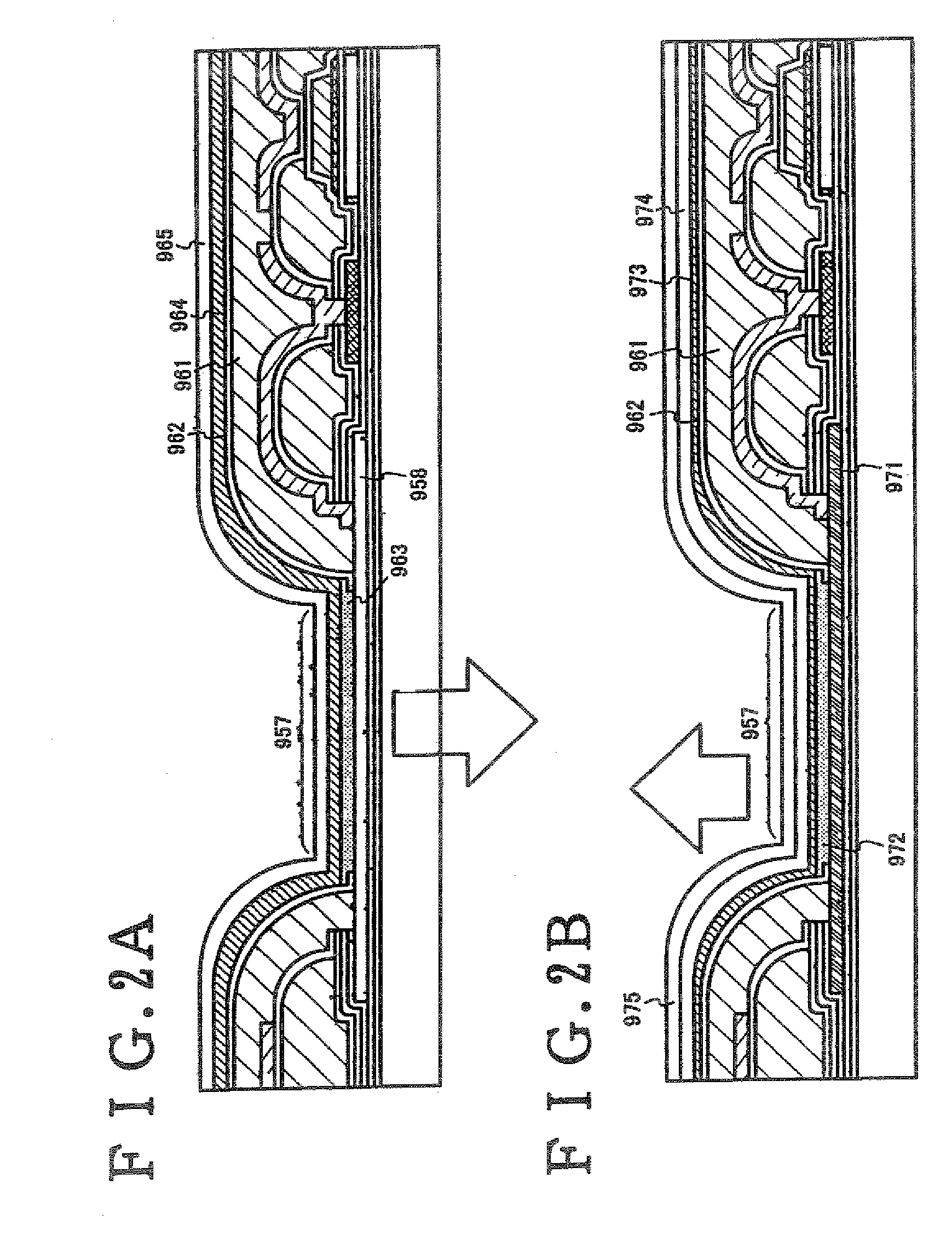

To achieve promotion of stability of operational function of display device and enlargement of design margin in circuit design, in a display device including a pixel portion having a semiconductor element and a plurality of pixels provided with pixel electrodes connected to the semiconductor element on a substrate, the semiconductor element includes a photosensitive organic resin film as an interlayer insulating film, an inner wall face of a first opening portion provided at the photosensitive organic resin film is covered by a second insulating nitride film, a second opening portion provided at an inorganic insulating film is provided on an inner side of the first opening portion, the semiconductor and a wiring are connected through the first opening portion and the second opening portion and the pixel electrode is provided at a layer on a lower side of an activation layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor laser device and manufacturing method thereof

ActiveUS20080008220A1Sufficient epitaxial growth-rateSignificant growthOptical wave guidanceLaser detailsActive layerSilicon dioxide

It is an object of the present invention to provide a semiconductor laser device with high-yielding in which a clack generated in an epitaxial growth layer is restrained and to the manufacturing method thereof, the semiconductor laser device includes a GaN substrate 1, an n-type GaN layer 2, an n-type AlGaN cladding layer 3, a n-type GaN guide layer 4, an InGaN multiple quantum well active layer 5, an undoped-GaN guide layer 6, a p-type AlGaN electron overflow suppression layer 7, a p-type GaN guide layer 8, a SiO2 blocking layer 9, an Ni / ITO cladding layer electrode 10 as a transparent electrode, a Ti / Au pad electrode 11, and a Ti / Al / Ni / Au electrode 12. The SiO2 blocking layer 9 is formed above the InGaN multiple quantum well active layer 5 so as to have an opening. The Ni / ITO cladding layer electrode 10 is formed inside the opening, and which is transparent for the light from the InGaN multiple quantum well active layer, and serves as a cladding layer.

Owner:PANASONIC CORP

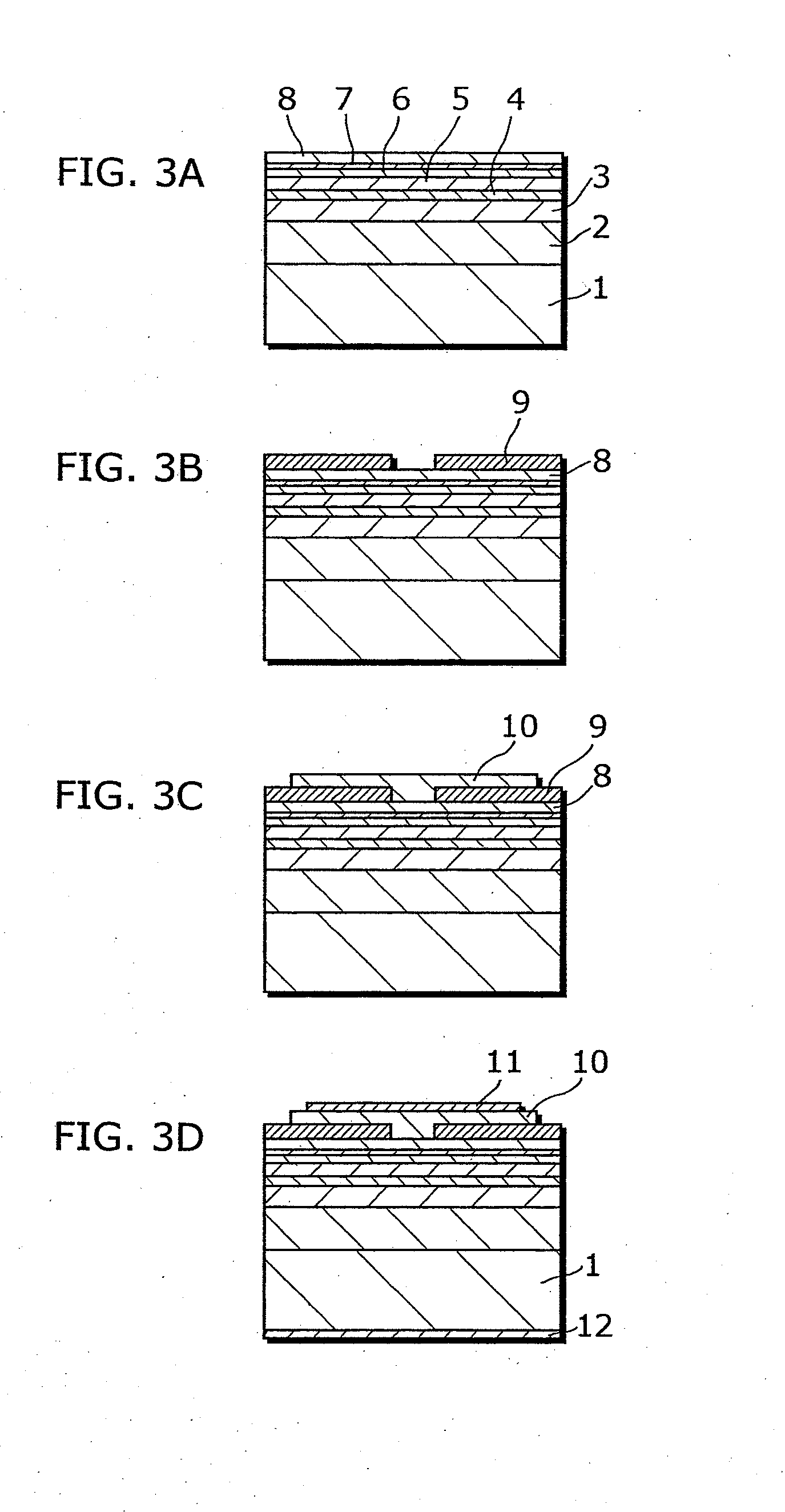

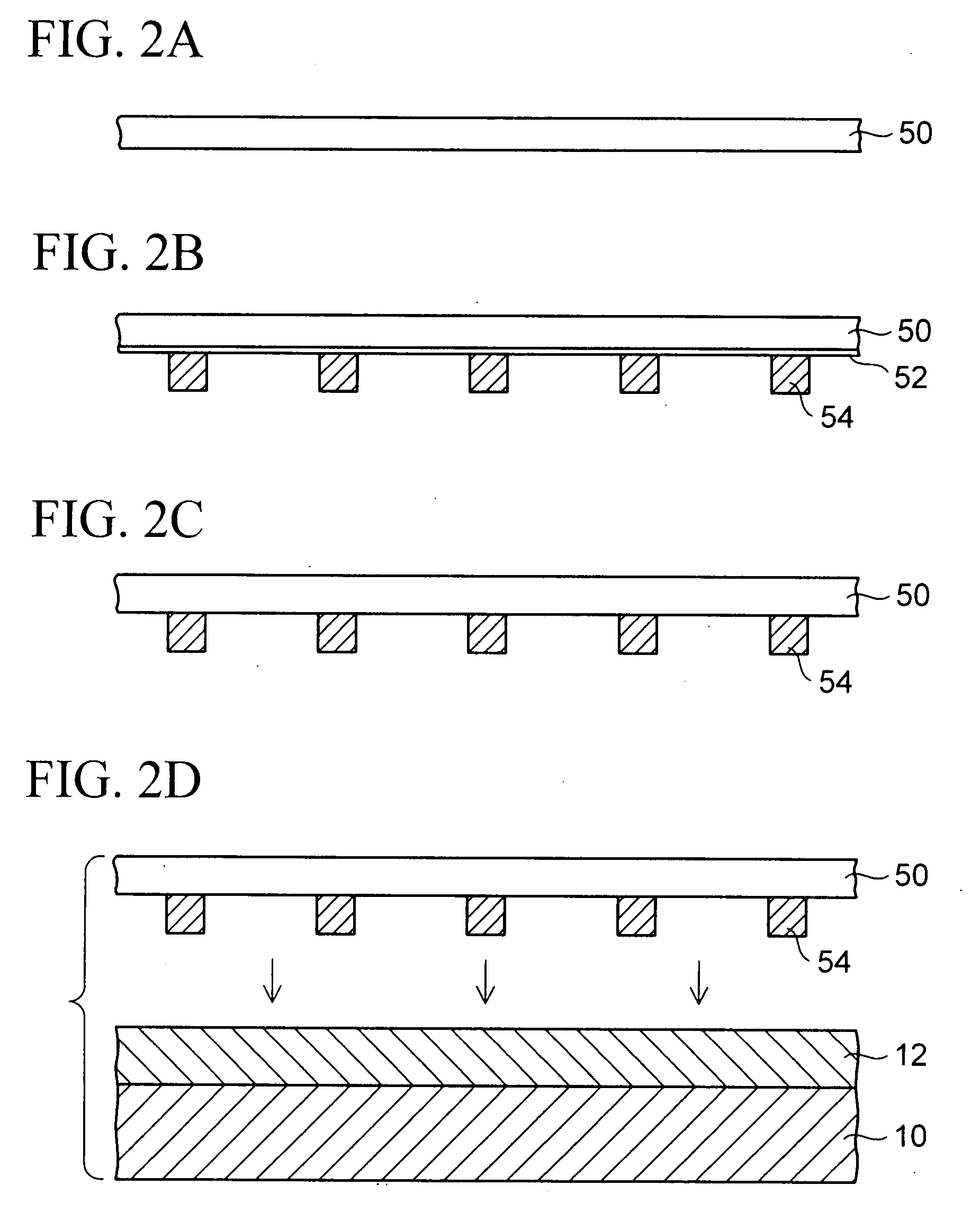

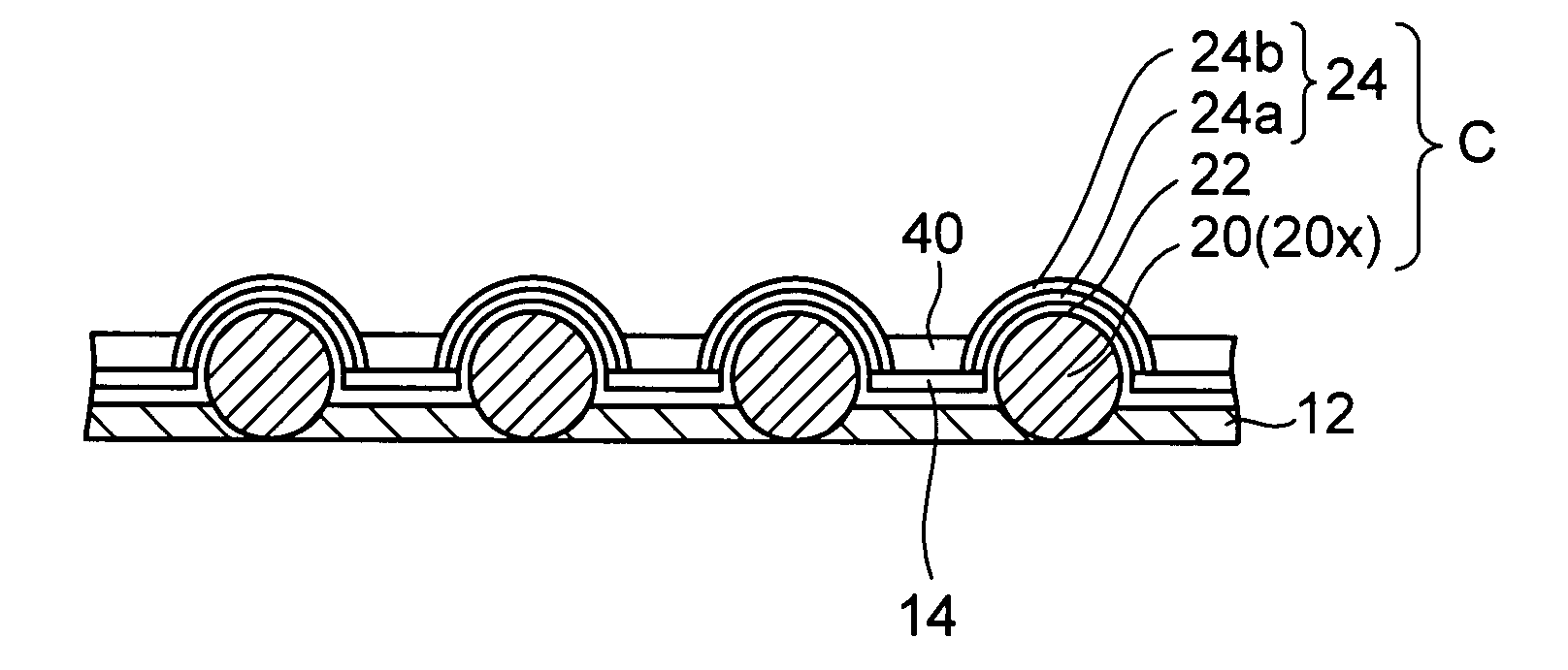

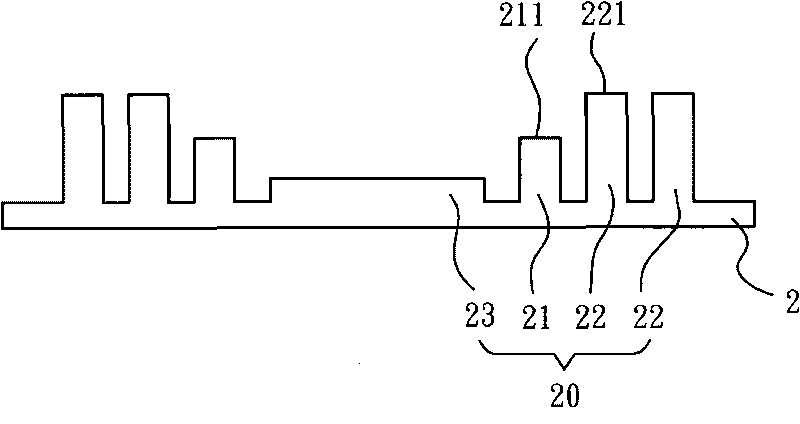

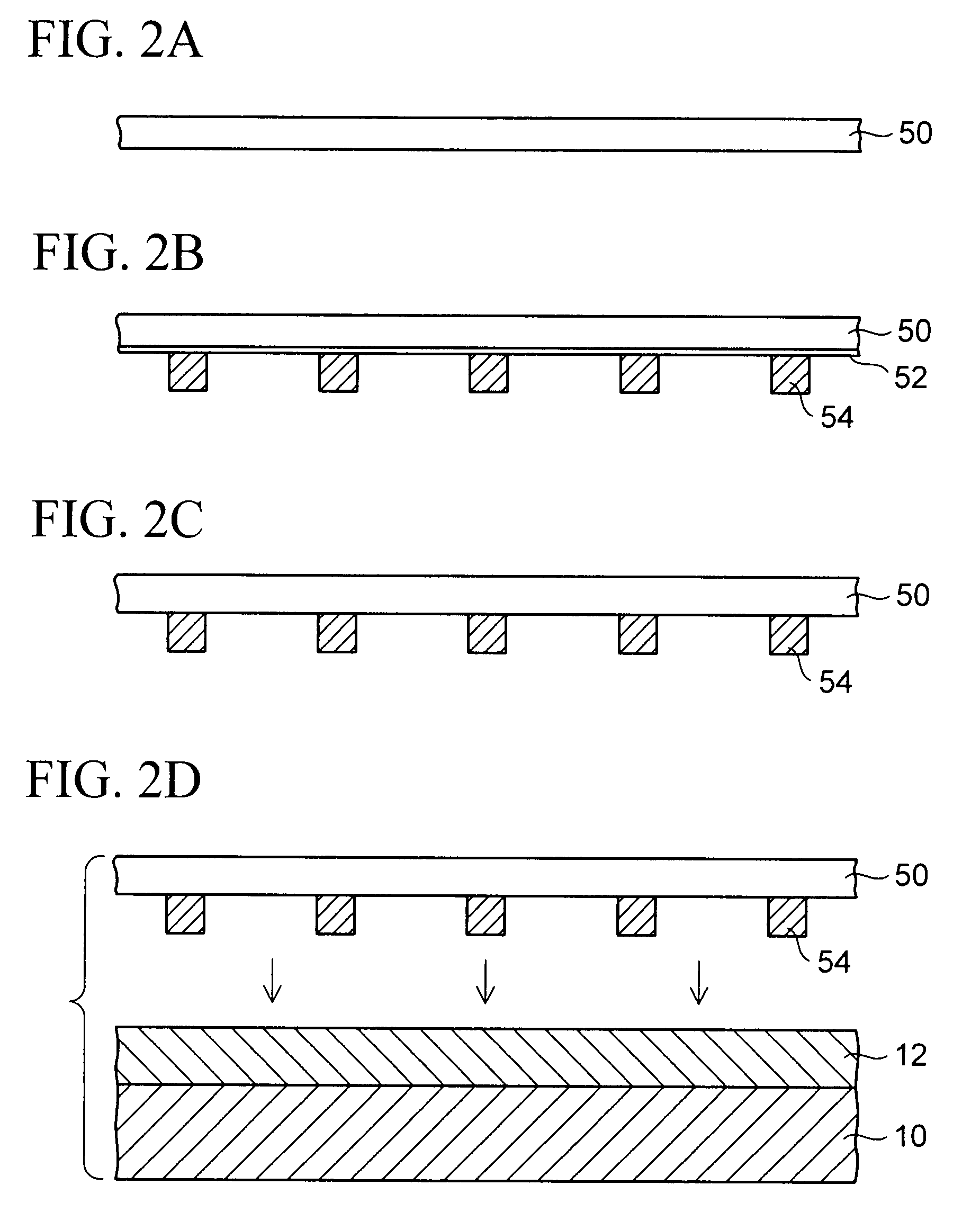

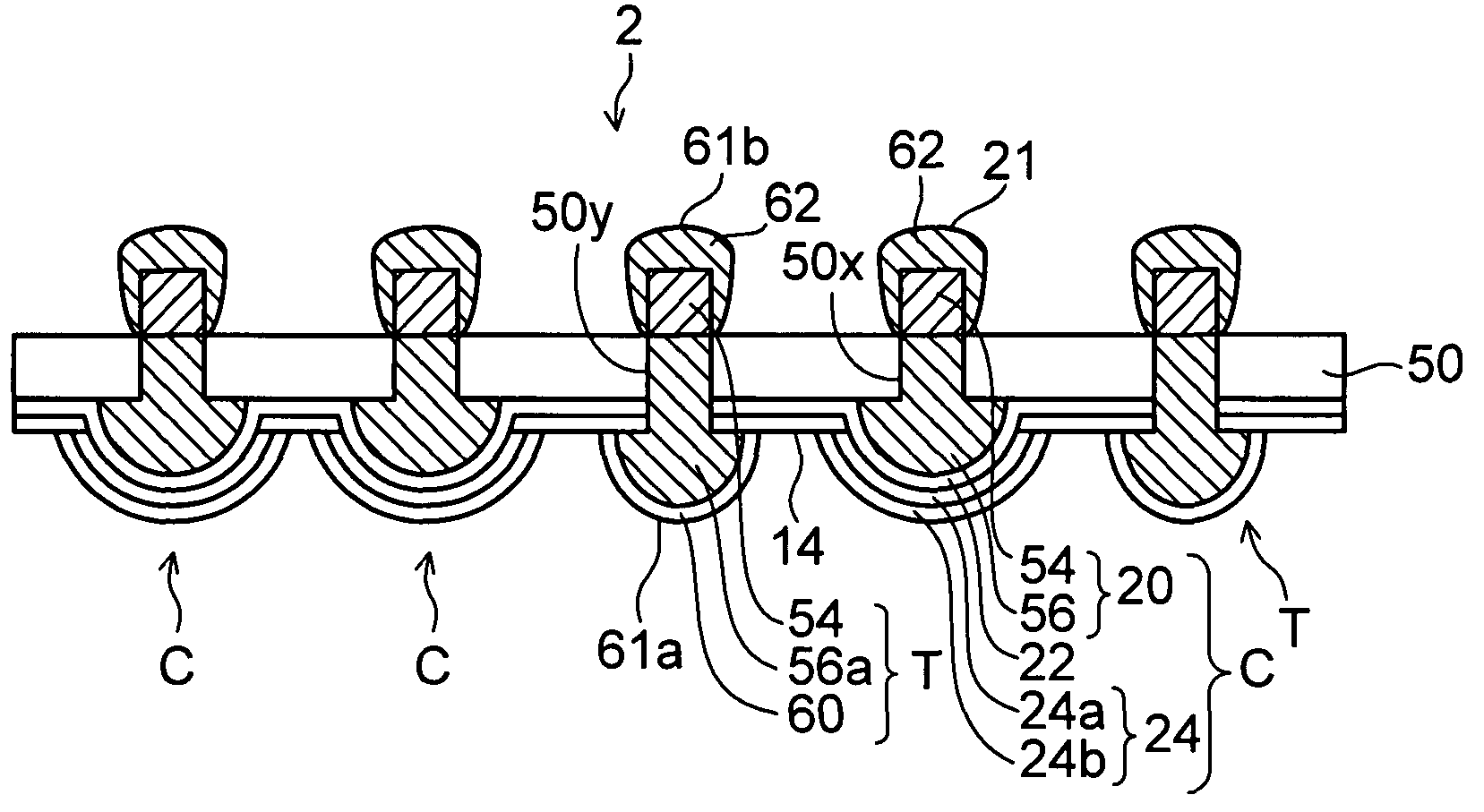

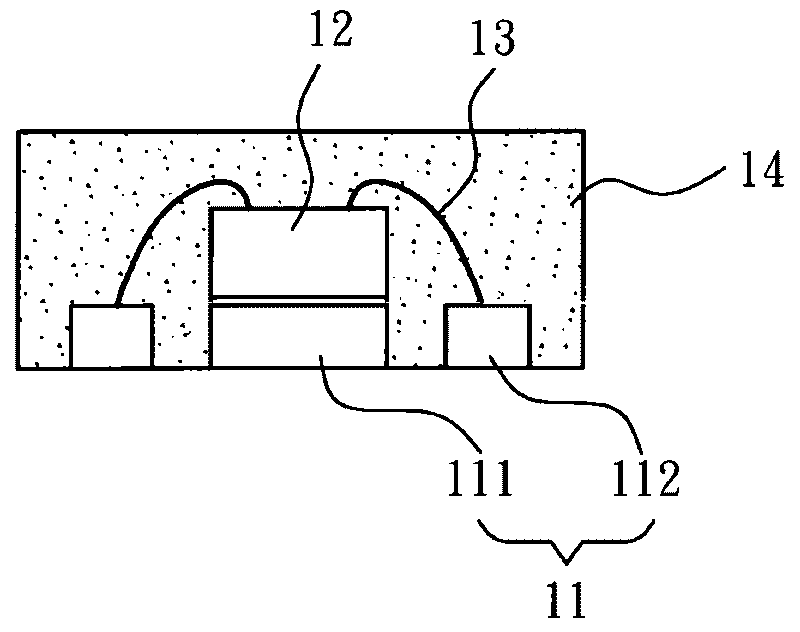

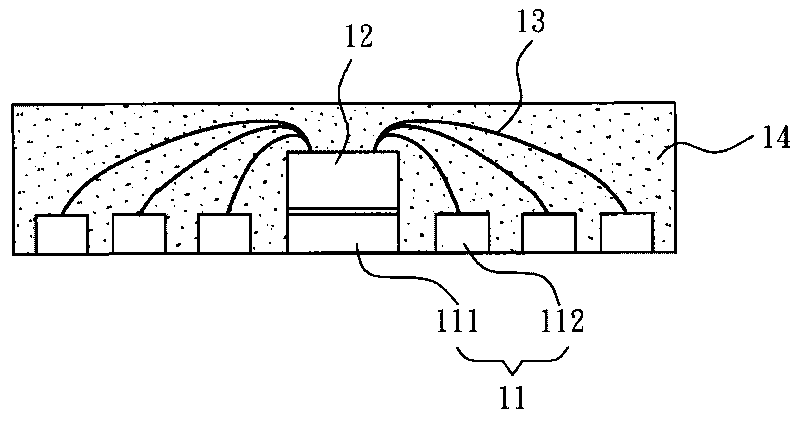

Capacitor built-in substrate and method of manufacturing the same and electronic component device

InactiveUS20080291649A1Easy to manufactureLarge design marginSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

A capacitor built-in substrate of the present invention includes; a base resin layer; a plurality of capacitors arranged side by side in a lateral direction in a state that the capacitors are passed through the base resin layer, each of the capacitors constructed by a first electrode provided to pass through the base resin layer and having projection portions projected from both surface sides of the base resin layer respectively such that the projection portion on one surface side of the base resin layer serves as a connection portion, a dielectric layer for covering the projection portion of the first electrode on other surface side of the base resin layer, and a second electrode for covering the dielectric layer; a through electrode provided to pass through the base resin layer and having projection portions projected from both surface sides of the base resin layer respectively; and a built-up wiring formed on the other surface side of the base resin layer and connected to the second electrodes of the capacitors and one end side of the through electrode.

Owner:SHINKO ELECTRIC IND CO LTD

Capacitor built-in interposer and method of manufacturing the same and electronic component device

InactiveUS20080030968A1Easy to manufactureEasy to buildSemiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

A capacitor built-in interposer of the present invention, includes a base resin layer, a capacitor first electrode provided to pass through the base resin layer and having projection portions projected from both surface sides of the base resin layer respectively whereby the projection portion on one surface side of the base resin layer serves as a connection portion, a capacitor dielectric layer for covering the projection portion of the first electrode on other surface side of the base resin layer, and a capacitor second electrode for covering the dielectric layer, wherein a plurality of capacitors each constructed by the first electrode, the dielectric layer, and the second electrode are arranged and aligned in a lateral direction in a state that the capacitors are passed through the base resin layer.

Owner:SHINKO ELECTRIC IND CO LTD

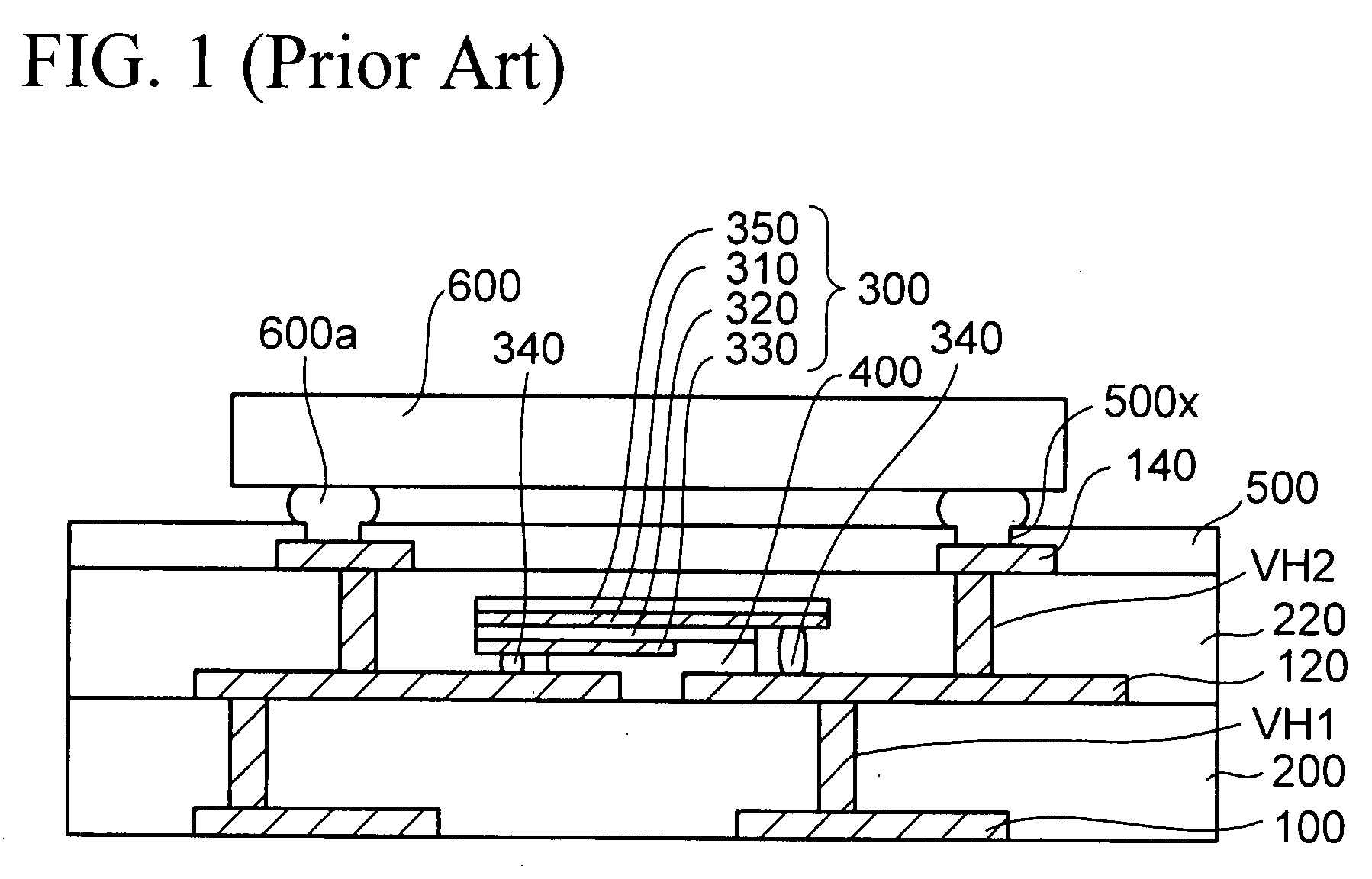

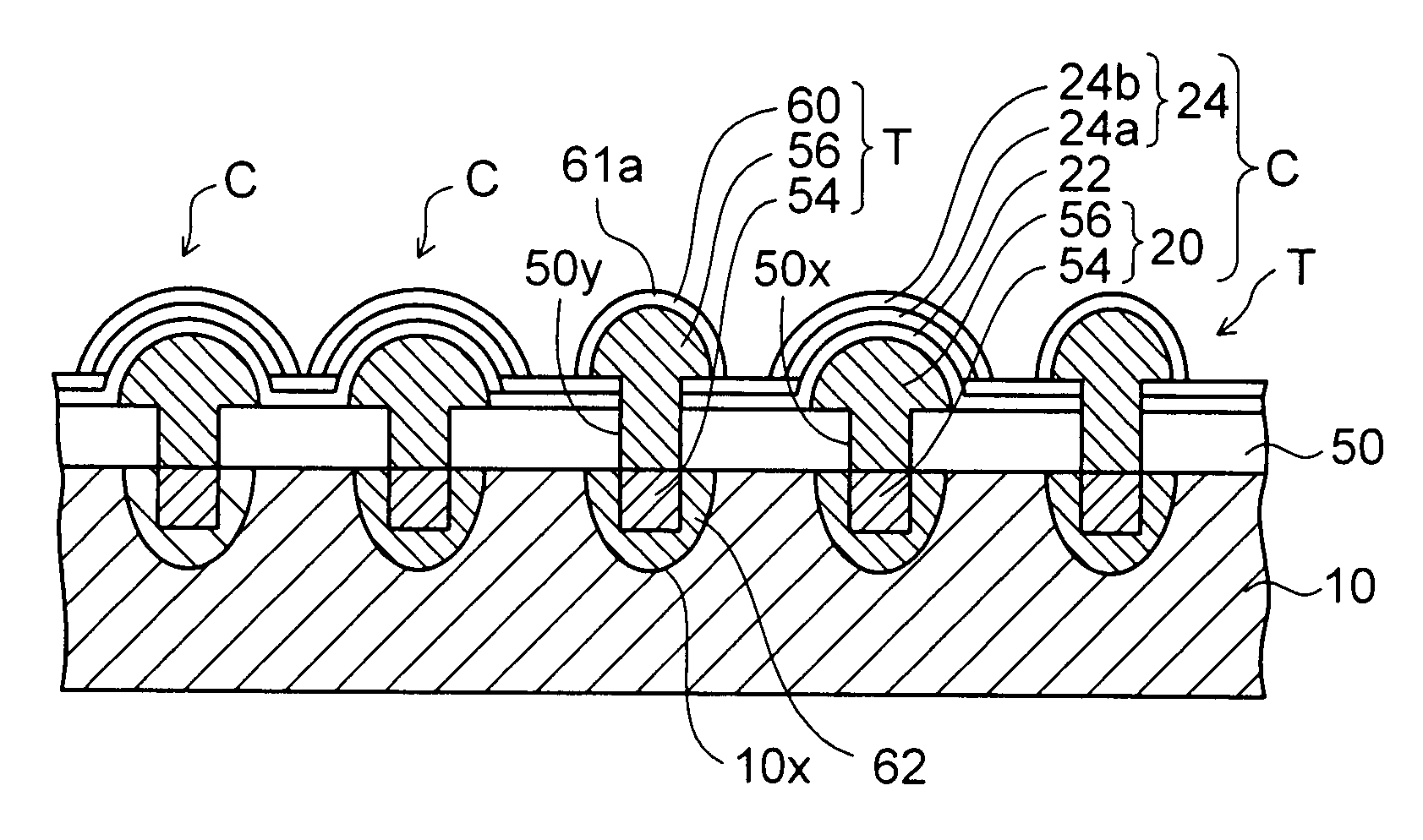

Semiconductor device

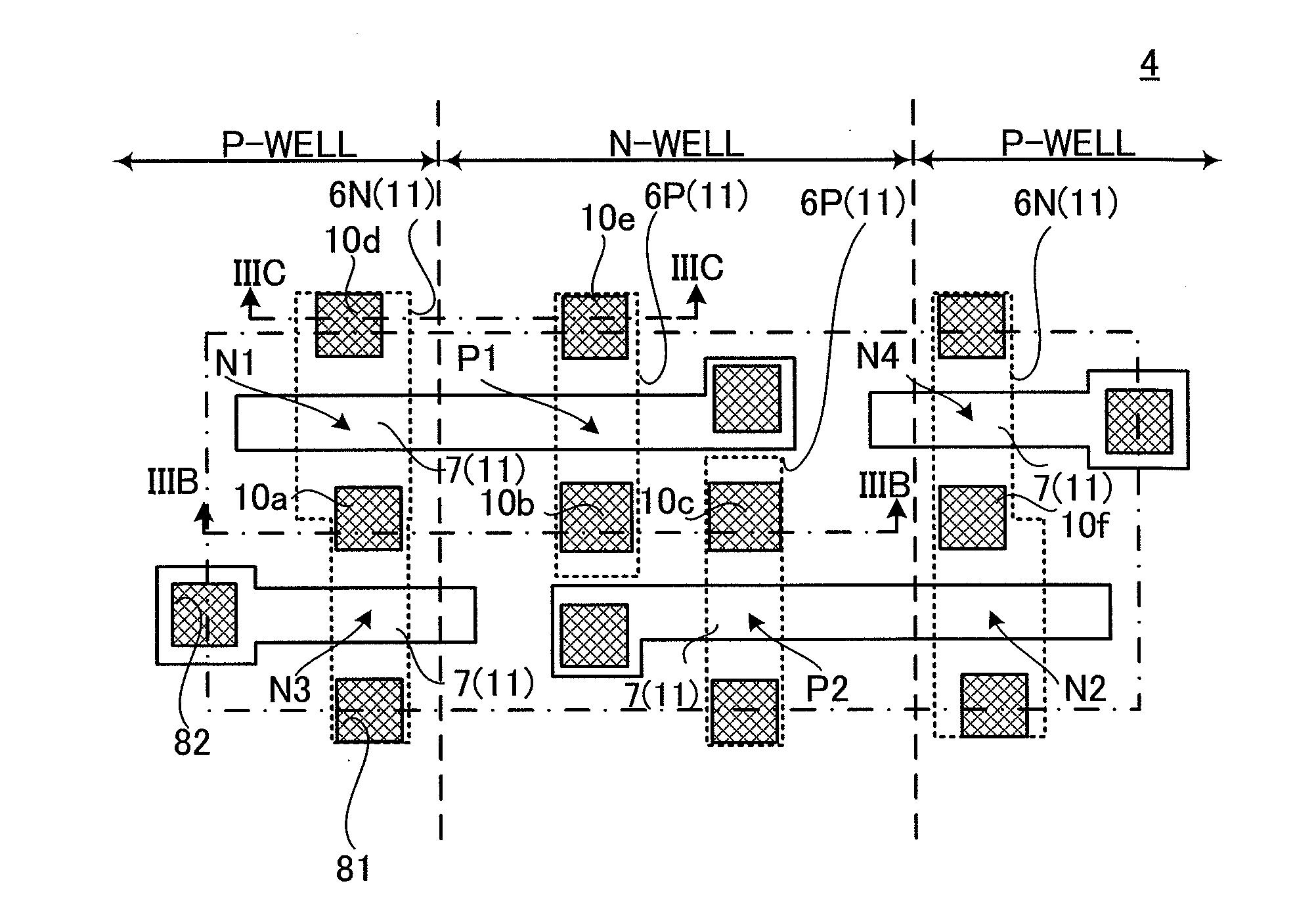

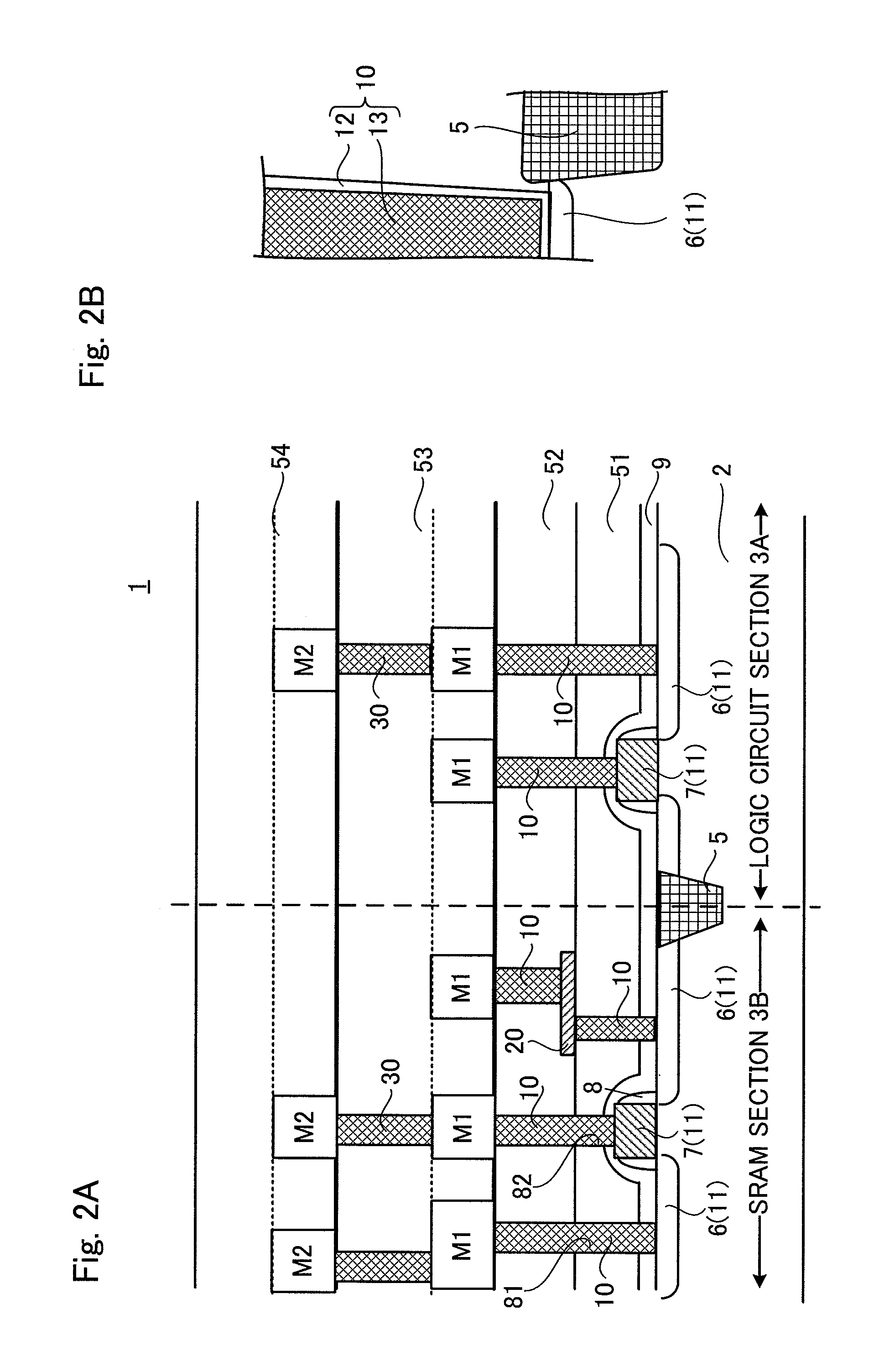

InactiveUS20100123253A1Increase design marginReduce short circuit failureTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

An exemplary embodiment of the present invention is a semiconductor device having a regular layout region and an irregular layout region formed on one chip, including: a lower conductive layer; an interlayer insulating film formed on the lower conductive layer; an upper interconnect layer formed on the interlayer insulating film; and connection plugs disposed to electrically connect the lower conductive layer and the upper interconnect layer at a substantially shortest distance. In at least part of the regular layout region, the lower conductive layer and the upper interconnect layer are electrically connected to each other through at least two connection plugs and an intermediate connection layer for electrically connecting the at least two connection plugs, the at least two connection plugs being disposed at an immediately above position extending from immediately above the lower conductive layer and a shift position spaced apart from the immediately above position, respectively.

Owner:RENESAS ELECTRONICS CORP

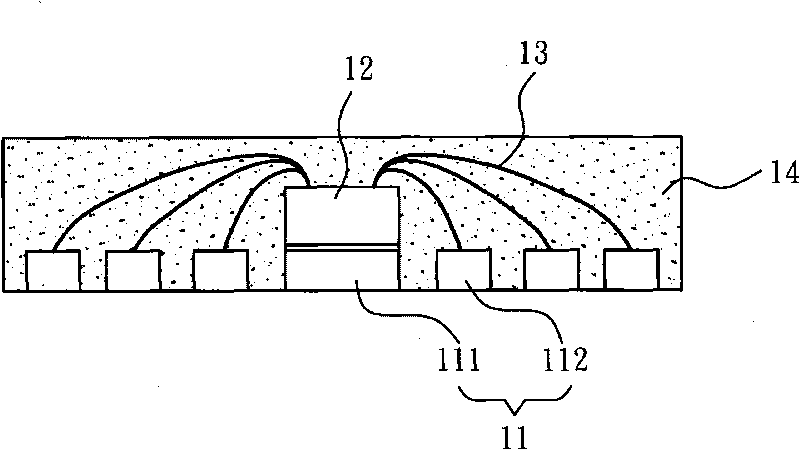

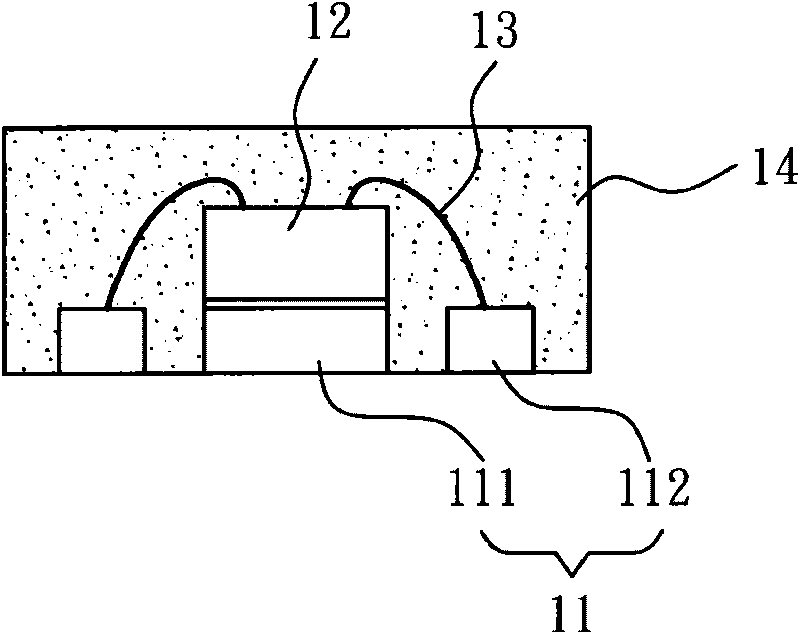

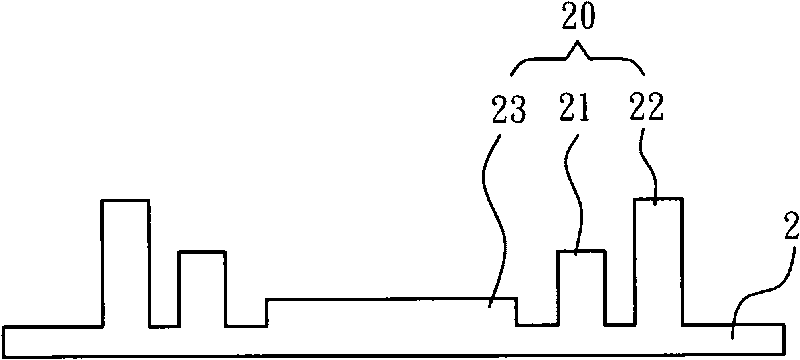

Semiconductor package without outer pins and stacked structure thereof

InactiveCN101764127AMeet the needs of high-density packagingIncrease design marginSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

The present invention discloses a semiconductor package without outer pins and a stacked structure thereof. A first package is formed by arranging at least one chip on a lead frame and carrying out a potting procedure. The two ends of a plurality of contacts are exposed out of the first package, so at least one second package is connected with one of the ends of the contacts. Thus, a POP (package on package) novel multi-chip module structure is made by taking the lead frame of a QFN (quad flat non-leaded) package structure as the base frame.

Owner:ASE ASSEMBLY & TEST SHANGHAI

Capacitor built-in substrate and method of manufacturing the same and electronic component device

InactiveUS7936568B2Large design marginInductance between the semiconductor chip and the capacitors can be reducedSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

A capacitor built-in substrate of the present invention includes; a base resin layer; a plurality of capacitors arranged side by side in a lateral direction in a state that the capacitors are passed through the base resin layer, each of the capacitors constructed by a first electrode provided to pass through the base resin layer and having projection portions projected from both surface sides of the base resin layer respectively such that the projection portion on one surface side of the base resin layer serves as a connection portion, a dielectric layer for covering the projection portion of the first electrode on other surface side of the base resin layer, and a second electrode for covering the dielectric layer; a through electrode provided to pass through the base resin layer and having projection portions projected from both surface sides of the base resin layer respectively; and a built-up wiring formed on the other surface side of the base resin layer and connected to the second electrodes of the capacitors and one end side of the through electrode.

Owner:SHINKO ELECTRIC IND CO LTD

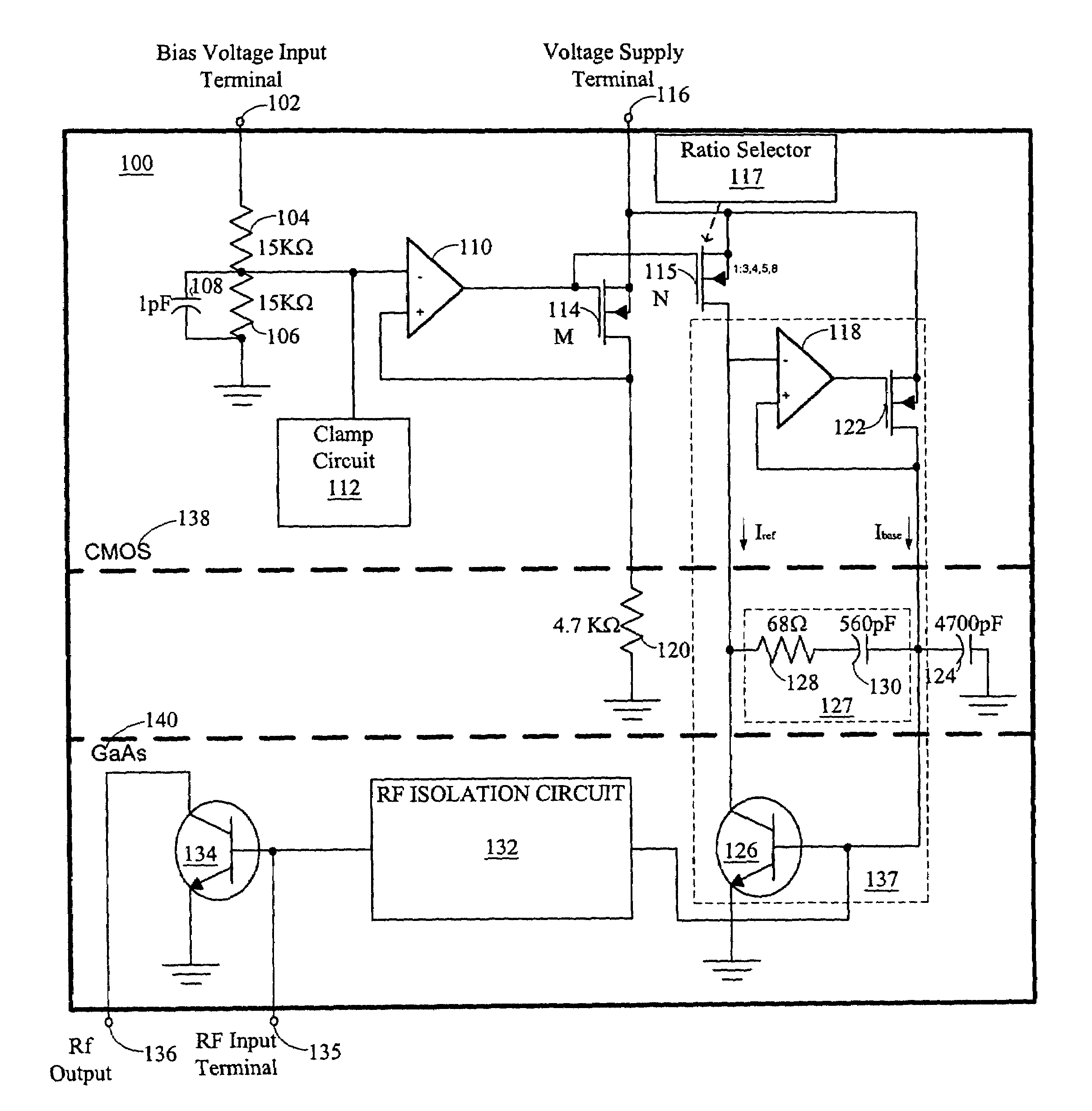

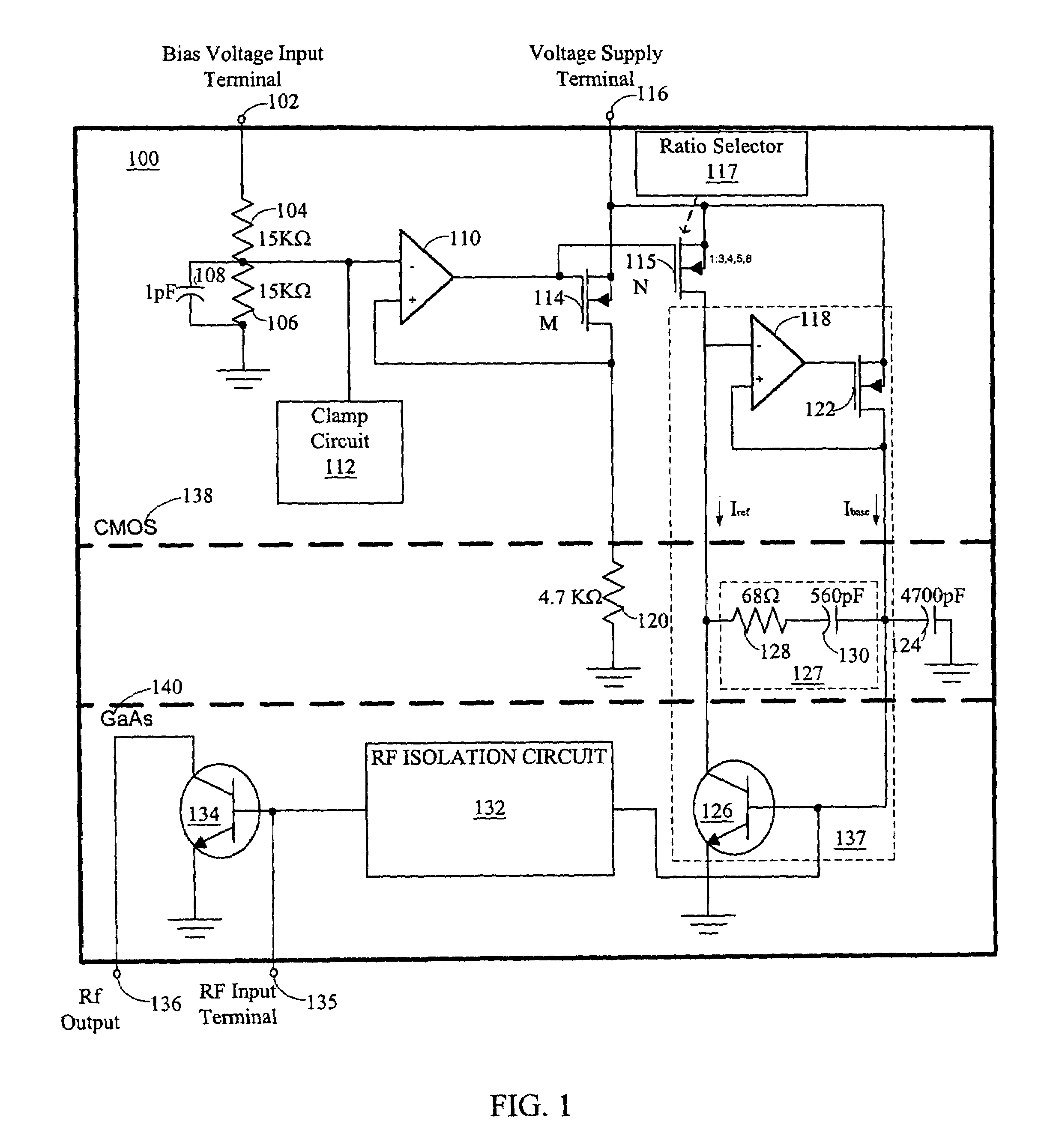

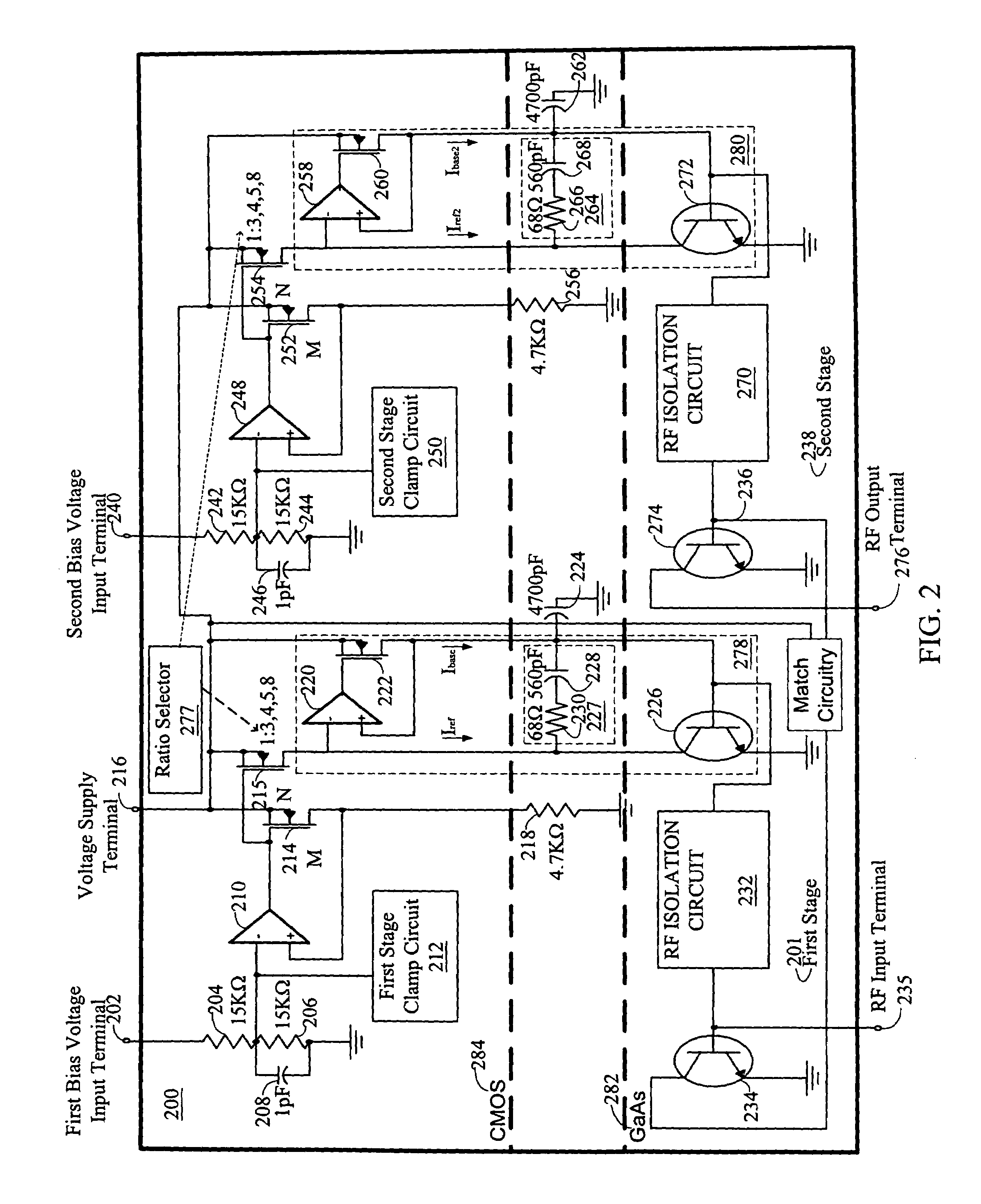

Constant current biasing circuit for linear power amplifiers

InactiveUS7443246B2Reduce variationIncrease design marginAmplifier modifications to reduce temperature/voltage variationGain controlLinear power amplifierEngineering

A constant current bias approach that receives an input bias voltage and maintains a temperature independent constant current bias in a linear amplifier device. Integrated sense circuitry protects against unacceptable input voltages to guarantee bias stability. Fabrication in multiple semiconductor technologies and assembly into a single package allows for optimum cost and performance of DC bias and RF amplifier sections.

Owner:SKYWORKS SOLUTIONS INC

Titanium-aluminum-tin alloy applied to golf club head

InactiveCN101514412ARaise room temperatureHigh temperature strengthGolf clubsRacket sportsNiobiumAlloy

The invention relates to a titanium-aluminum-tin alloy applied to a golf club head, which comprises the following materials in percentage by weight: 89 to 95 percent of titanium, 3.5 to 6.5 percent of aluminum and 1.5 to 3.5 percent of tin. The titanium-aluminum-tin alloy can be selectively added with trace elements such as niobium, vanadium, molybdenum, zirconium, chromium, iron, silicon, oxygen, nitrogen, and the like to form a high elongation material with the elongation of between 11 and 15 percent and the tensile strength of between 700 and 950 Mpa. The high elongation material can be applied to a body and a batter side of the golf club head; and by the design of an internal structure of the body and the design of a structure of balance weight and fins, products of the golf club head have good beating performance, shock controlling and golf controlling performances, adjustable angles and individuation.

Owner:ADVANCED INT MULTITECH CO LTD

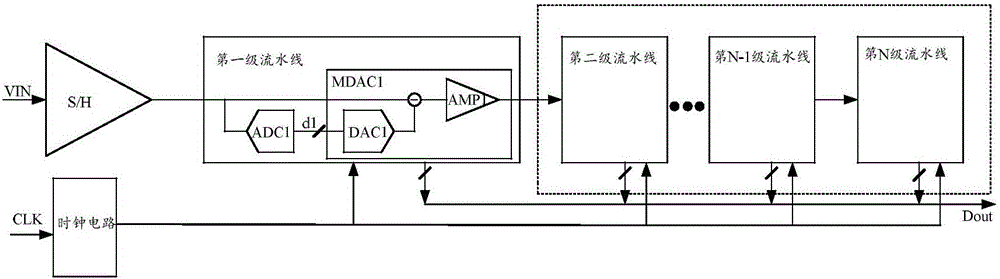

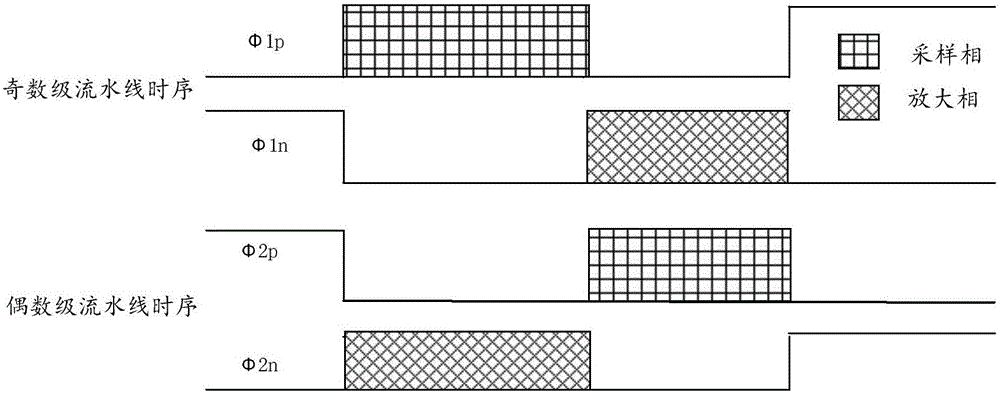

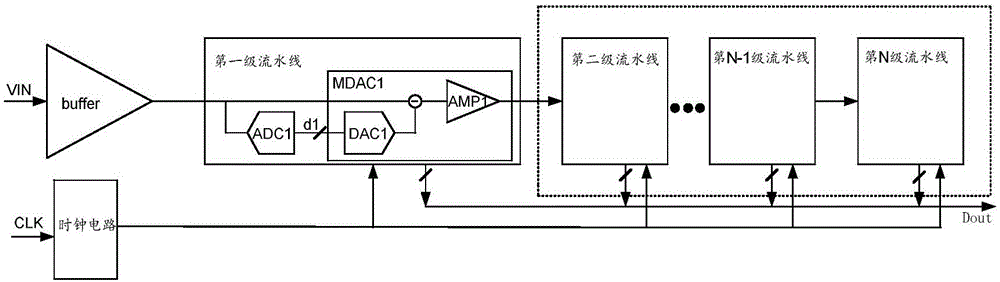

Clock circuit used for high-speed high-precision SHA-less pipelined analog-to-digital converter

ActiveCN105763193AGuaranteed accuracyImprove reusabilityAnalogue-digital convertersPhysical parameters compensation/preventionEngineeringAnalog-to-digital converter

The invention provides a clock circuit used for a high-speed high-precision SHA-less pipelined analog-to-digital converter. The clock circuit comprises first and second duty ratio stabilizing circuits and first to Nth output clock buffers. The first duty ratio stabilizing circuit generates a clock of which the duty ratio is adjustable and less than 50% and the clock is used for the first stage pipeline time sequence control. The second duty ratio stabilizing circuit generates a clock of which the duty ratio is 50% and the clock is used for the second stage to the Nth stage pipeline time sequence control. The first output clock buffer performs delay tuning on the clock outputted by the first duty ratio stabilizing circuit so as to realize time sequence alignment of the first stage pipeline and the subsequent stage pipeline. The second to the Nth output clock buffers drive the clock outputted by the second duty ratio stabilizing circuit. The two duty ratio stabilizing circuits are connected in series. Time sequence distribution of the first stage pipeline is enabled to be optimized by the clock of which the duty ratio is less than 50% so as to reduce the design difficulty of an operational amplifier, and the second to the Nth stage time sequences are enabled to be optimized by the clock of which the duty ratio is 50% so as to increase the reuse degree of the unit circuit.

Owner:CHONGQING GIGACHIP TECH CO LTD

Low-density alloy for head of golf rod

InactiveCN1958821AIncrease design marginAdjust the center of gravityGolf clubsTrace elementVolumetric Mass Density

This invention discloses a low-density alloy for head of golf club. The alloy comprises: Ti 84-94 wt.%, Al 6.5-9.5 wt.% (or 5.5-8.5 wt.%), and V less than 1.5 wt.% (or less than 3.0 wt.%). Selectively, trace elements such as Mo, Ge, Fe, Si and / or B can also be added. Since the major component is Ti with a density lower than 4.40 g / cm3, and obtained Ti alloy has a low density and a high elongation rate.

Owner:FUSHENG IND CO LTD

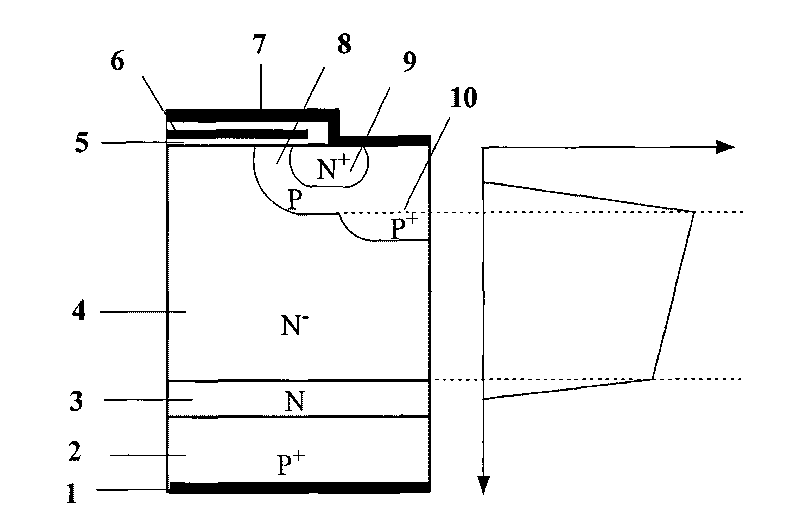

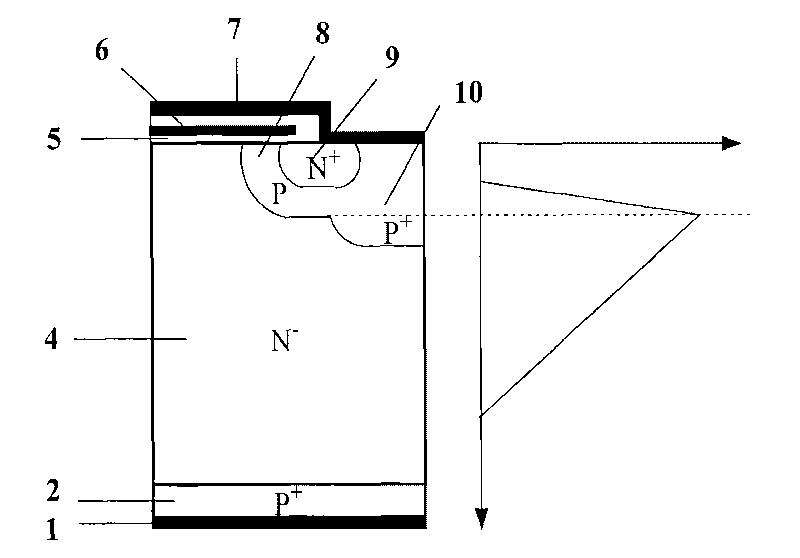

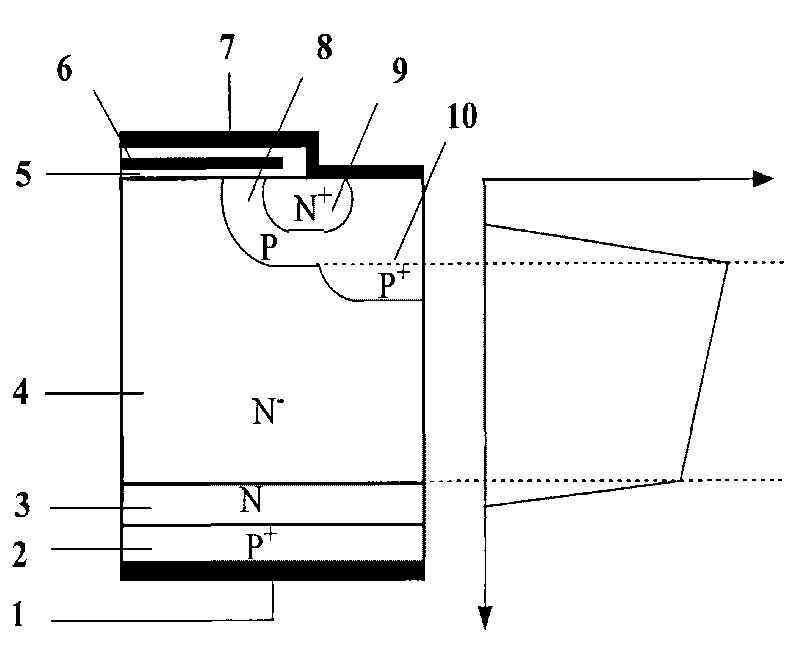

Grooved gate IGBT with P-type floating layer

InactiveCN101694851ALower saturation current densityImprove breakdown voltageSolid-state devicesSemiconductor devicesVoltage dropDrain current

The invention relates to a grooved gate IGBT with a P-type floating layer, belonging to the technical filed of semiconductor power devices. On a basis of grooved gate insulated-gate bipolar transistor (IGBT) controlled by an accumulation layer, a P-type floating layer (11) is introduced to effectively improve the electric-field integration effect of the bottom of the grooved gate and greatly increase the breakdown voltage of the device. Meanwhile, due to the existence of the P-type floating layer, a JFET zone is introduced to play the effect of shielding the groove barrier potential of the accumulation layer to a certain extent and greatly reduce the drain current of the device. When the device is forwardly conducted, the saturation current density of the device is greatly decreased so as to greatly improve the short-circuit safety operation area (SCSOA) of the device. The invention maintains the original low forward-conducted voltage drop of the grooved gate IGBT controlled by the accumulation layer and increases the forward bias safety operation area (FBSOA) and the bolt current density while decreasing the drain current of the device, improving the breakdown voltage of the device and greatly improving the SCSOA of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Semiconductor laser device and manufacturing method thereof

ActiveUS7279751B2Sufficient epitaxial growth-rateSignificant growthOptical wave guidanceLaser detailsOptoelectronicsActive layer

Owner:PANASONIC CORP

Capacitor built-in interposer and method of manufacturing the same and electronic component device

InactiveUS7755910B2Inductance generatedIncrease speedSemiconductor/solid-state device detailsSolid-state devicesInterposerElectronic component

Owner:SHINKO ELECTRIC IND CO LTD

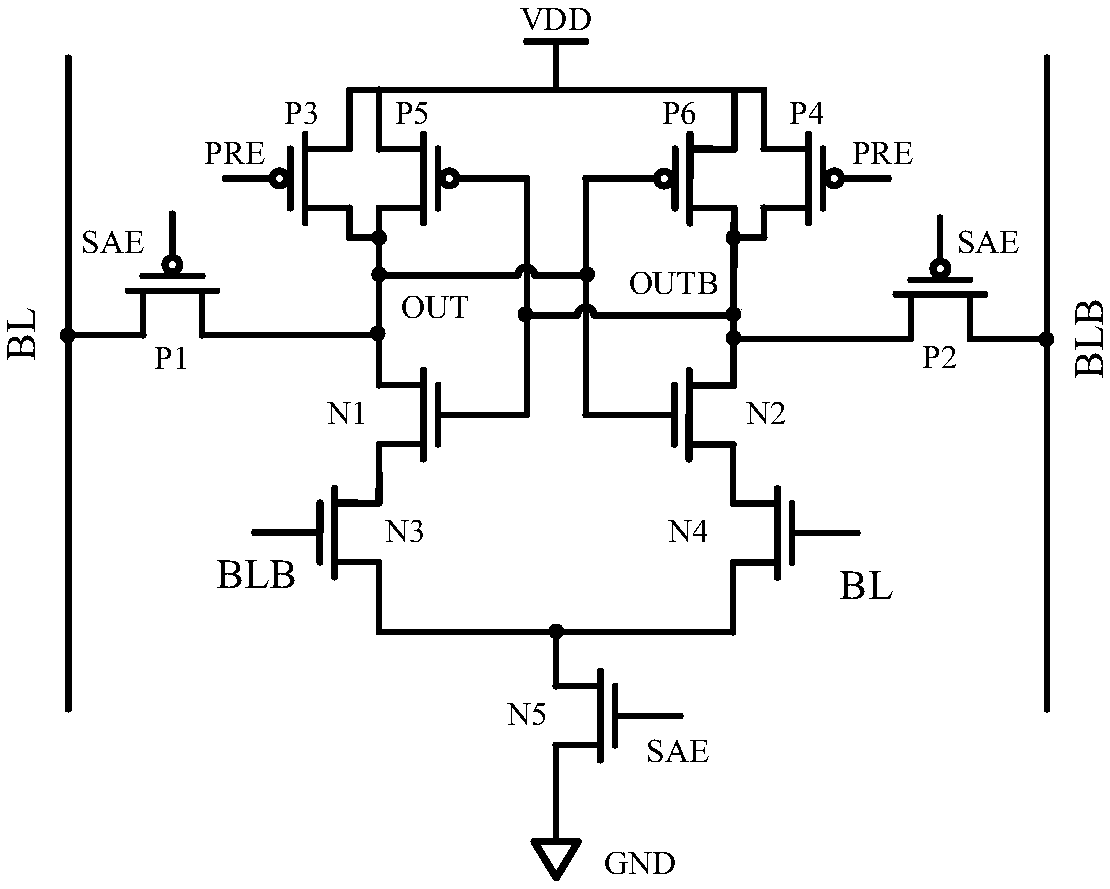

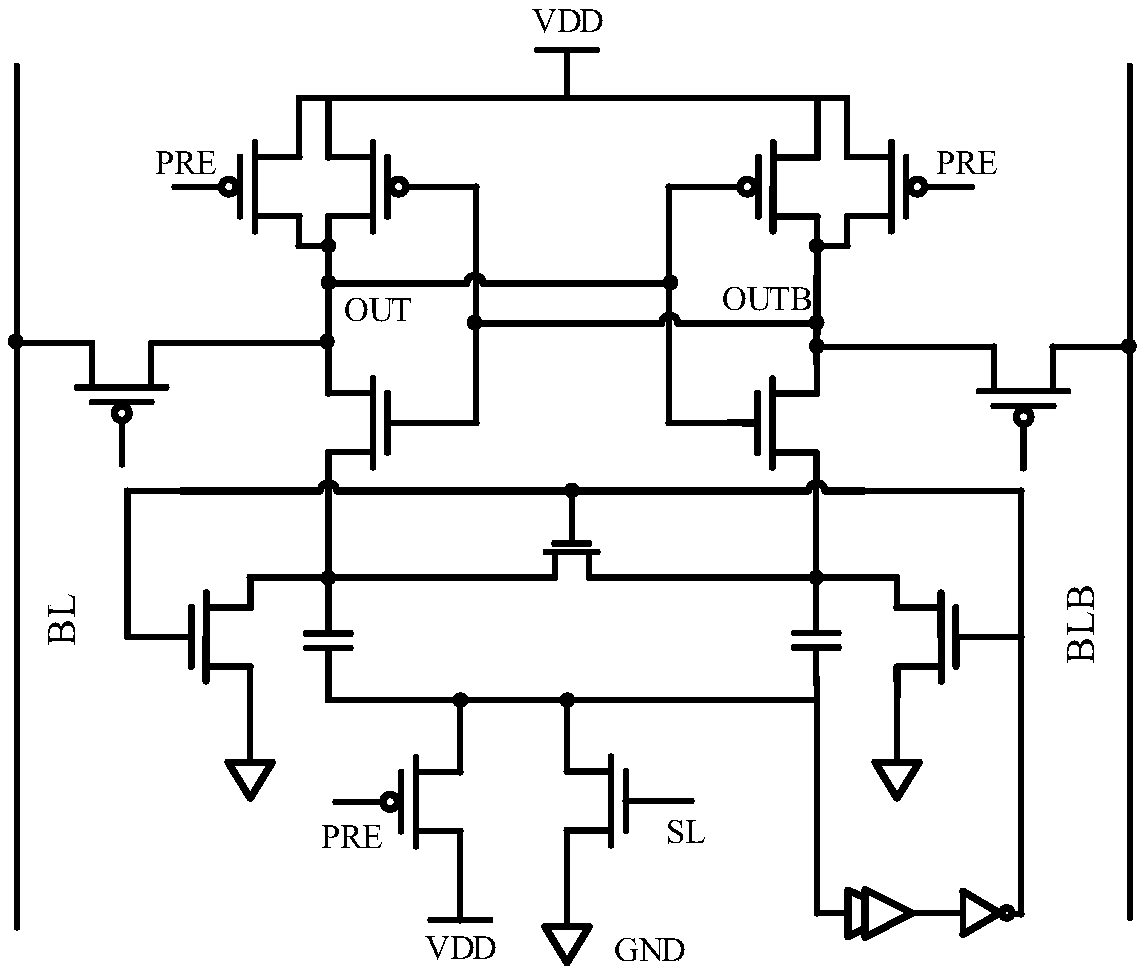

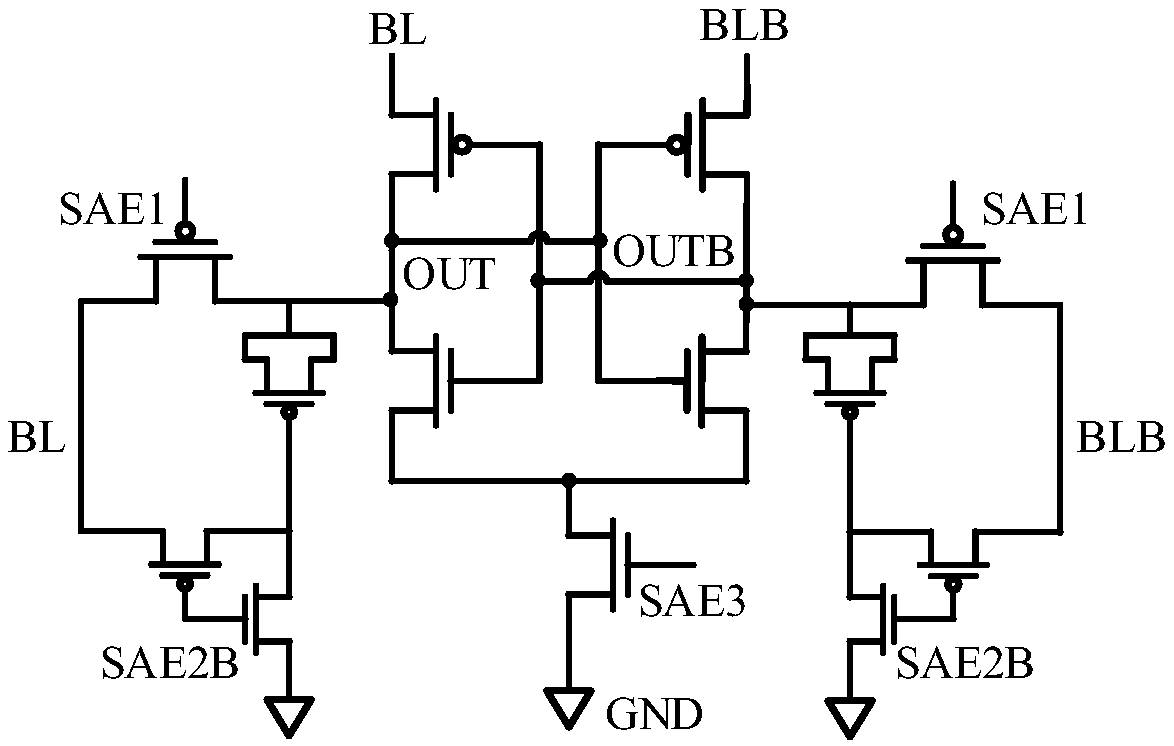

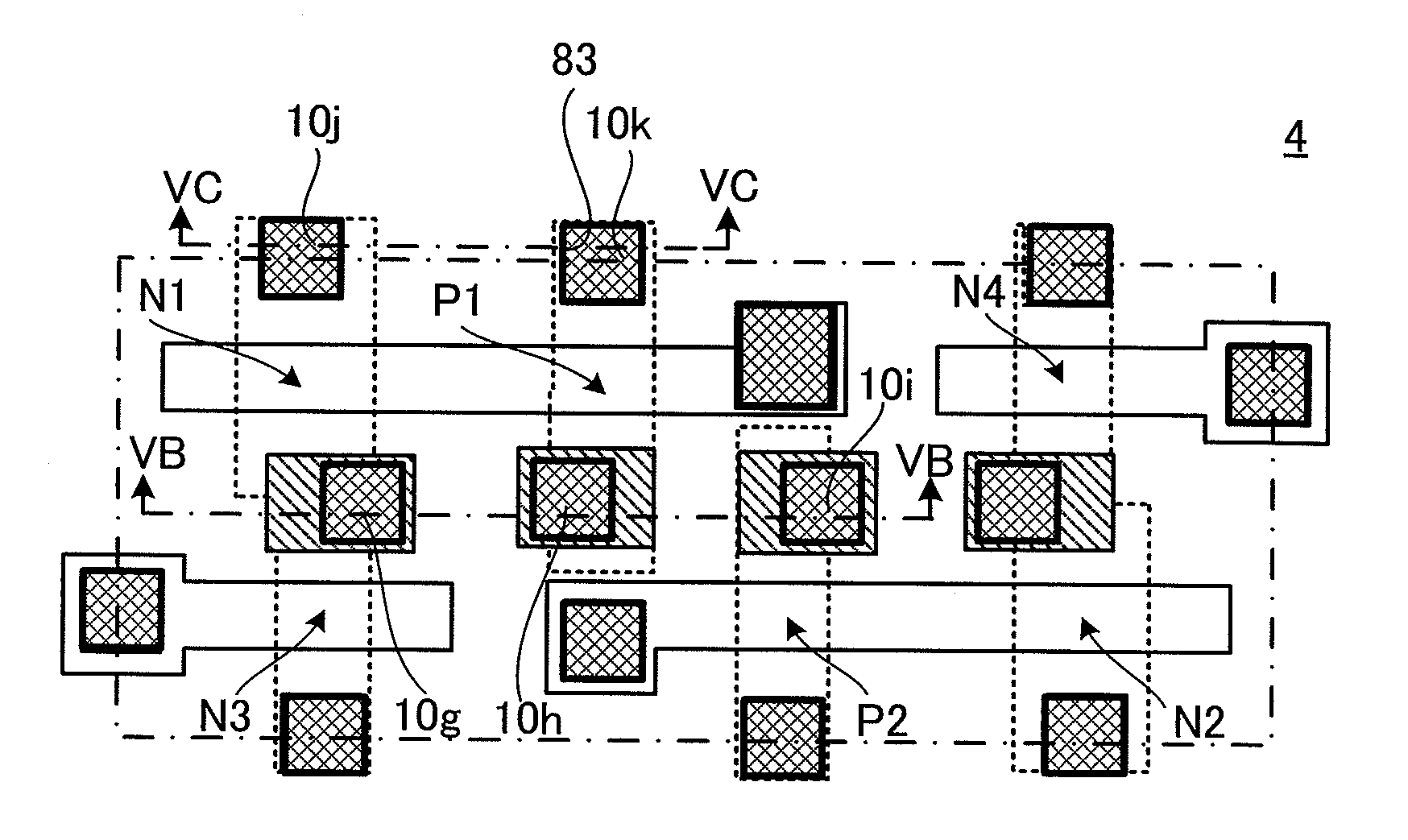

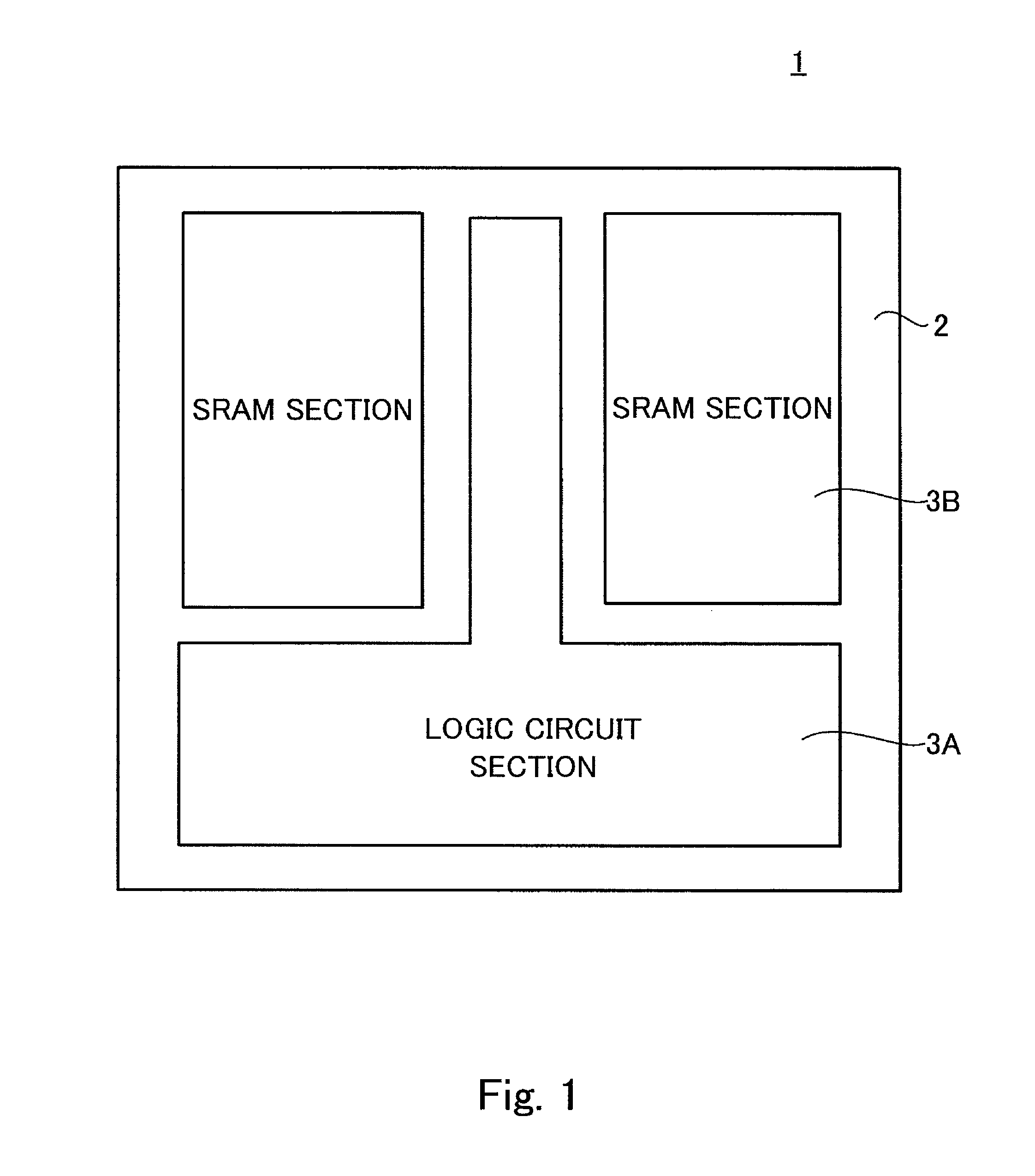

A sensitive amplifier circuit with ultra-low offset

PendingCN109448768AReduce power consumptionImprove data reading speedDigital storageCapacitanceStatic random-access memory

The invention discloses a sensitive amplifier circuit with ultra-low offset. According to the sensitive amplifier structure, the offset voltage can be greatly reduced, amplification of the bit line voltage difference and storage compensation of the threshold voltage difference are achieved through the capacitor storage voltage and the characteristic that the voltage is not suddenly changed, and the effect of greatly reducing the offset voltage is achieved. Meanwhile, along with great reduction of offset voltage, the data reading speed of the static random access memory can be effectively increased, the energy consumption during unit reading is reduced, and the margin of the reading voltage of the static random access memory is effectively improved.

Owner:ANHUI UNIVERSITY

Welding method and clamp of Venturi tube with bend

ActiveCN102990265ASimple structural designMeet welding requirementsWelding/cutting auxillary devicesAuxillary welding devicesEdge surfaceEngineering

The invention discloses a welding method and clamp of a Venturi tube with a bend. The welding method comprises the steps of: respectively clamping and positioning an inlet section and an outlet section of a Venturi tube with a transition section for welding; sequentially spot-welding all spots on a butt seam corresponding to arcs of 0 degree->180 degrees->270 degrees->450 degrees->495 degrees->675 degrees; carrying out sealing welding along the clockwise rotation from the starting point of the butt seam, and after welding the butt seam for one circle, starting arc extinguishing in a place exceeding the starting point by 15 degrees, so as to complete the sealing welding; and selecting a point, between which and the starting point the arc angle is 180 degrees, as another starting point to perform welding, and after welding for one circle, starting the arc extinguishing in a place exceeding the starting point by 15 degrees, so as to complete the welding. The clamp comprises a center shaft with a bend, wherein an inlet inner sleeve and an outlet inner sleeve are sleeved on the center shaft, the outer edge surfaces of the inner sleeves are clung to the inner wall of the Venturi tube, and protection sleeves are respectively arranged on two ends of the inner sleeves, and clamping flanges are respectively arranged on opening ends of an inlet section and an outlet section and are fixed through nuts. According to the welding method and the clamp disclosed by the invention, the Venturi tube with a wall thickness of 1-3mm and the bend of 3-8 degrees can be welded.

Owner:BEIJING AERONAUTICAL MFG TECH RES INST

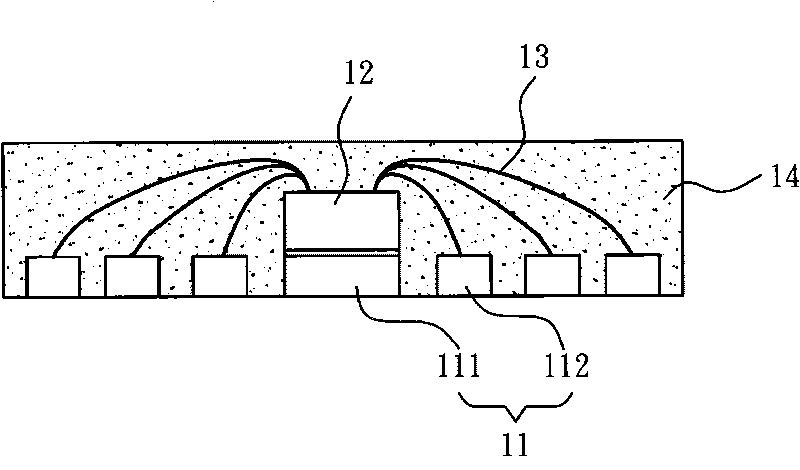

Multi-chip semiconductor package structure without outer leads and lead frame thereof

InactiveCN101764126AMeet the needs of high-density packagingShorten the lengthSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

The present invention discloses a multi-chip semiconductor package structure without outer leads and a lead frame thereof. At least one group of first contacts and at least one group of second contacts, having different heights, are formed on a lead frame and arranged around a chip placement zone preset. The chip placement zone is used for placing a first chip and stacking a second chip. The first contacts are electrically connected to the active surface of the first chip of the most similar height by a plurality of first electrical connecting elements. The second contacts are electrically connected to the active surface of the second chip of the most similar height by a plurality of second electrical connecting elements. Thus, a novel multi-chip module structure of multiple stacked chips is made by taking the lead frame of a QFN (quad flat non-leaded) package structure as the base frame.

Owner:ASE ASSEMBLY & TEST SHANGHAI

Packaging structure of multi-chip semiconductor

InactiveCN101752353AMeet the needs of high-density packagingIncrease design marginSemiconductor/solid-state device detailsSolid-state devicesEngineeringMechanical engineering

The invention discloses a packaging structure of a multi-chip semiconductor, at least a first chip is placed on a wire guide frame, and two ends of a plurality of contact points after the first adhesive sealing procedure, thereby utilizing one end of each contact point for connecting at least one second chip; and then carrying out the second adhesive sealing procedure, thereby realizing an completely new multi-chip module structure which is constructed by taking the wire guide frame with a quad flat non-leaded (QFN) packaging structure as a foundation frame and similar to a package in package (PIP) stacking body.

Owner:ASE ASSEMBLY & TEST SHANGHAI

Display device and method of fabricating the same

InactiveUS8368072B2Promote stability of operational functionIncrease design marginTransistorElectroluminescent light sourcesDisplay deviceEngineering

To achieve promotion of stability of operational function of display device and enlargement of design margin in circuit design, in a display device including a pixel portion having a semiconductor element and a plurality of pixels provided with pixel electrodes connected to the semiconductor element on a substrate, the semiconductor element includes a photosensitive organic resin film as an interlayer insulating film, an inner wall face of a first opening portion provided at the photosensitive organic resin film is covered by a second insulating nitride film, a second opening portion provided at an inorganic insulating film is provided on an inner side of the first opening portion, the semiconductor and a wiring are connected through the first opening portion and the second opening portion and the pixel electrode is provided at a layer on a lower side of an activation layer.

Owner:SEMICON ENERGY LAB CO LTD

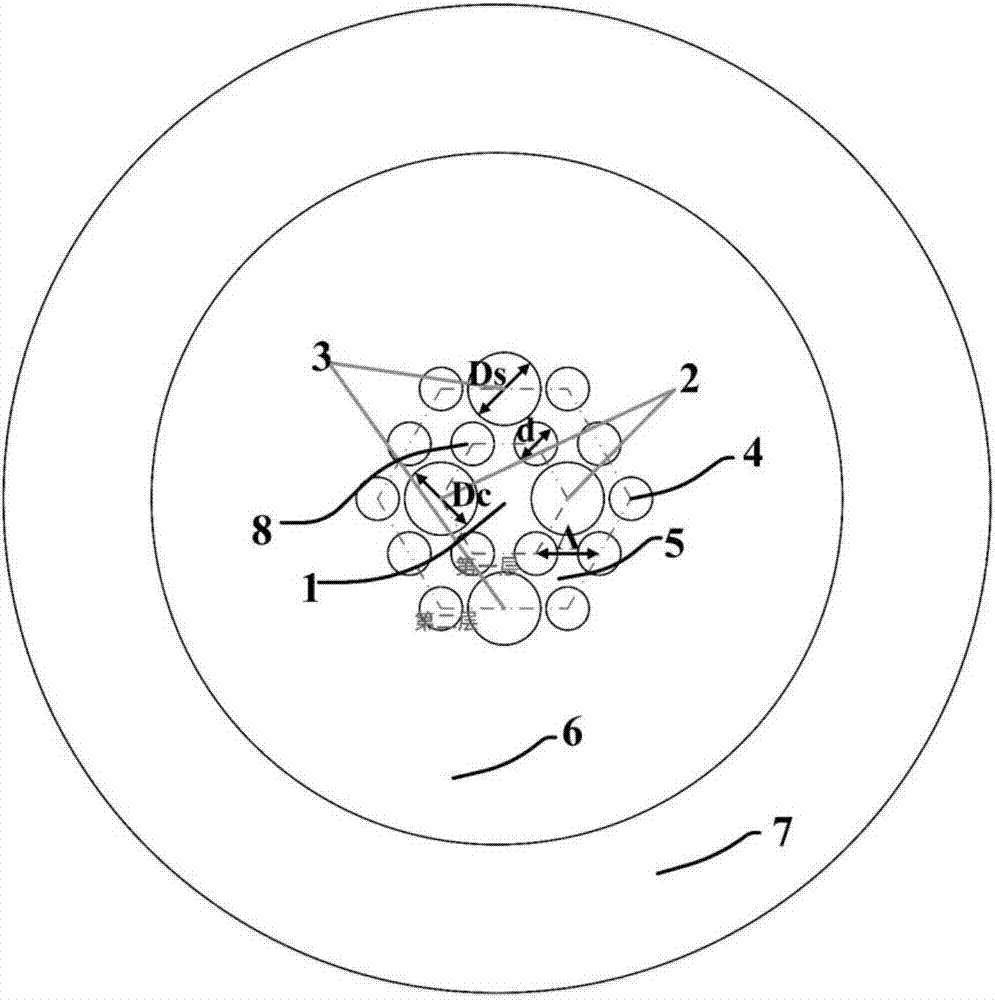

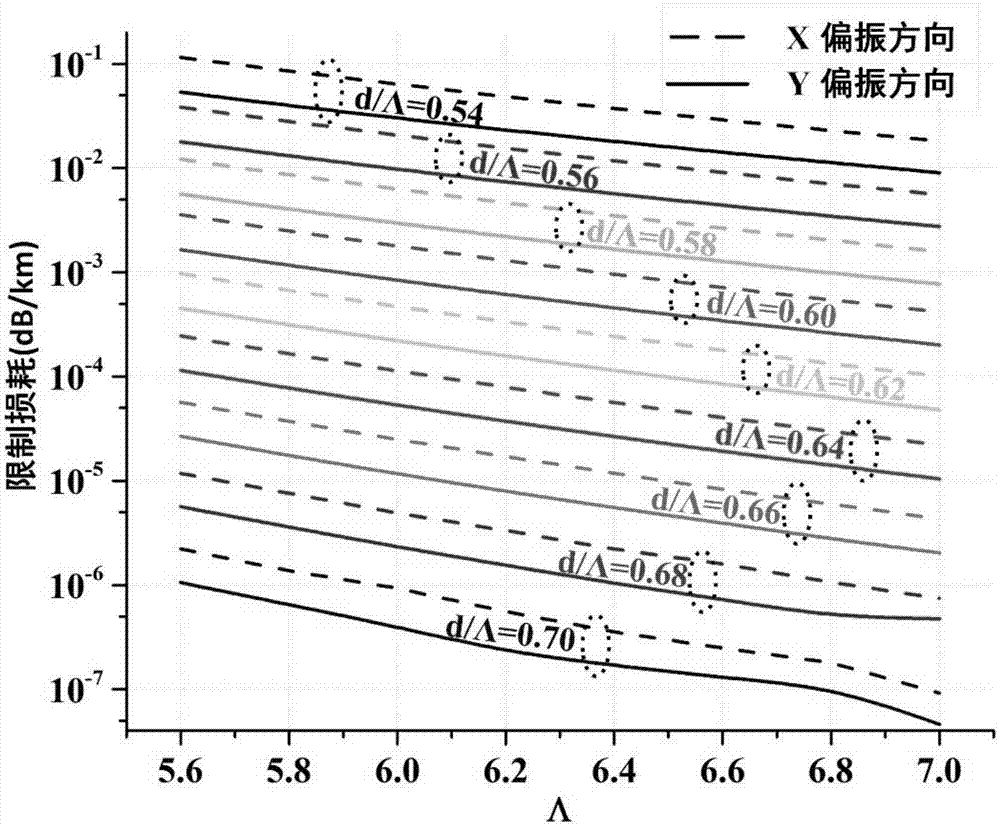

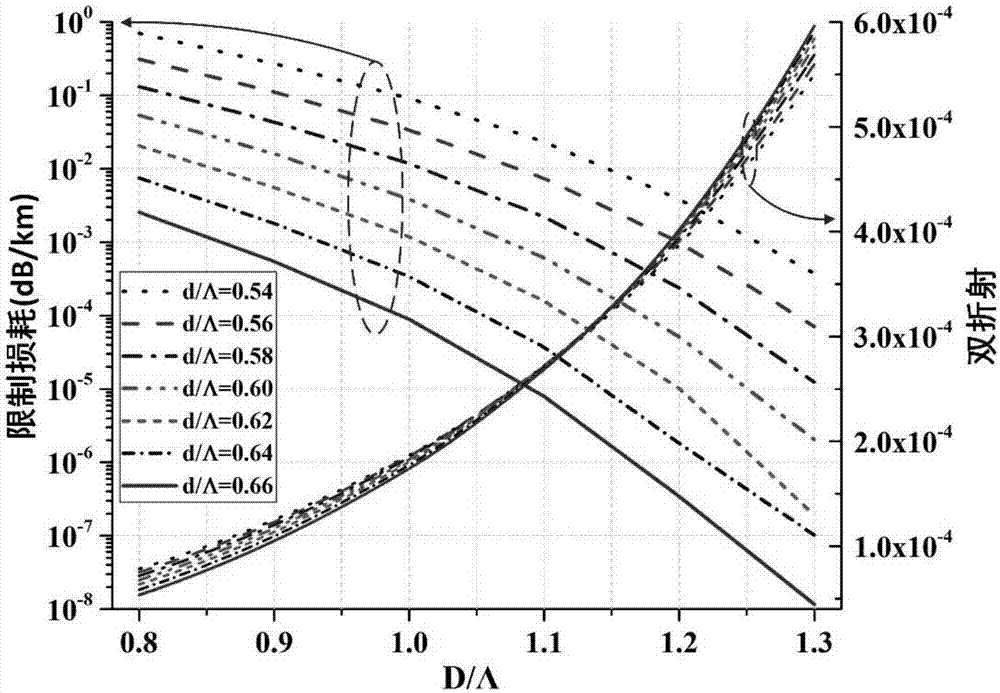

Thin-diameter solid-core polarization-maintaining photonic crystal fiber of two-layer structure

ActiveCN107315221ASmall geometryReduce weightOptical fibre with polarisationOptical waveguide light guideGyroscopePhotonic crystal

The invention discloses a thin-diameter solid-core polarization-maintaining photonic crystal fiber of a two-layer structure, wherein the cross section of an optical fiber is circular. The polarization-maintaining photonic crystal fiber sequentially and structurally comprises a coating layer, a quartz cladding layer, cladding air holes and a fiber core from outside to inside. The cladding air holes are divided into two layers. The first layer of air holes is composed of a first layer of big holes and a first layer of small holes. The second layer of air holes is composed of a second layer of big holes and a second layer of small holes. The circle center of the cross section of the optical fiber serves as an origin and the circle centers of air holes in the first layer are arranged in a regular hexagon shape with the circle center of the cross section of the optical fiber as the distribution center thereof. Two big holes are arranged in the first layer and the two big holes are symmetrically arranged in the transverse direction. Four small holes are arranged in the first layer and the four small holes are at the periphery of the first layer of air holes. The circle centers of air holes in the second layer are arranged in a regular hexagon shape with the circle center of the cross section of the optical fiber as the distribution center thereof. Two big holes are arranged in the second layer and the two big holes are symmetrically arranged in the longitudinal direction. Ten small holes are arranged in the second layer. According to the technical scheme of the invention, the geometrical size of the optical fiber can be greatly reduced. Therefore, the weight of the optical fiber ring is reduced. The size of an optical fiber ring is reduced, and the miniaturization of a gyroscope is facilitated. The integration degree of an optical fiber device is improved.

Owner:BEIHANG UNIV

Semiconductor device

InactiveUS7999385B2Increase design marginReduce leakageTransistorSemiconductor/solid-state device detailsShortest distanceEngineering

An exemplary embodiment of the present invention is a semiconductor device having a regular layout region and an irregular layout region formed on one chip, including: a lower conductive layer; an interlayer insulating film formed on the lower conductive layer; an upper interconnect layer formed on the interlayer insulating film; and connection plugs disposed to electrically connect the lower conductive layer and the upper interconnect layer at a substantially shortest distance. In at least part of the regular layout region, the lower conductive layer and the upper interconnect layer are electrically connected to each other through at least two connection plugs and an intermediate connection layer for electrically connecting the at least two connection plugs, the at least two connection plugs being disposed at an immediately above position extending from immediately above the lower conductive layer and a shift position spaced apart from the immediately above position, respectively.

Owner:RENESAS ELECTRONICS CORP

Motor and bearing supporting structure

ActiveCN101242121APrevent circumferential rotationPrevent axial movementStructural associationSupports/enclosures/casingsEngineeringMechanical engineering

Provided is a motor and bearing support structure thereof to support a shaft. The bearing support structure includes a bushing that has an opening and a placing space, a bearing being positioned in the placing space and supporting at least part of the shaft, and at least one first restriction component being disposed where the bearing is connected with the bushing.

Owner:DELTA ELECTRONICS INC