Patents

Literature

66results about How to "Improve data reading speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

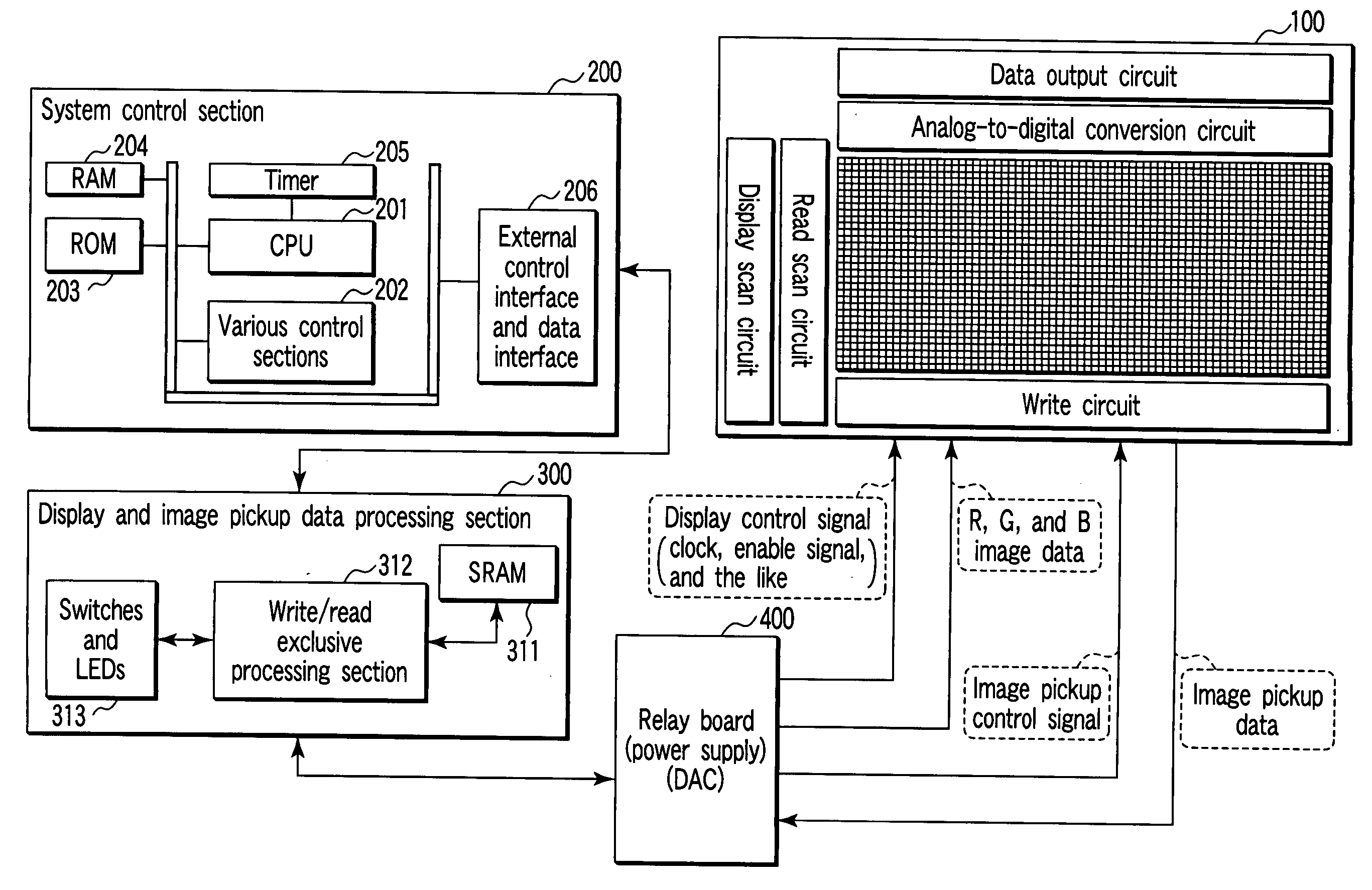

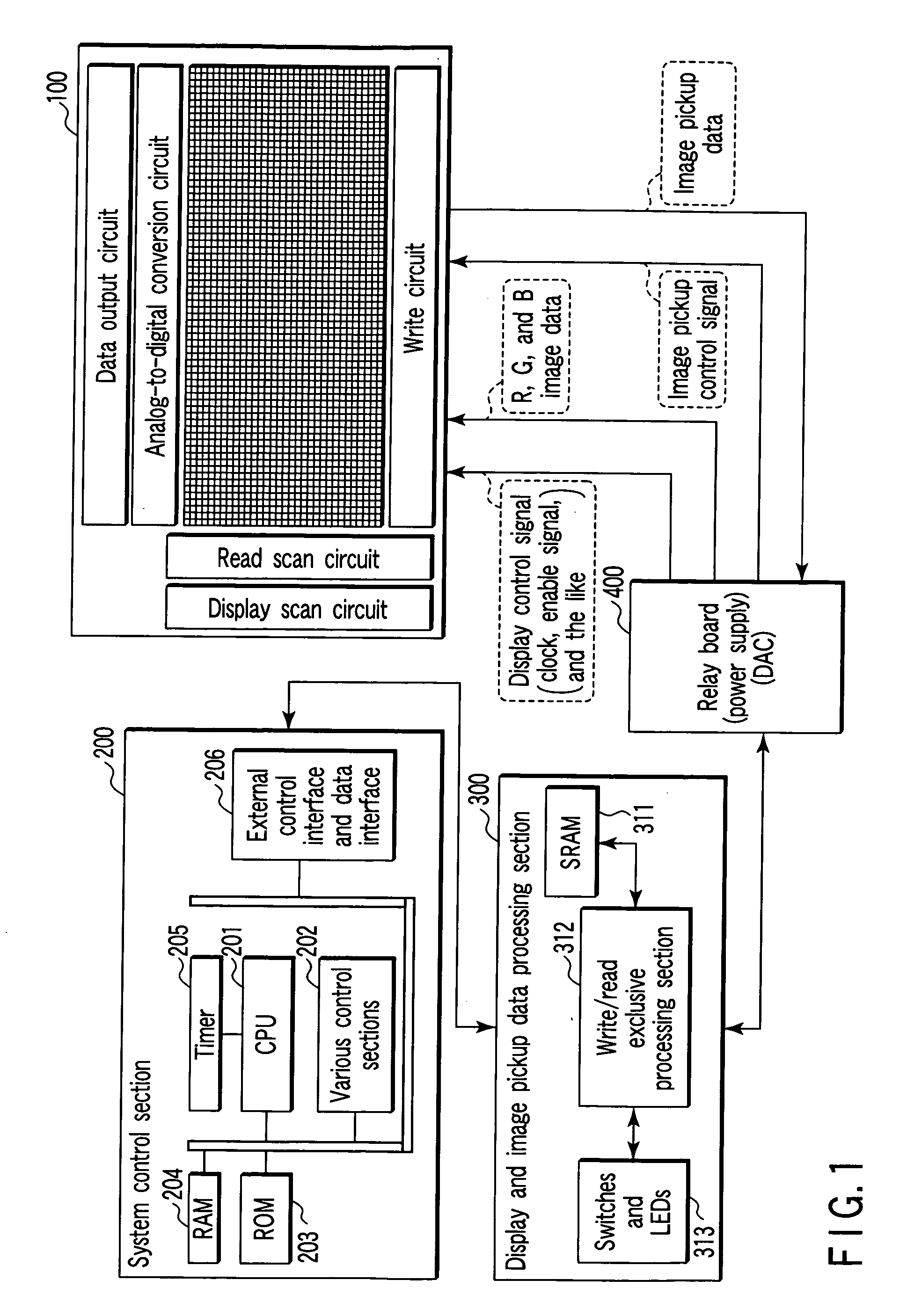

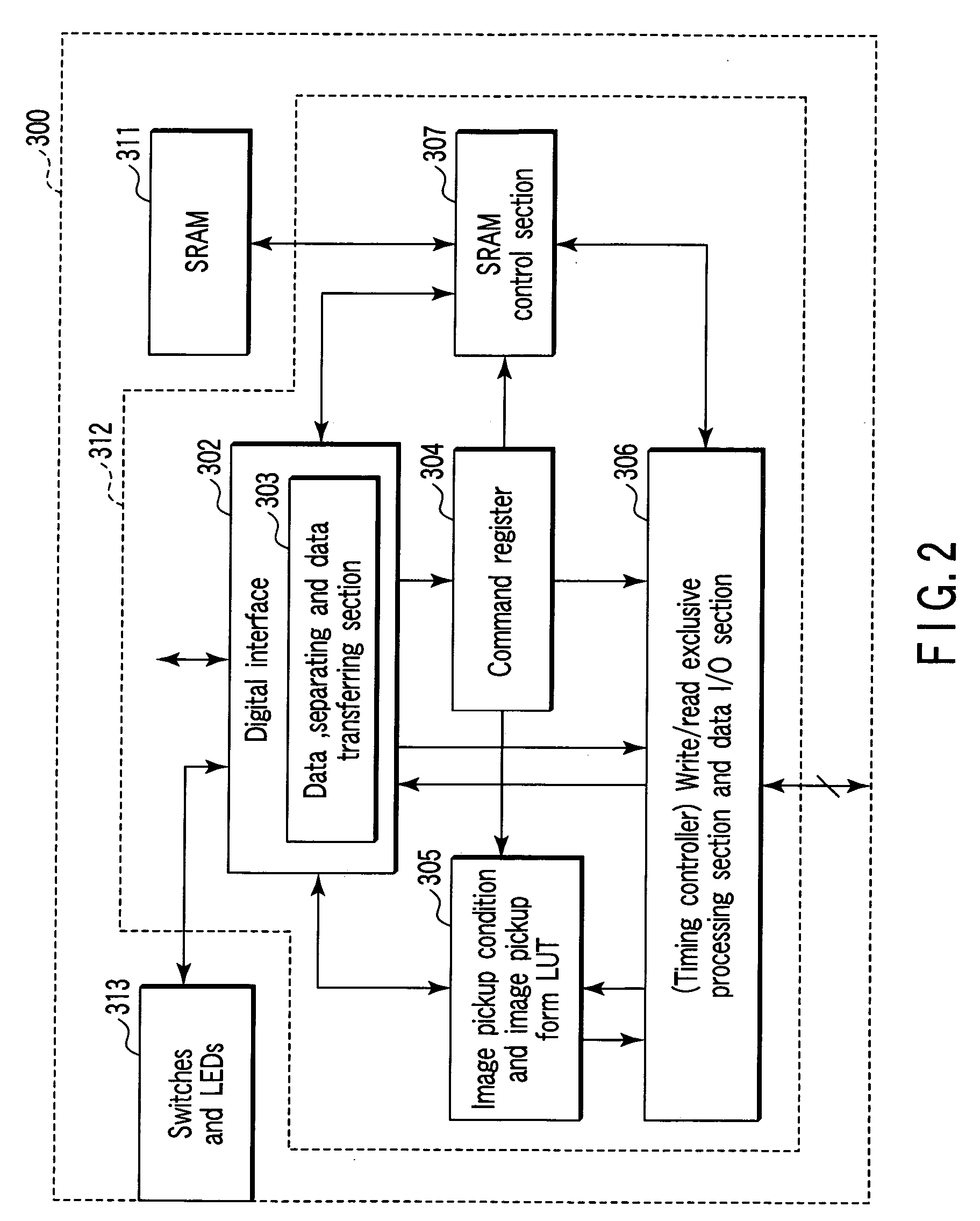

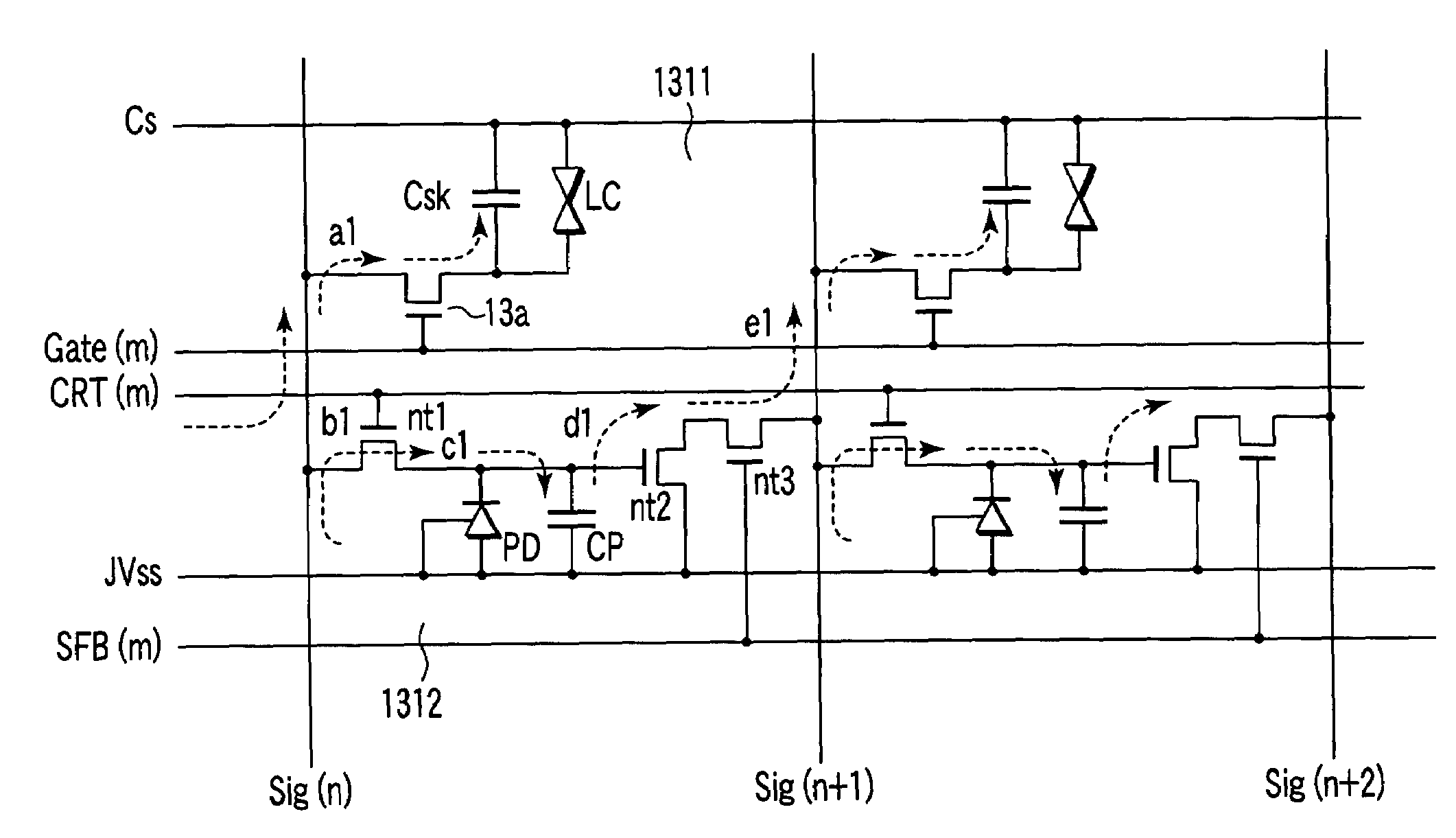

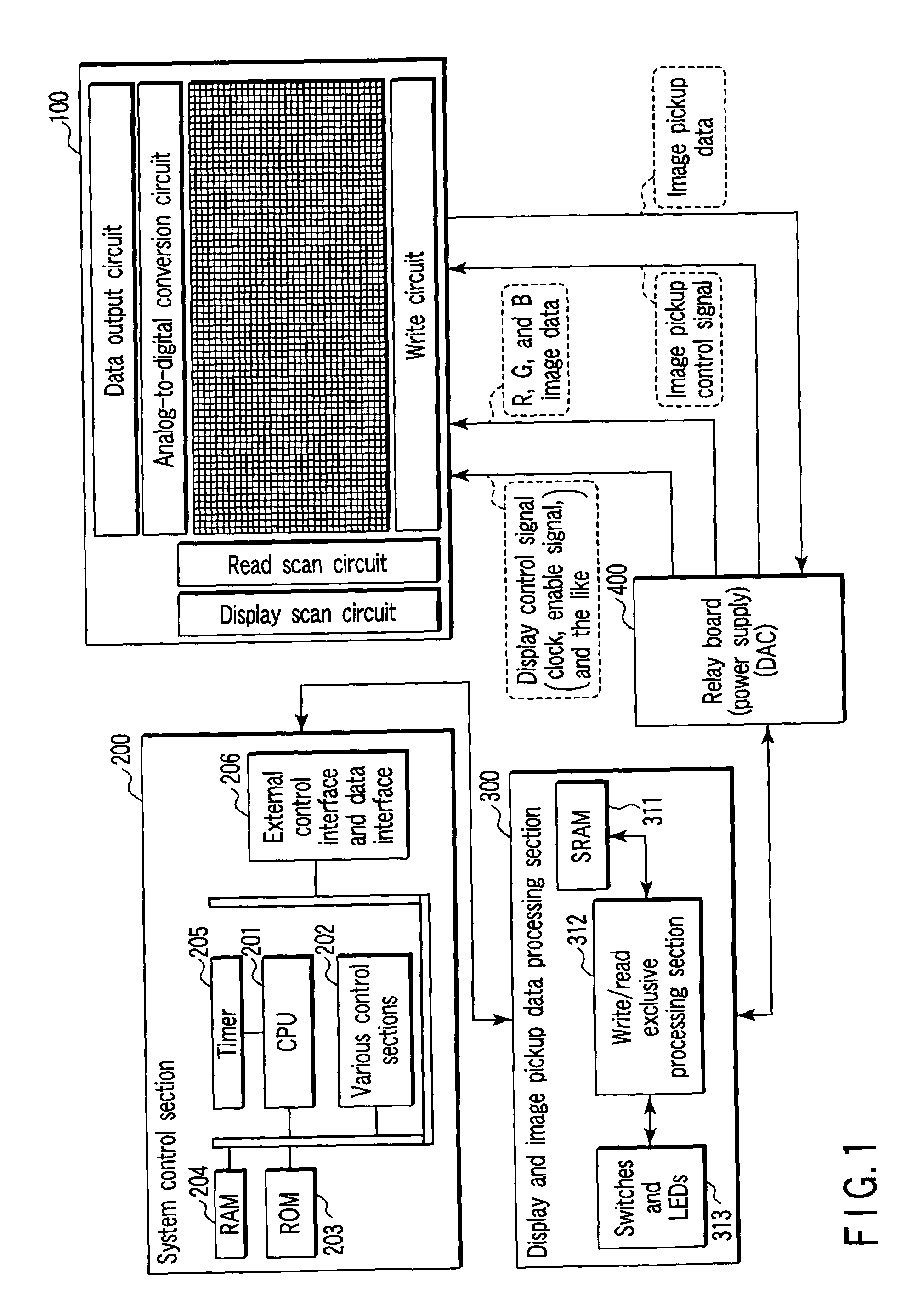

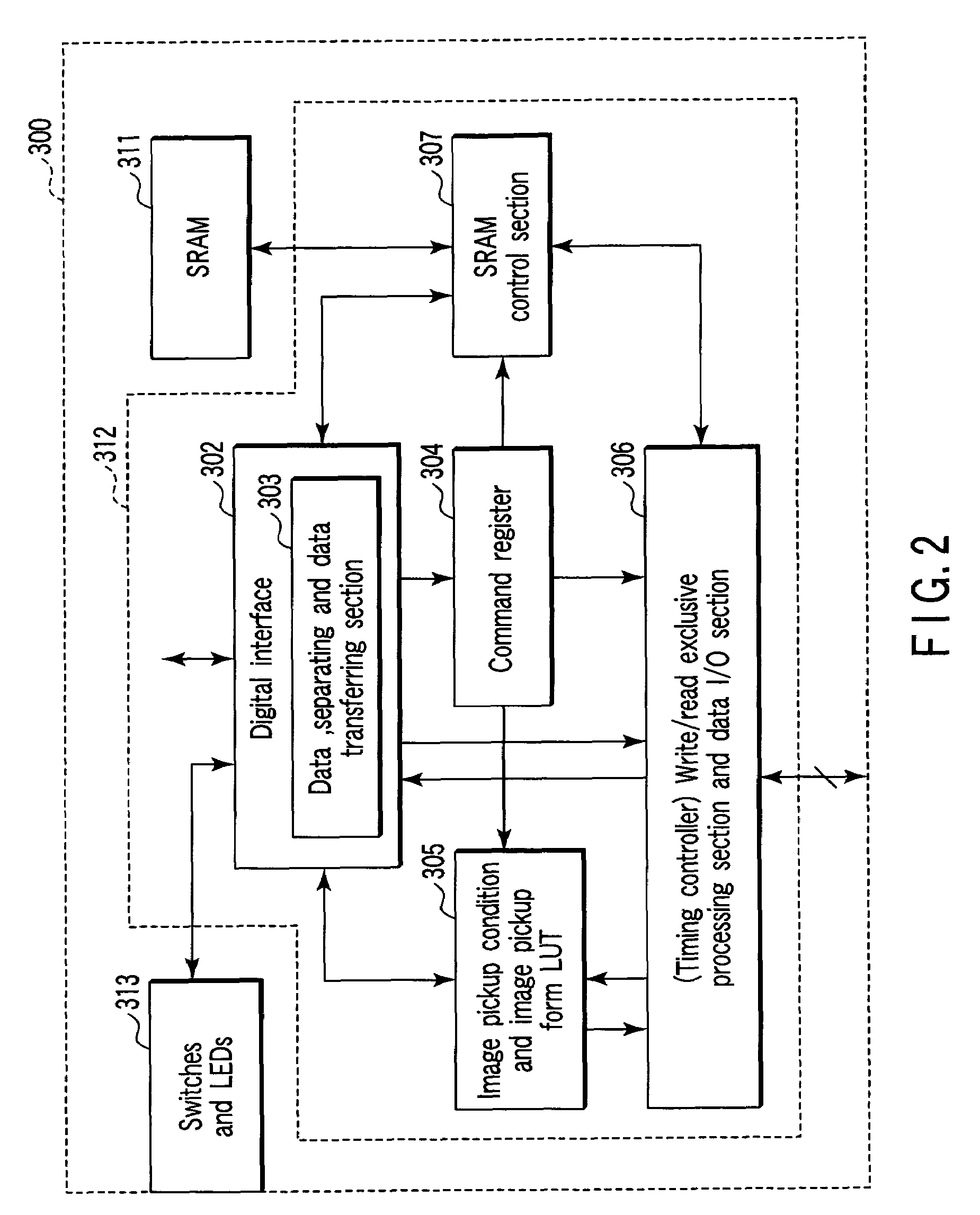

Input sensor containing display device and method for driving the same

ActiveUS20050212916A1Effectively displaying dataData processingTelevision system detailsTelevision system scanning detailsData displayDisplay device

The present invention provides a display device containing an input sensor (for example, a photoelectric converting element) which device can efficiently and flexibly process display data, read data, and association data. The display device has a group of pixel circuits arranged in a matrix, a group of optical sensor circuits arranged in a matrix, a display driving circuit which provides a display signal to the display element group and which provides a driving signal to the display element group, a read circuit which identifies an optical sensor to read a sense signal from this optical sensor, and a read signal processing section which processes the sense signal output by the read circuit in accordance with a command. The read signal processing section has an interface section which transfers, when the command requesting execution of an application is set to the interface section, the command to a command register.

Owner:JAPAN DISPLAY CENTRAL CO LTD

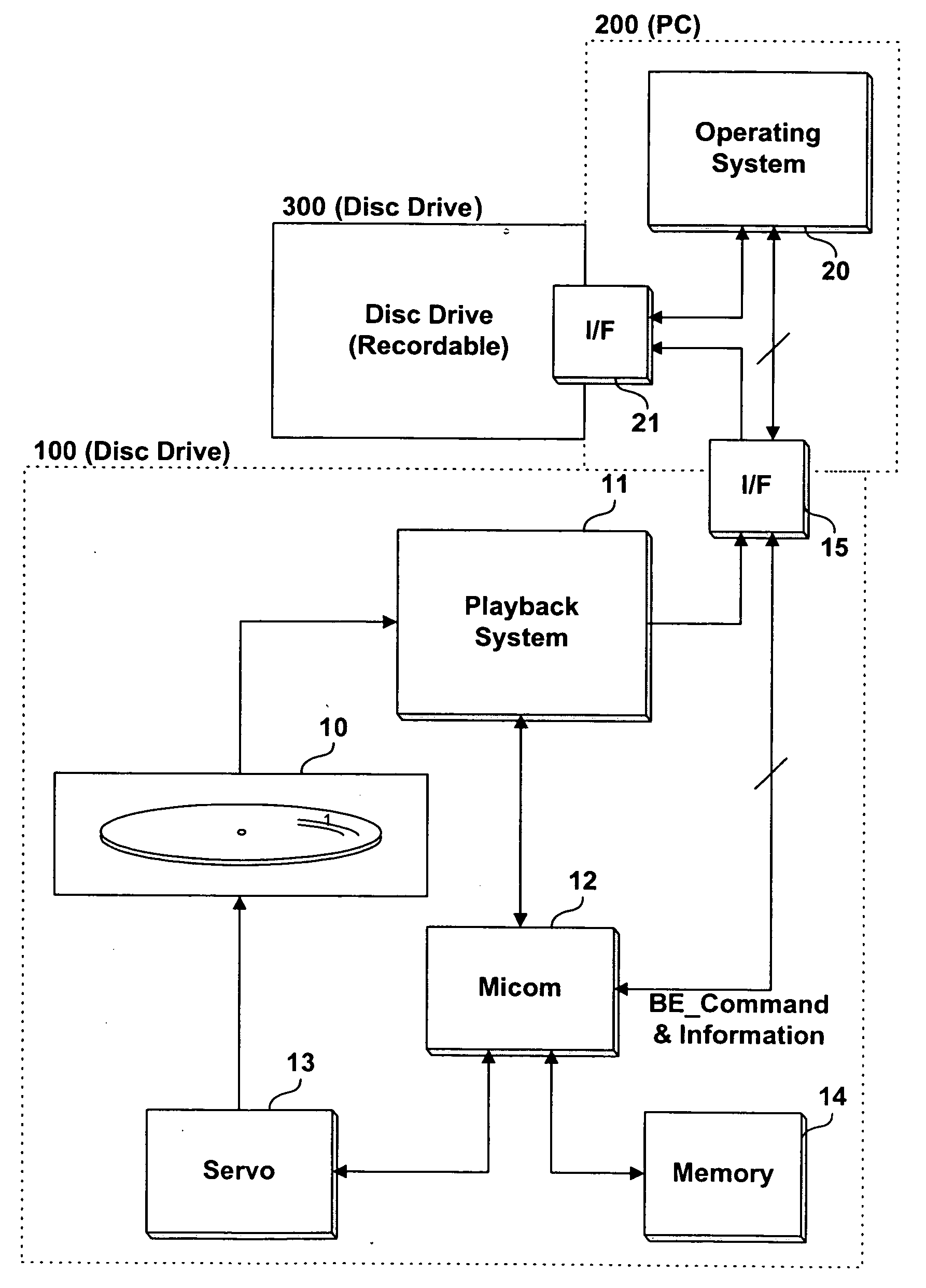

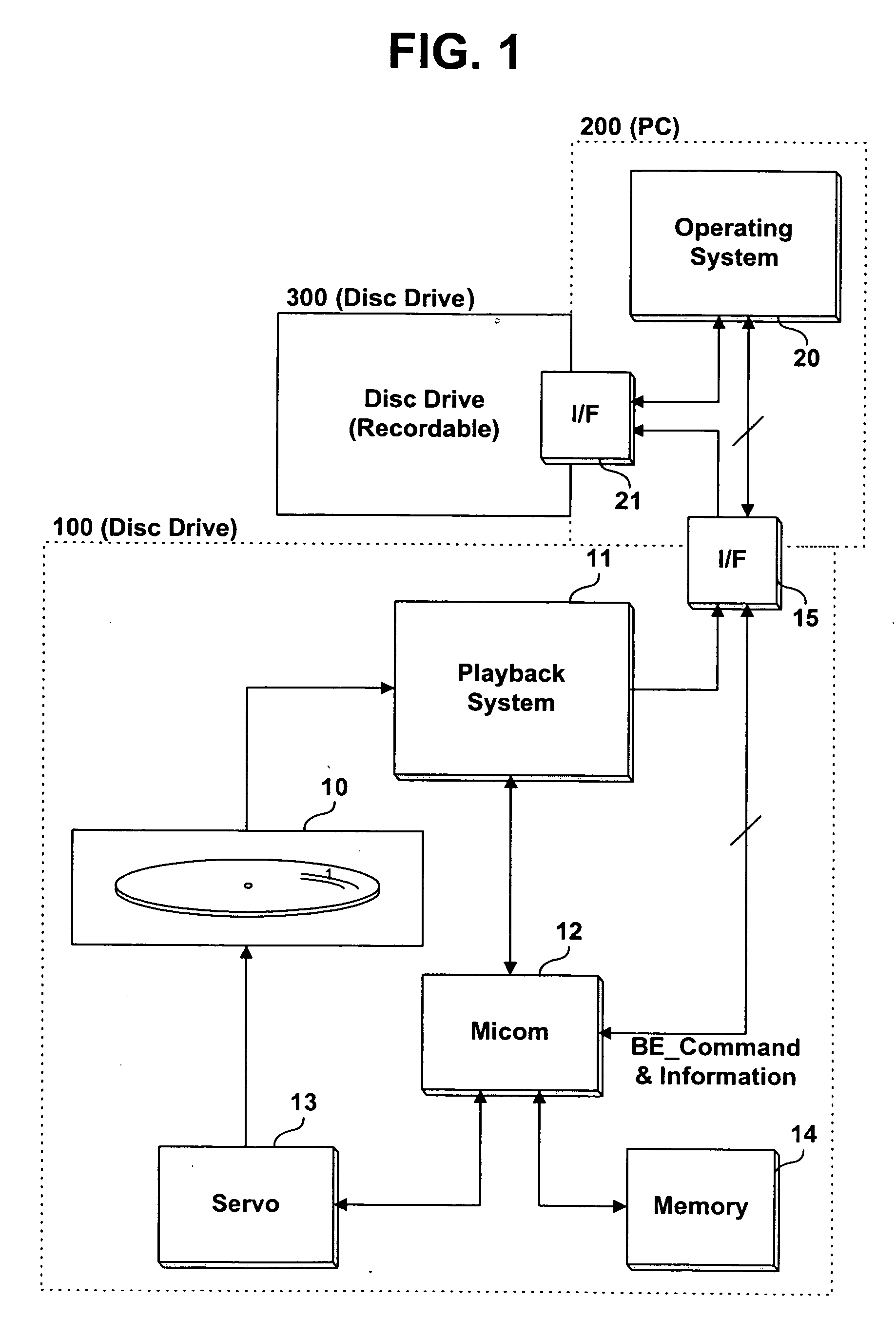

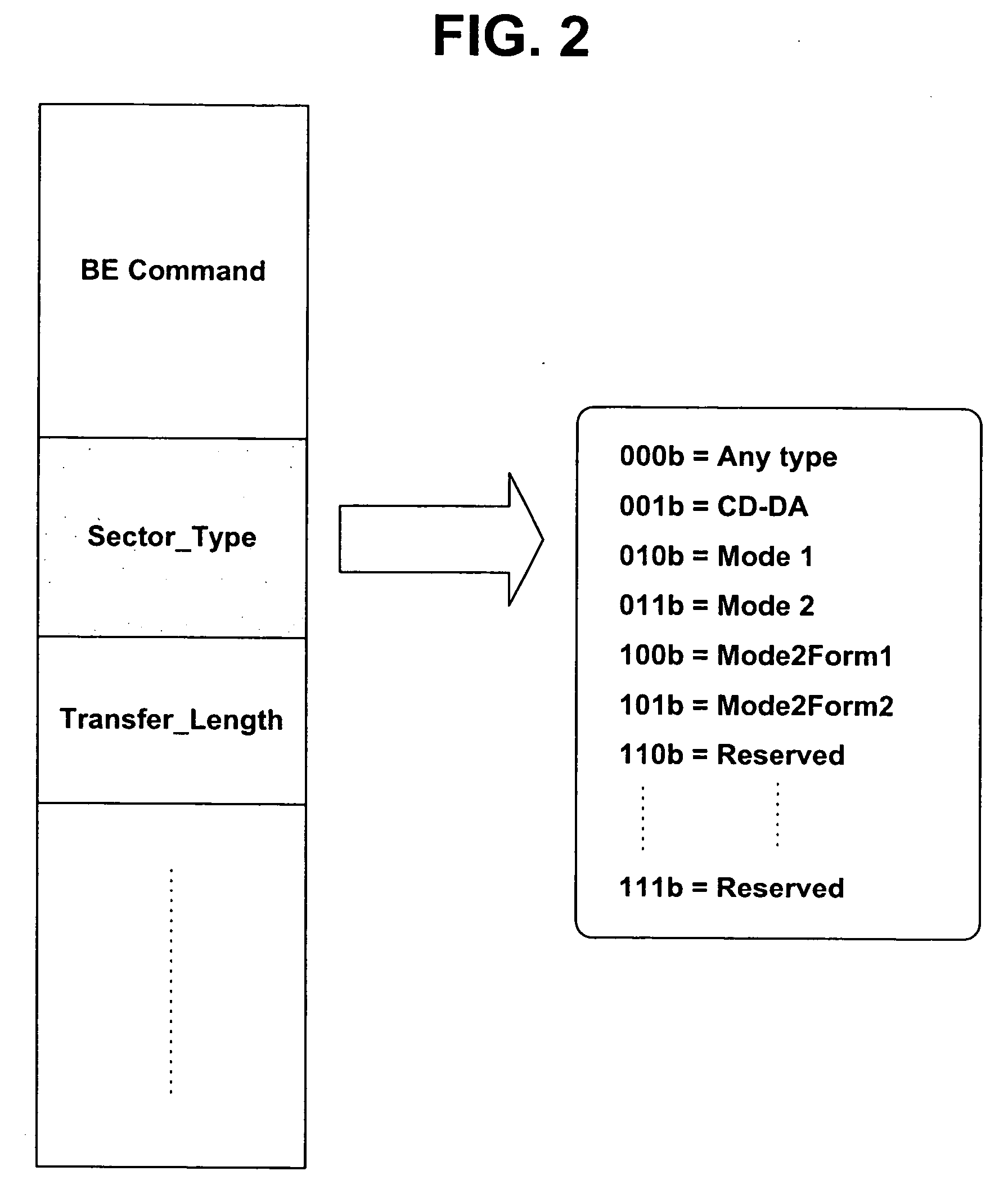

Method for variably controlling data read speed in optical disc drive

InactiveUS20050105885A1Shorten the time periodImprove data reading speedTelevision system detailsFilamentary/web record carriersComputer hardwareOptical disc drive

A method is provided for variably controlling a data read speed in an optical disc drive. The method includes determining whether or not a read command has been issued; if the determining step determines that the read command has been issued, examining additional information associated with the read command; and variably controlling a data read speed for an optical disc according to the additional information.

Owner:HITACHI LG DATA STORAGE KOREA

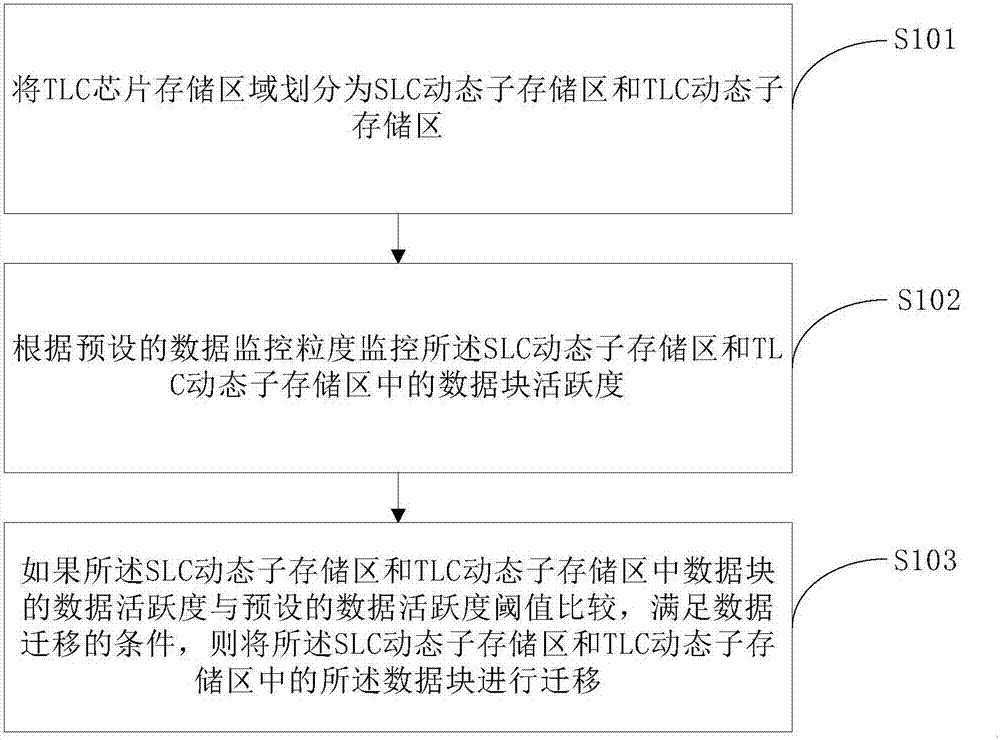

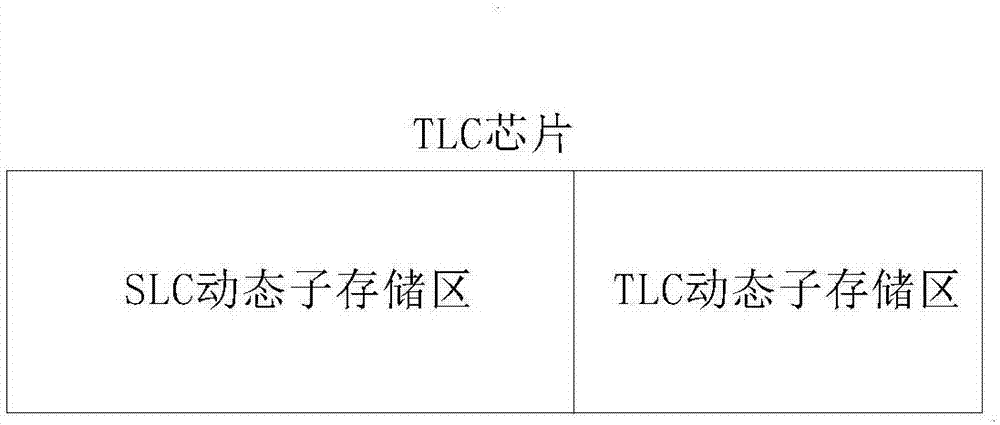

Solid state disk hierarchical storage method and system

InactiveCN107450858AImprove data reading speedIncrease flexibilityInput/output to record carriersData accessSolid-state drive

The embodiment of the invention discloses a solid state disk hierarchical storage method and system. The method includes the steps that a TLC chip storage region is divided into an SLC dynamic sub-storage region and a TLC dynamic sub-storage region; data block activeness in the SLC dynamic sub-storage region and the TLC dynamic sub-storage region is monitored according to preset data monitoring strength; the data activeness of data blocks in the SLC dynamic sub-storage region and the TLC dynamic sub-storage region is compared with a preset data activeness threshold value, and if the data migration condition is met, the data blocks in the SLC dynamic sub-storage region and the TLC dynamic sub-storage region are migrated. The TLC chip is dynamically divided, flexibility of TLC chip storage data is achieved, initial data is stored to the SLC dynamic sub-storage region, along with increase of read-in data, hot data and cold data are stored according to data activeness, data access is directly completed in the SLC dynamic sub-storage region, and therefore data read speed of the TLC chip is increased.

Owner:HUNAN GOKE MICROELECTRONICS

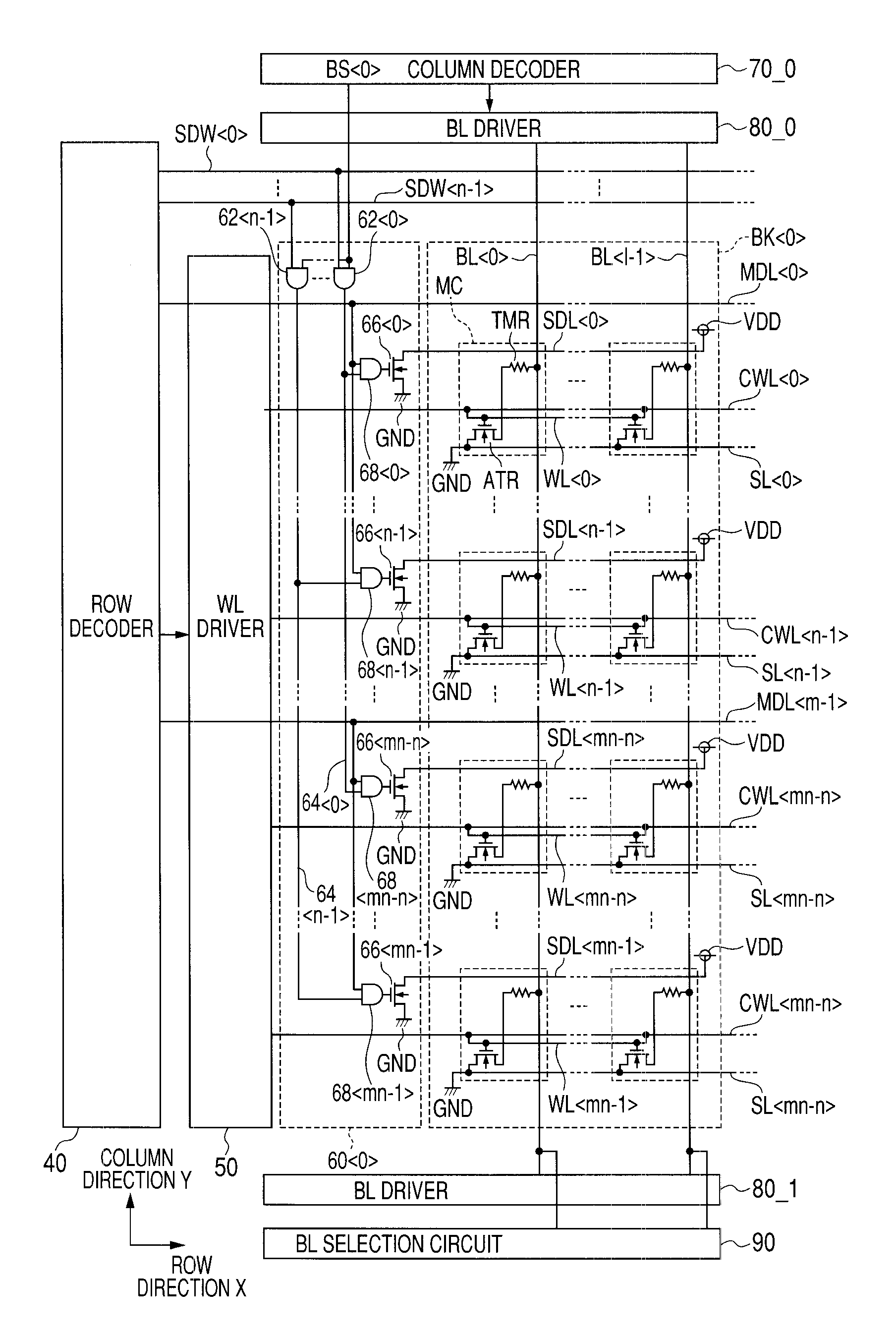

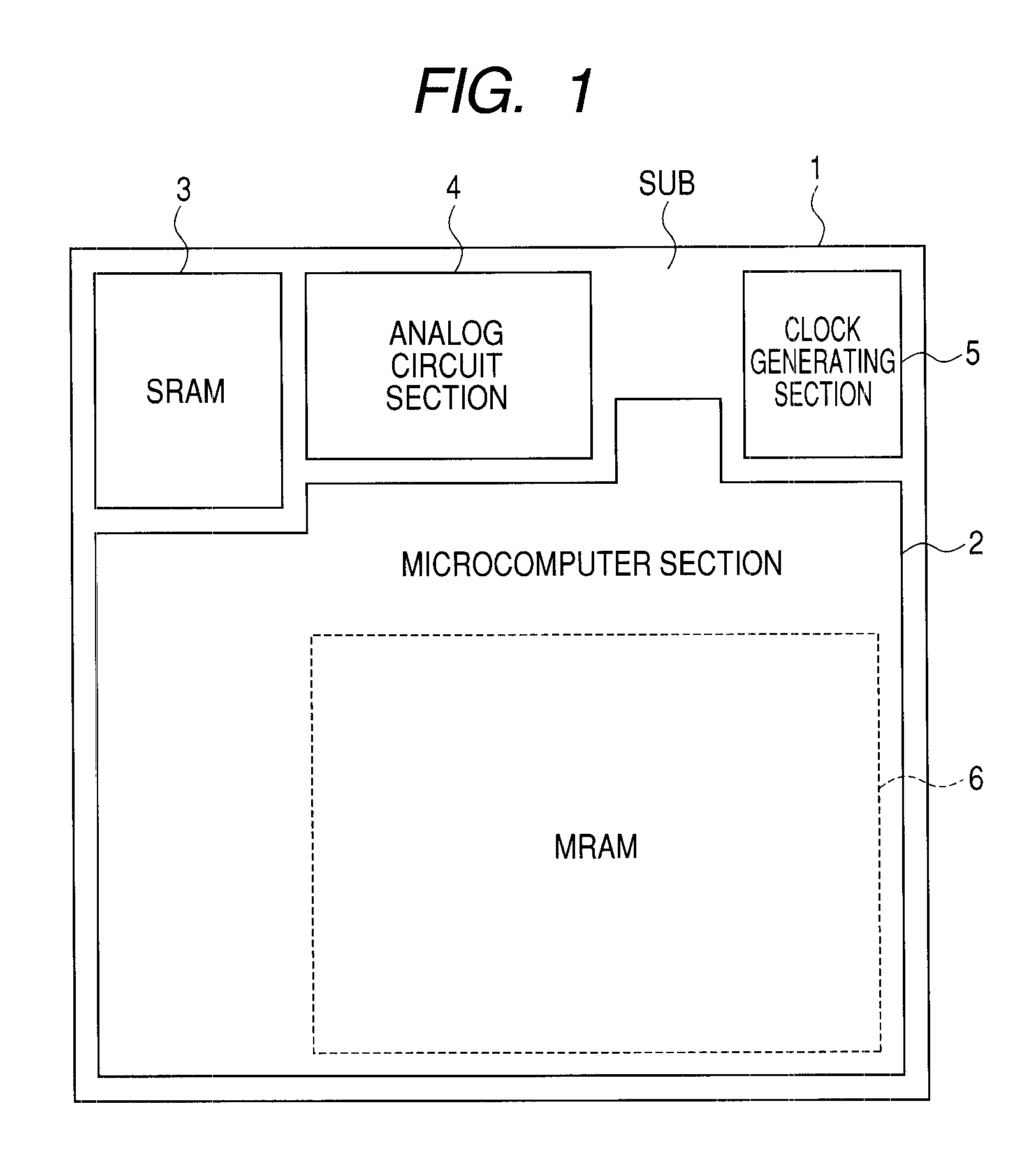

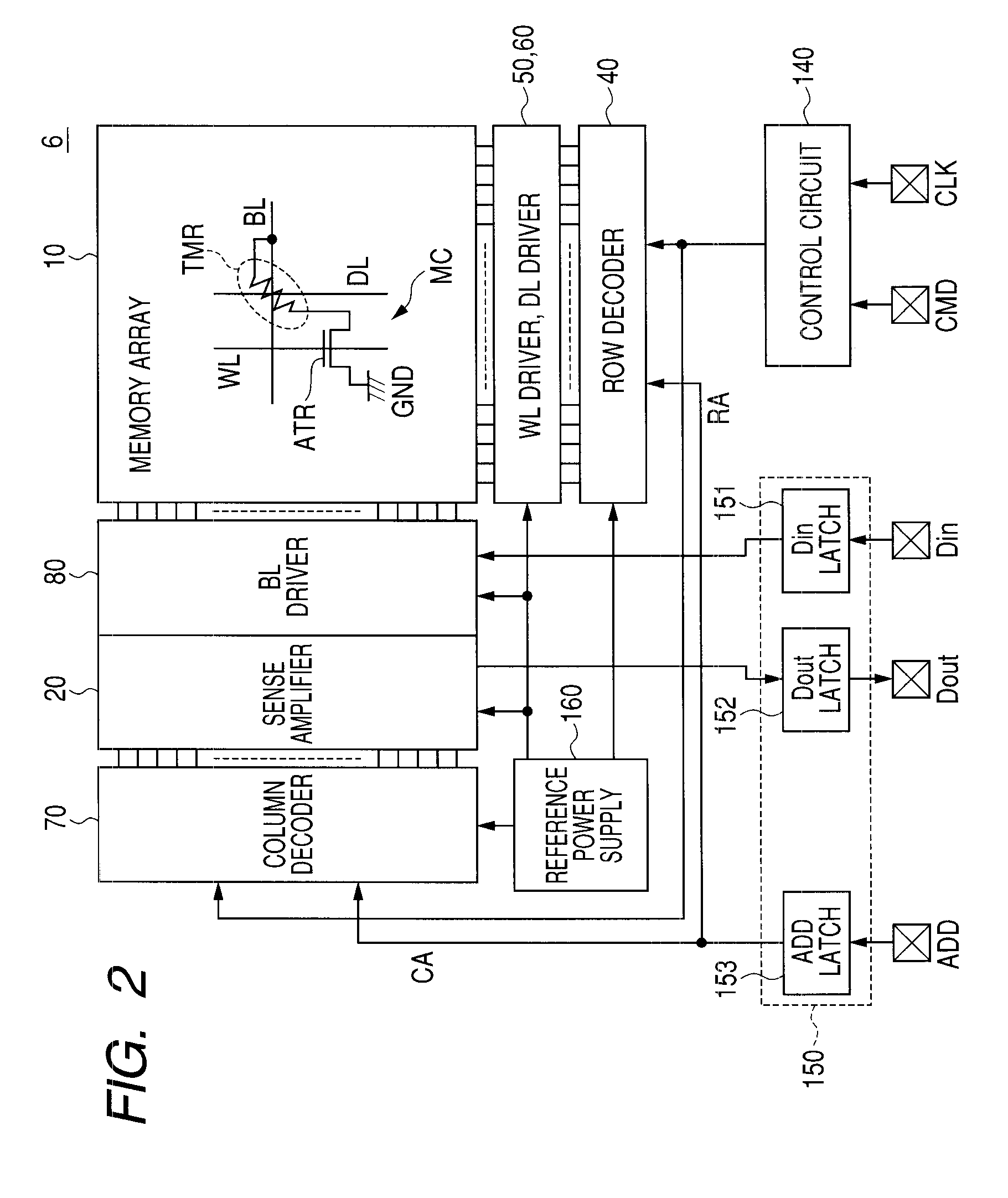

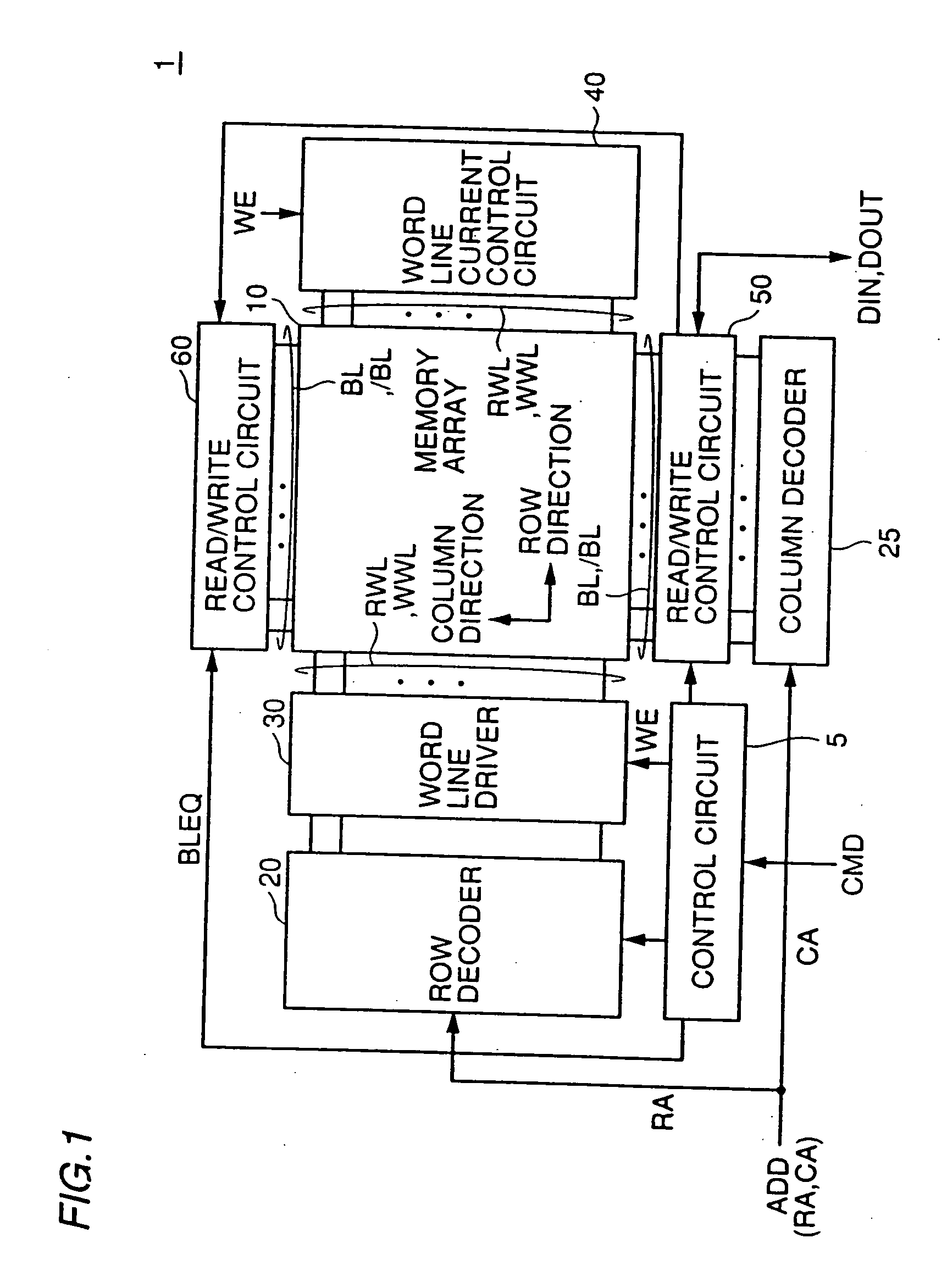

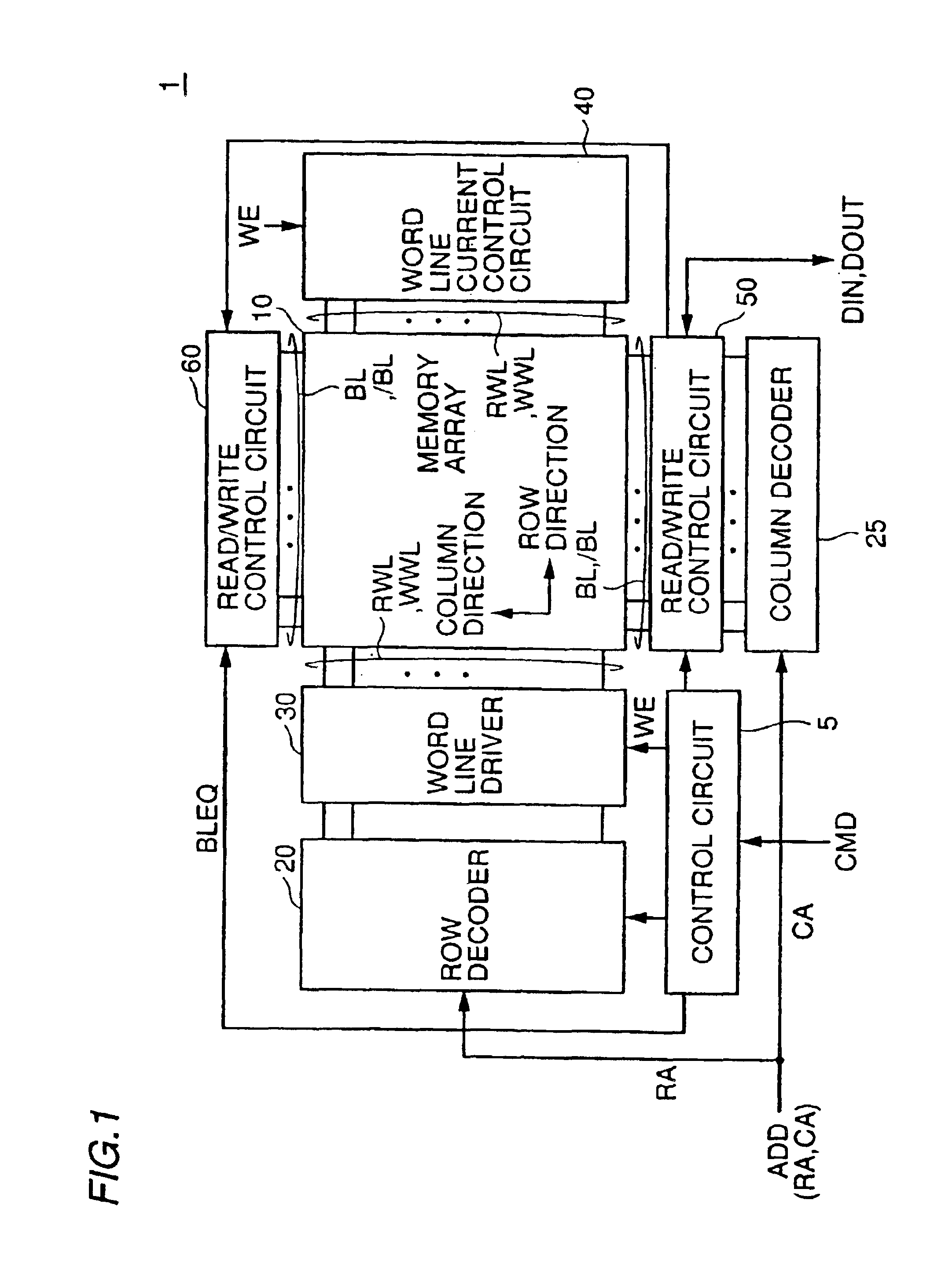

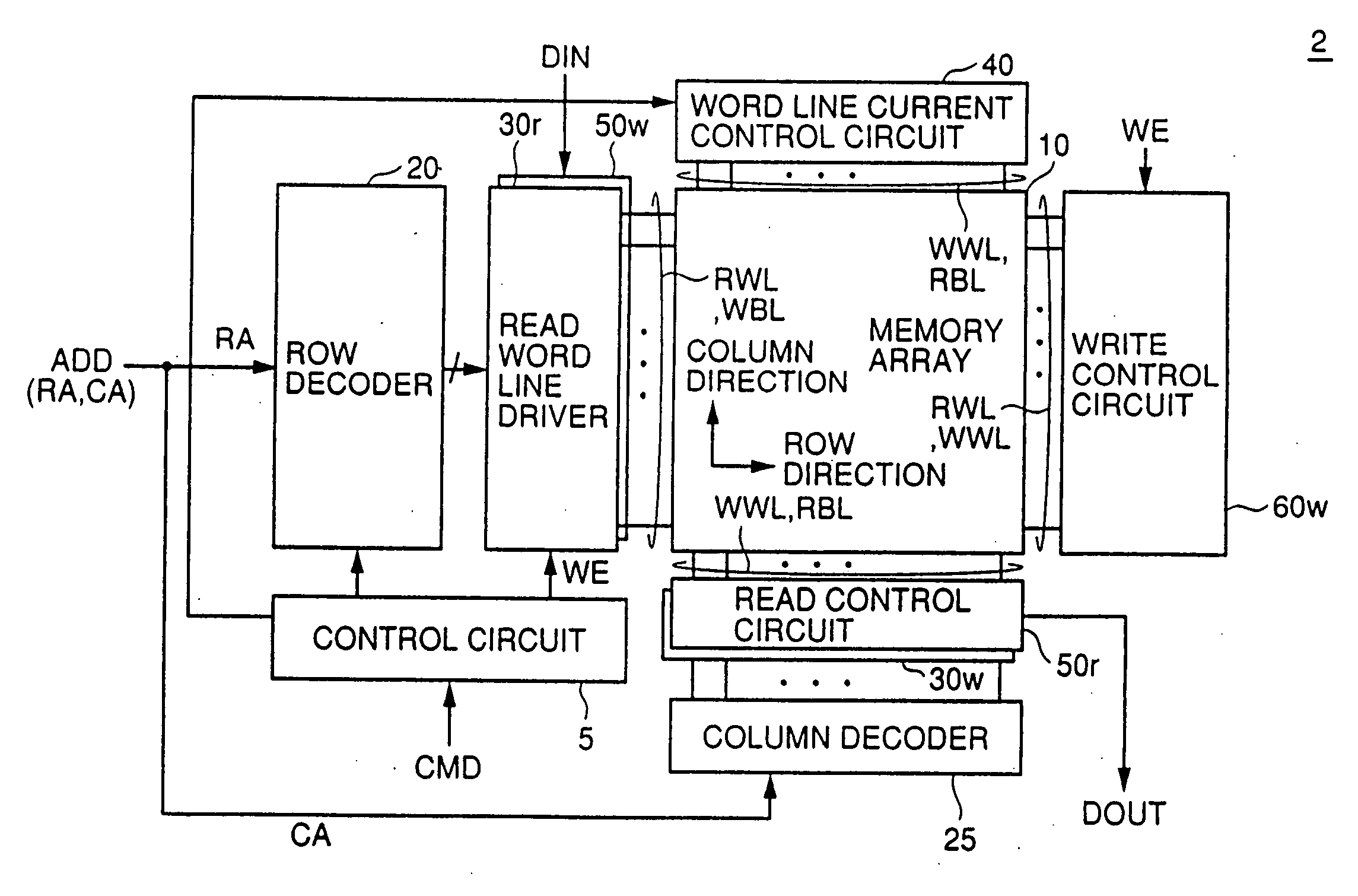

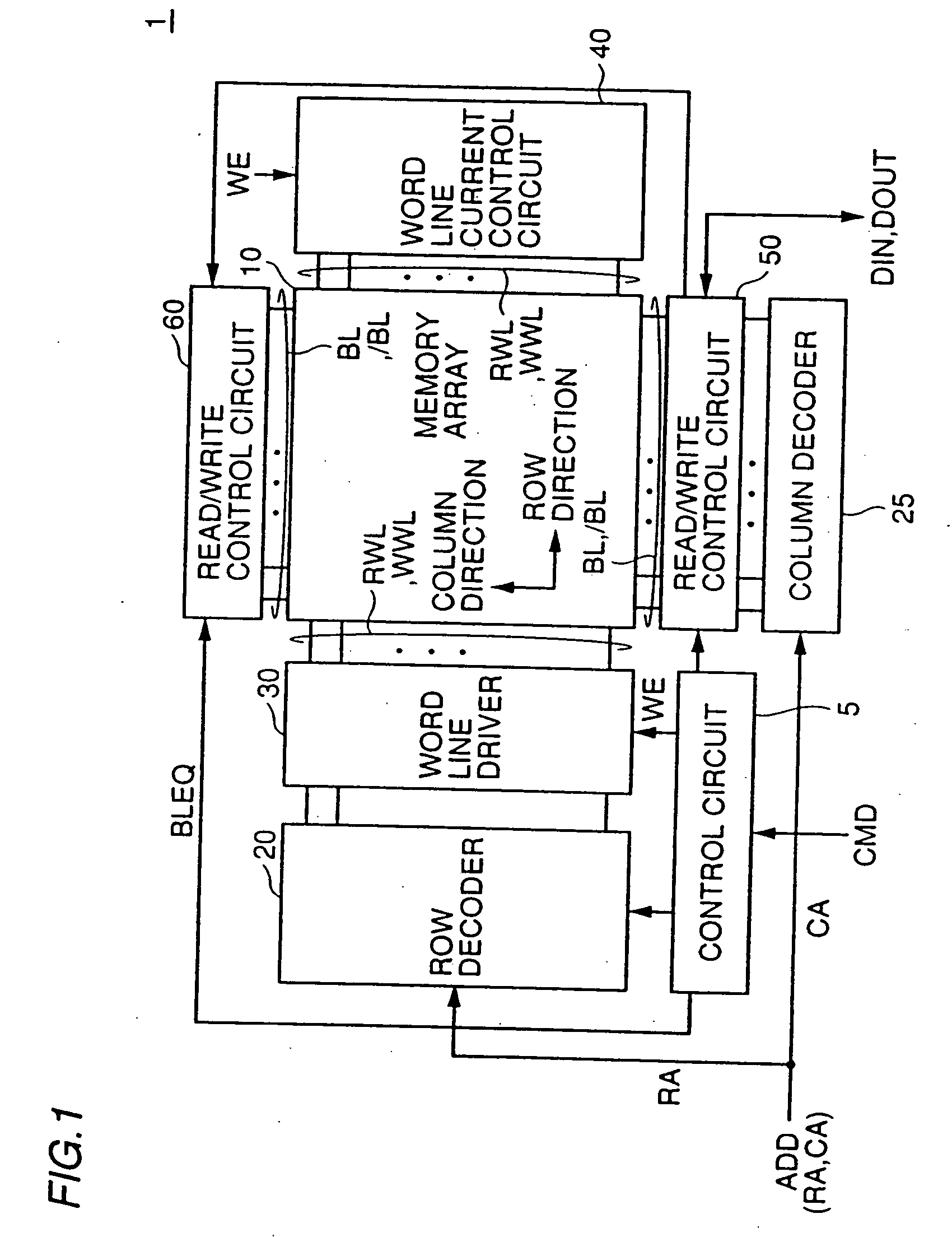

Semiconductor device

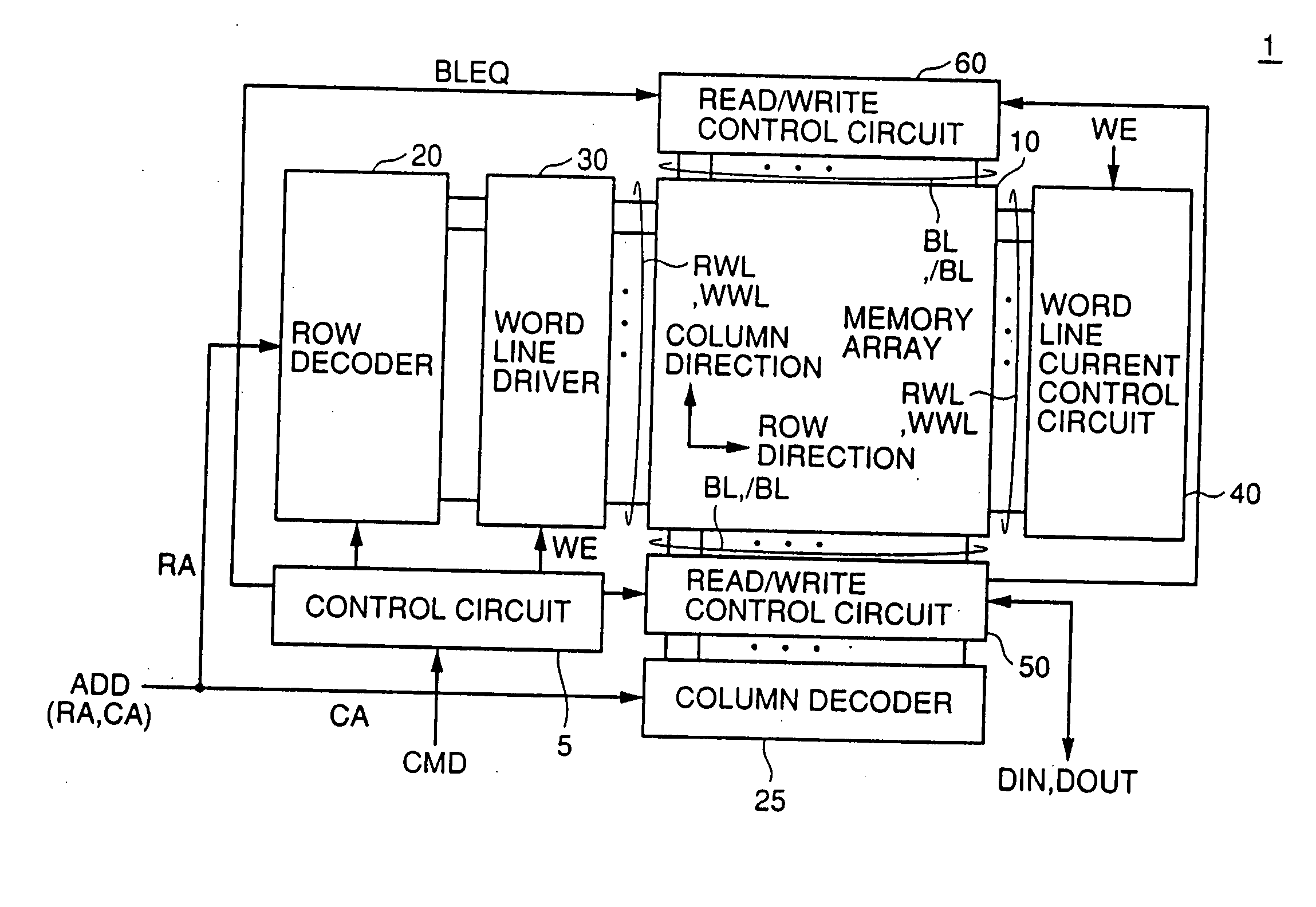

ActiveUS7872907B2Reduce areaHigh-speed data readingSolid-state devicesDigital storagePower semiconductor deviceCommon word

There is provided a semiconductor device that enables high-speed data read and reduces the area of a drive circuit for activating a word line. By signal transmission through a common word line having a low resistance and coupled at a plurality of points to a word line, it is possible to read data at high speed. Further, since the common word line is provided common to a plurality of memory blocks, a word line driver can be provided common to the memory blocks. Further, by disposing a latch circuit, corresponding to a sub-digit line, for holding the active state of the common word line, it is possible to transmit a row selection signal during data write through the common word line and thereby reduce a metal wiring layer.

Owner:RENESAS ELECTRONICS CORP

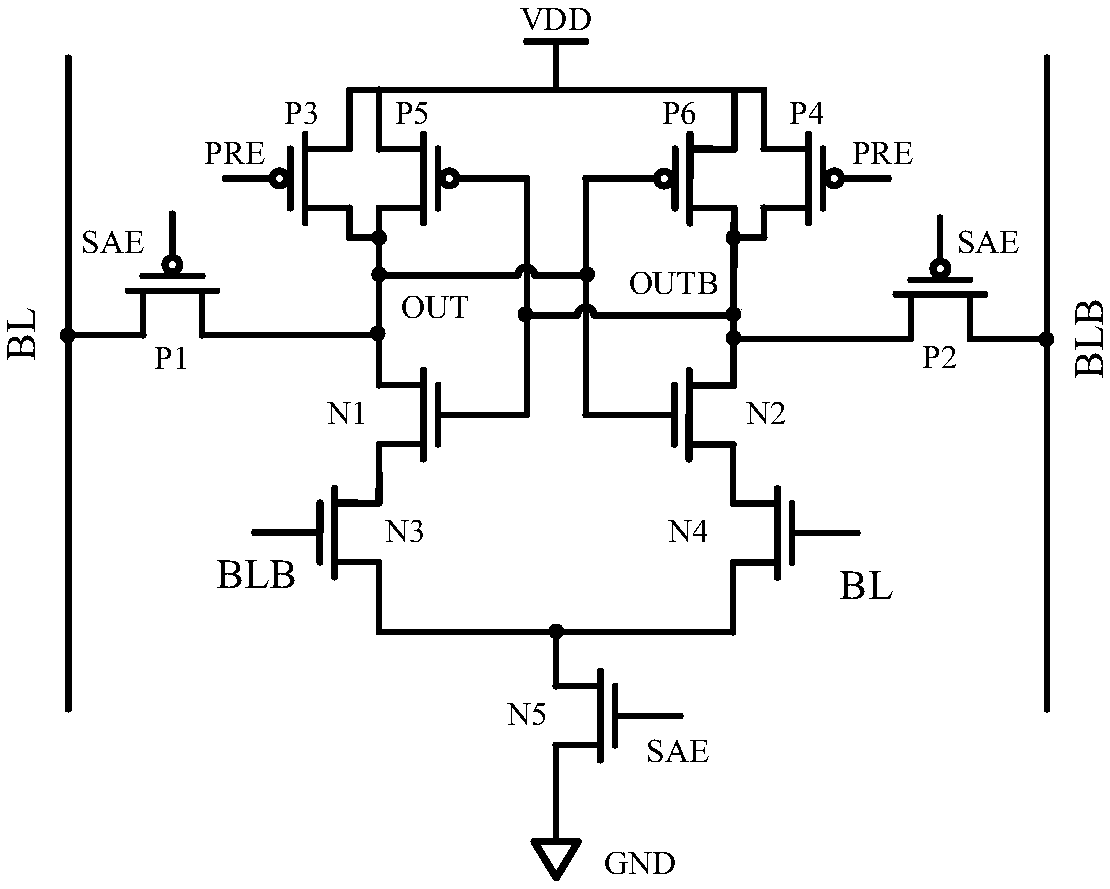

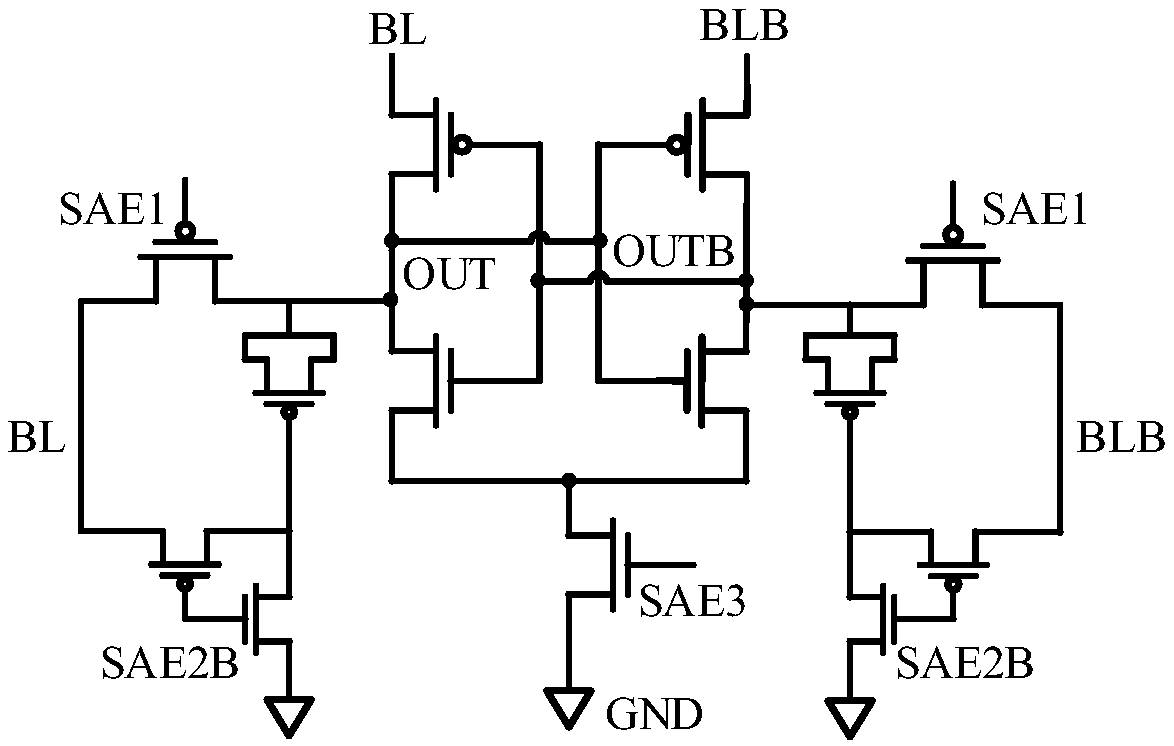

Current-Sense Amplifier With Low-Offset Adjustment and Method of Low-Offset Adjustment Thereof

ActiveUS20120294090A1Lower Input Offset VoltageIncreased memory data read speedCurrent/voltage measurementRead-only memoriesElectricityAudio power amplifier

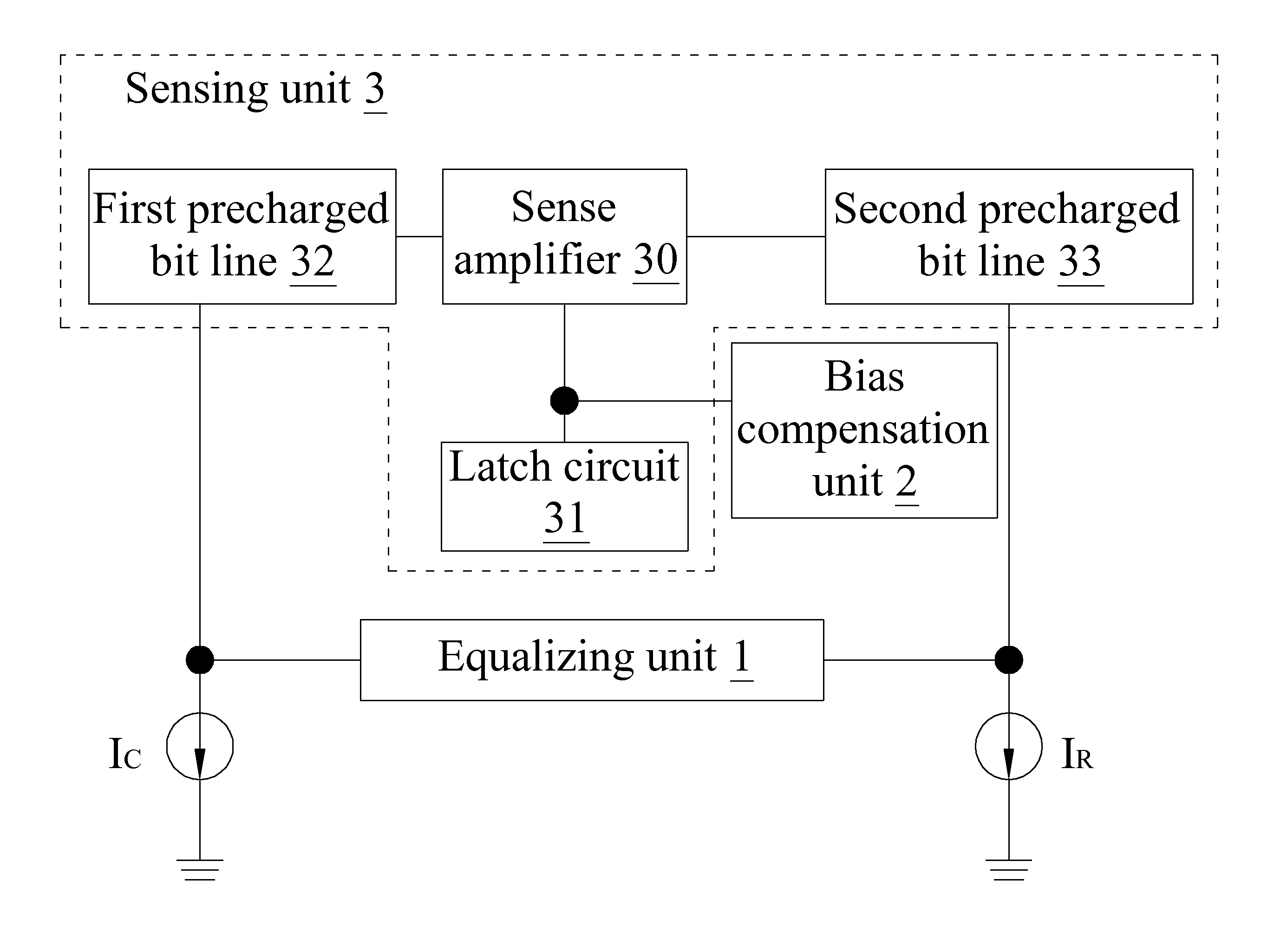

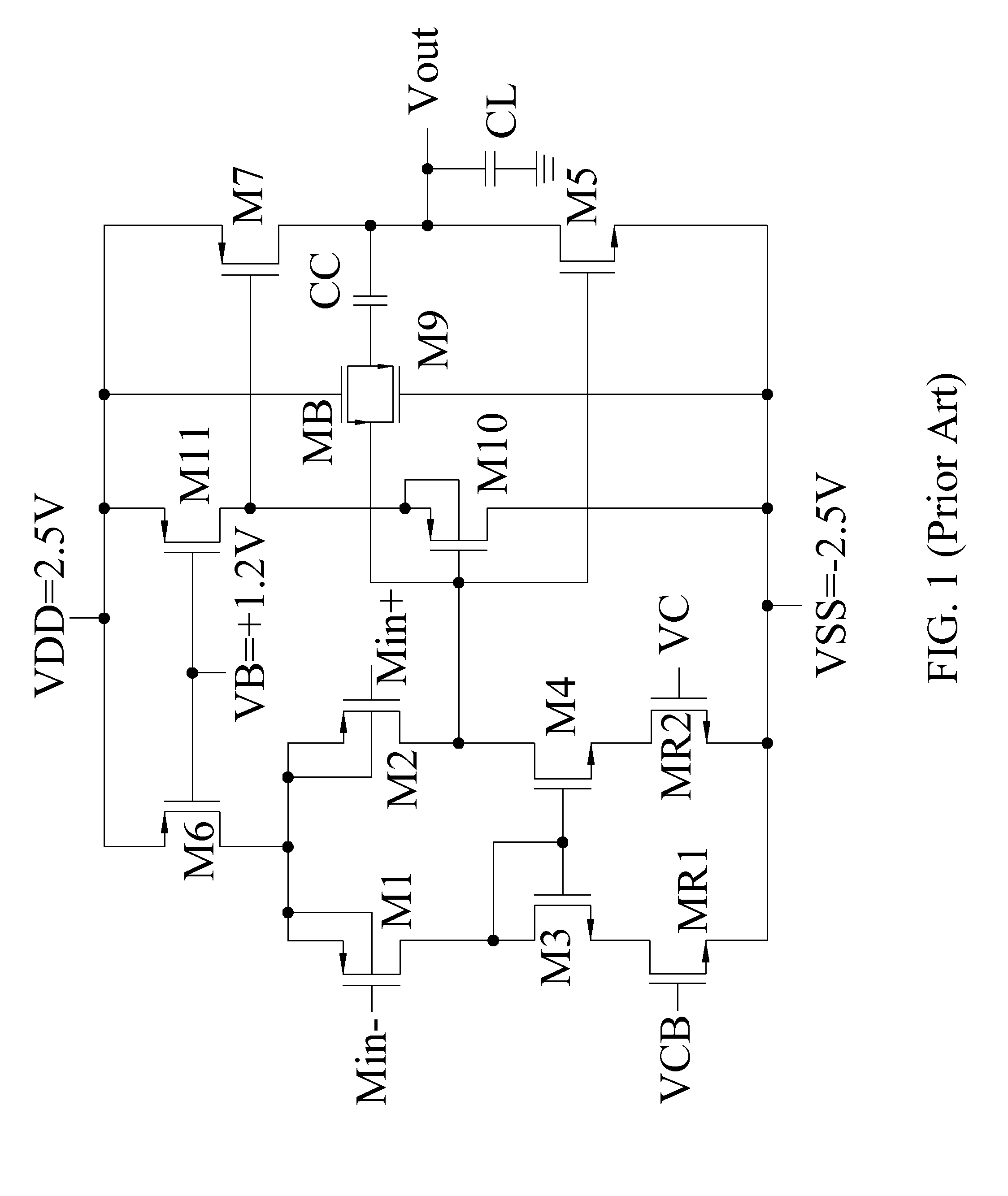

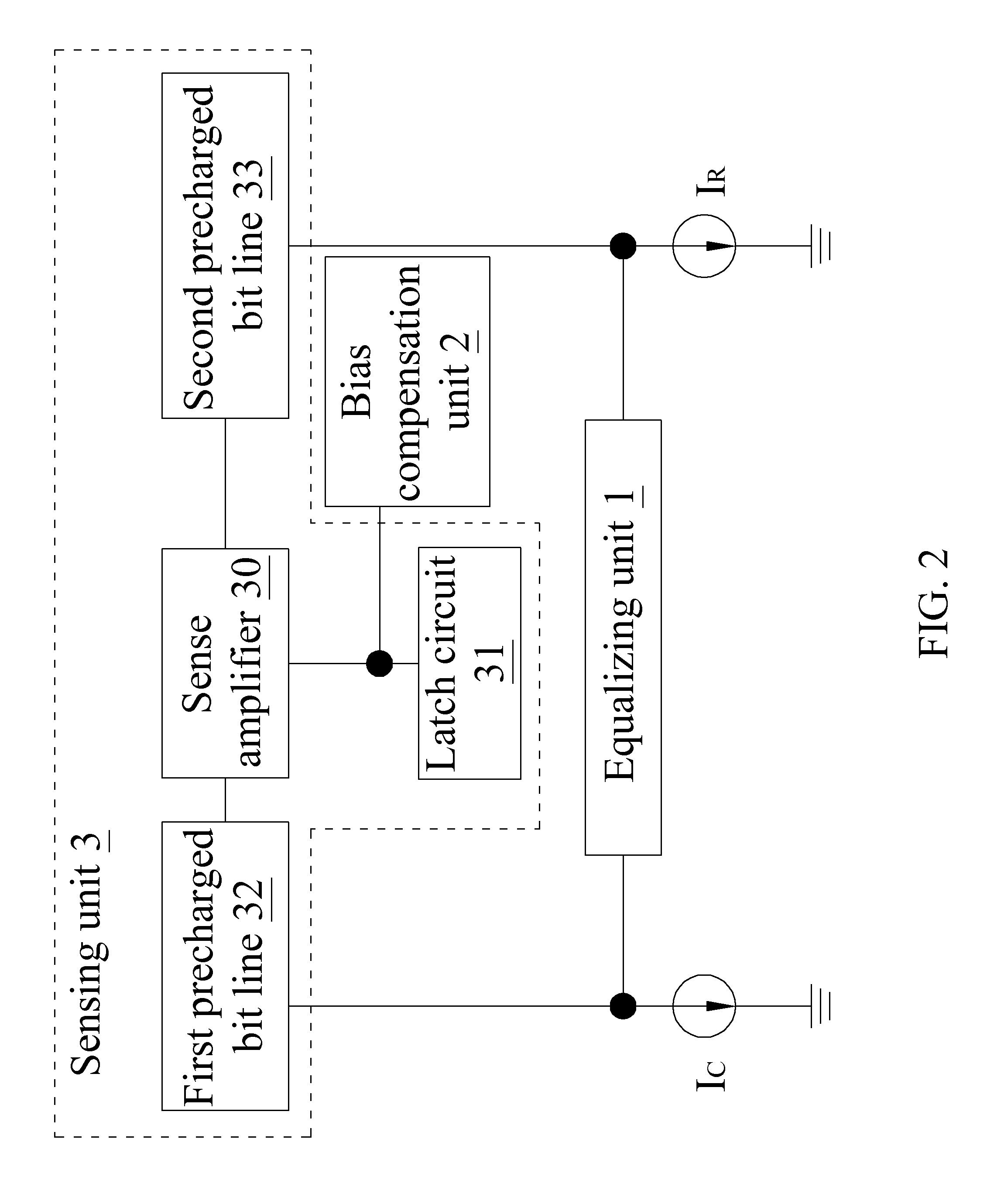

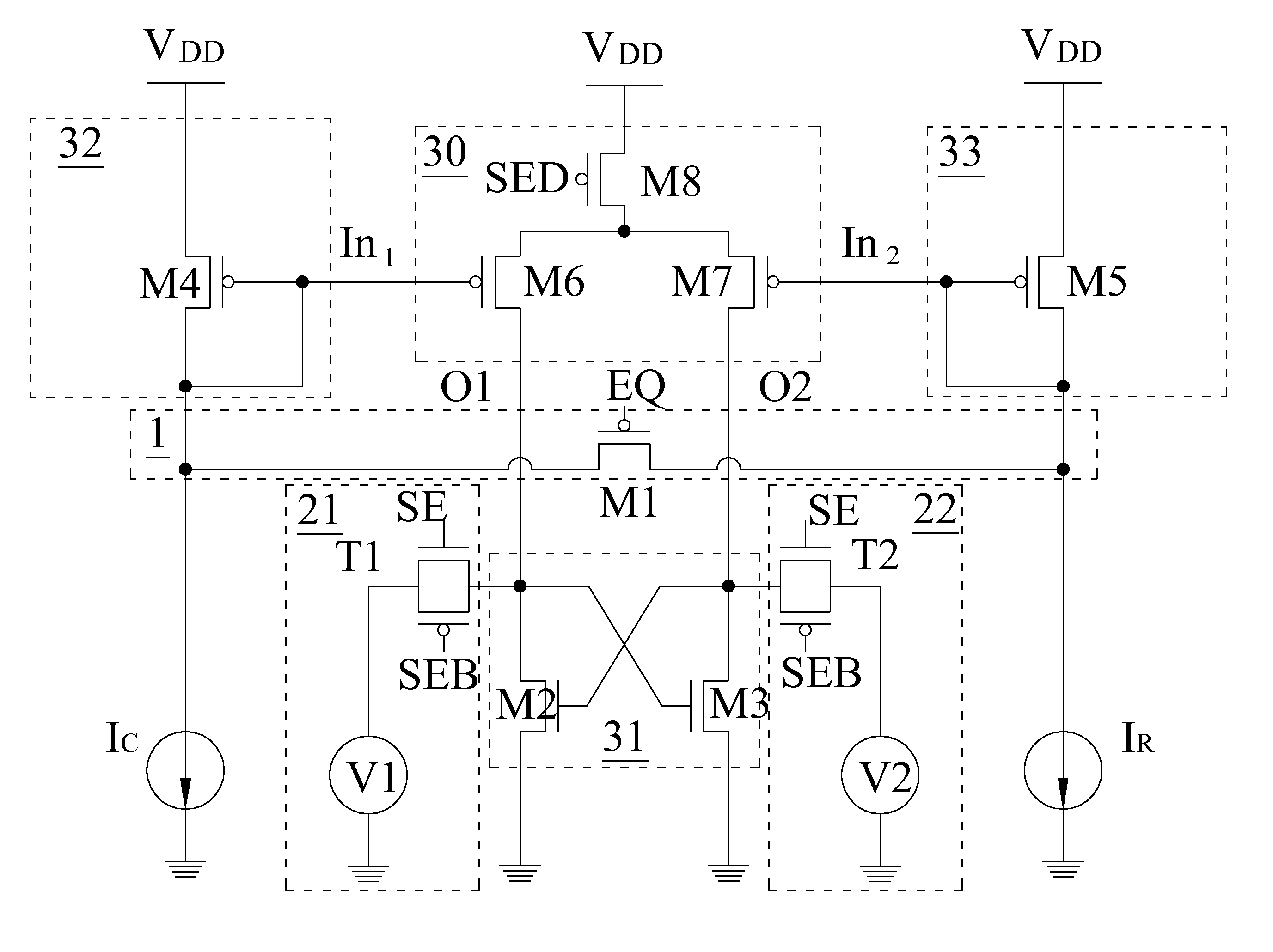

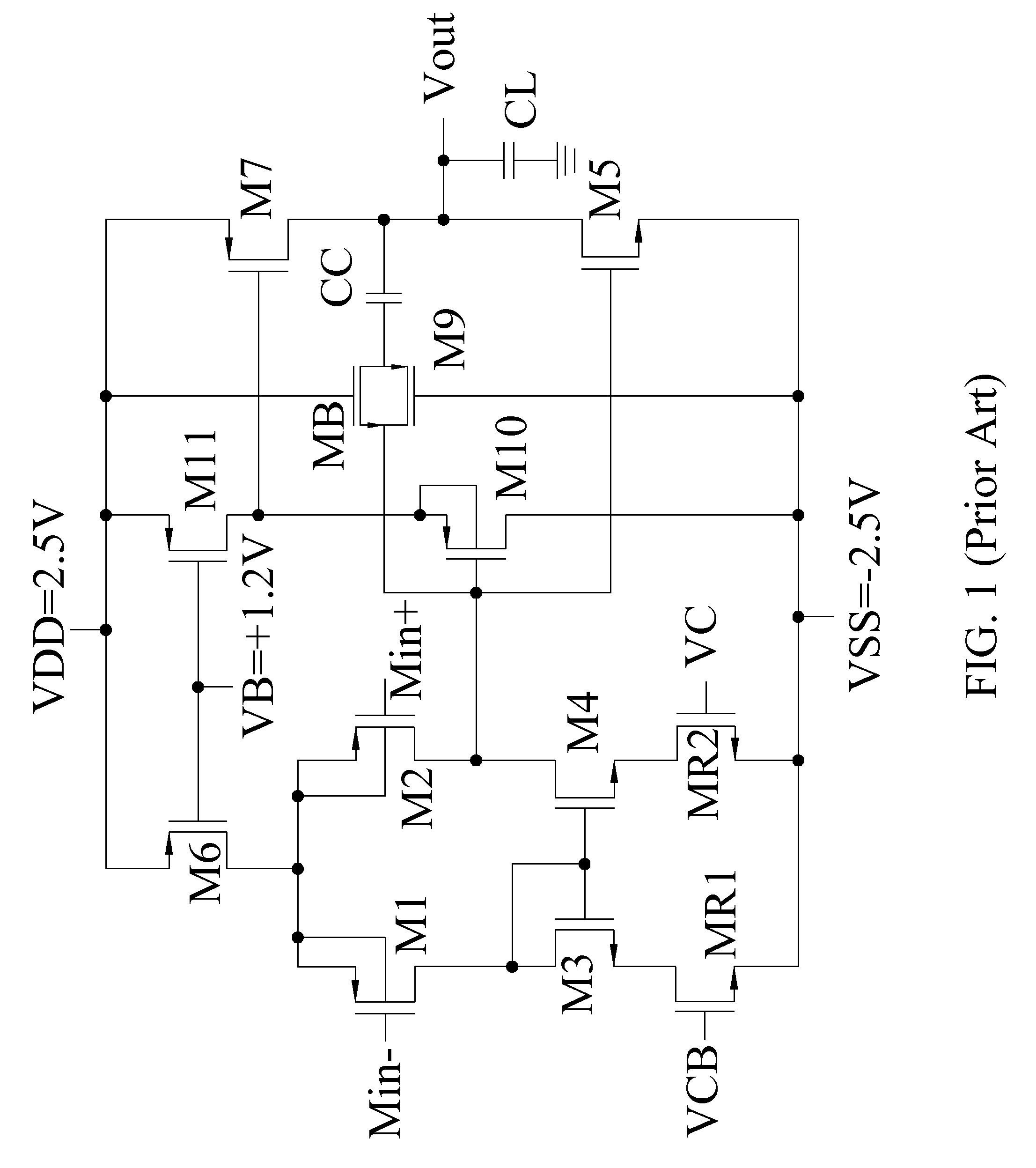

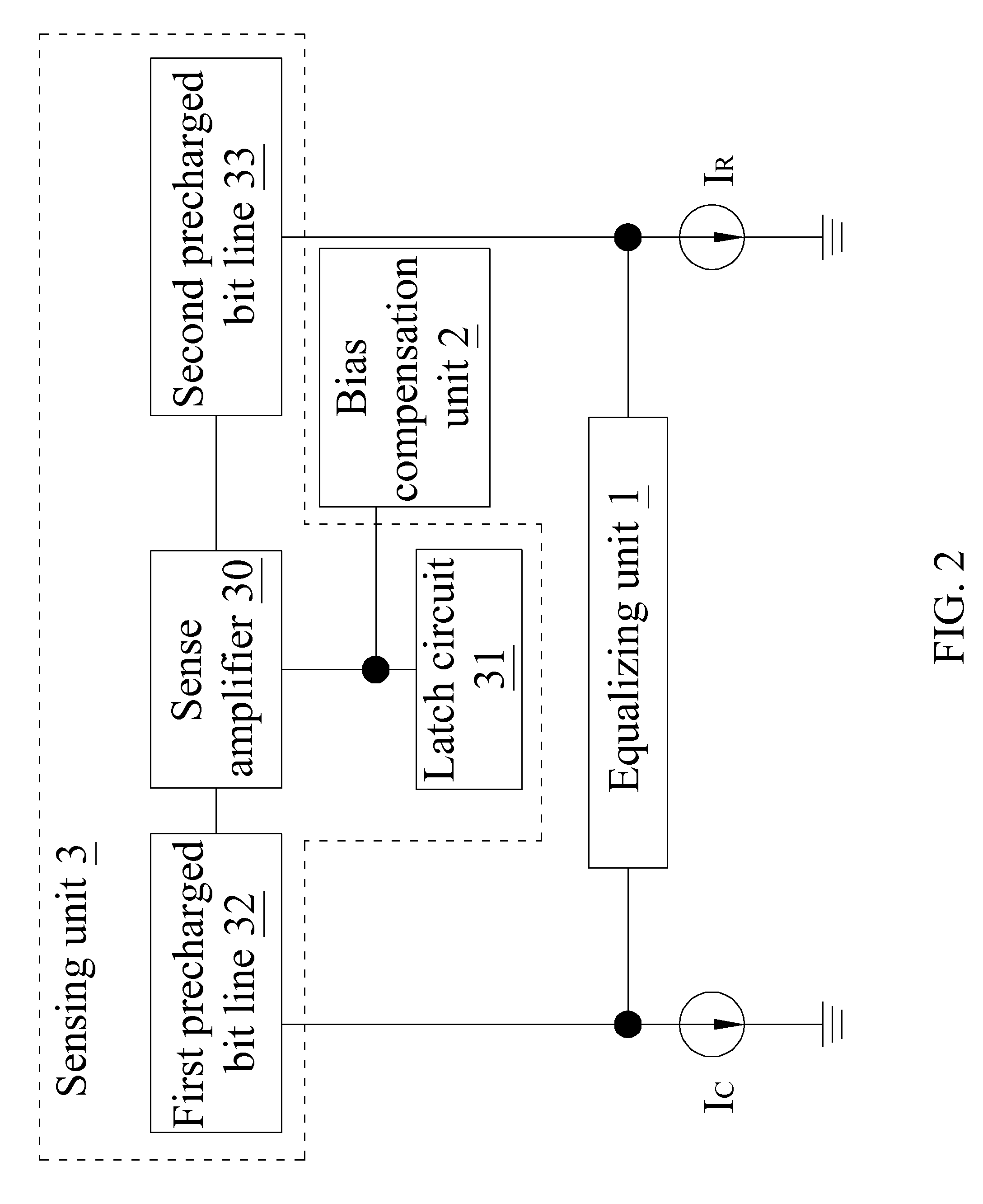

A current-sense amplifier with low-offset adjustment and a low-offset adjustment method thereof are disclosed. The current-sense amplifier includes a sensing unit, an equalizing unit and a bias compensation unit. The sensing unit includes a sense amplifier, a latch circuit, a first precharged bit line, and a second precharged bit line. The equalizing unit is electrically connected to the first and the second precharged bit line for regulating a voltage of the first precharged bit line and a voltage of the second precharged bit line to the same electric potential. The bias compensation unit is electrically connected to the sense amplifier for compensating an input offset voltage of the current-sense amplifier.

Owner:NATIONAL TSING HUA UNIVERSITY

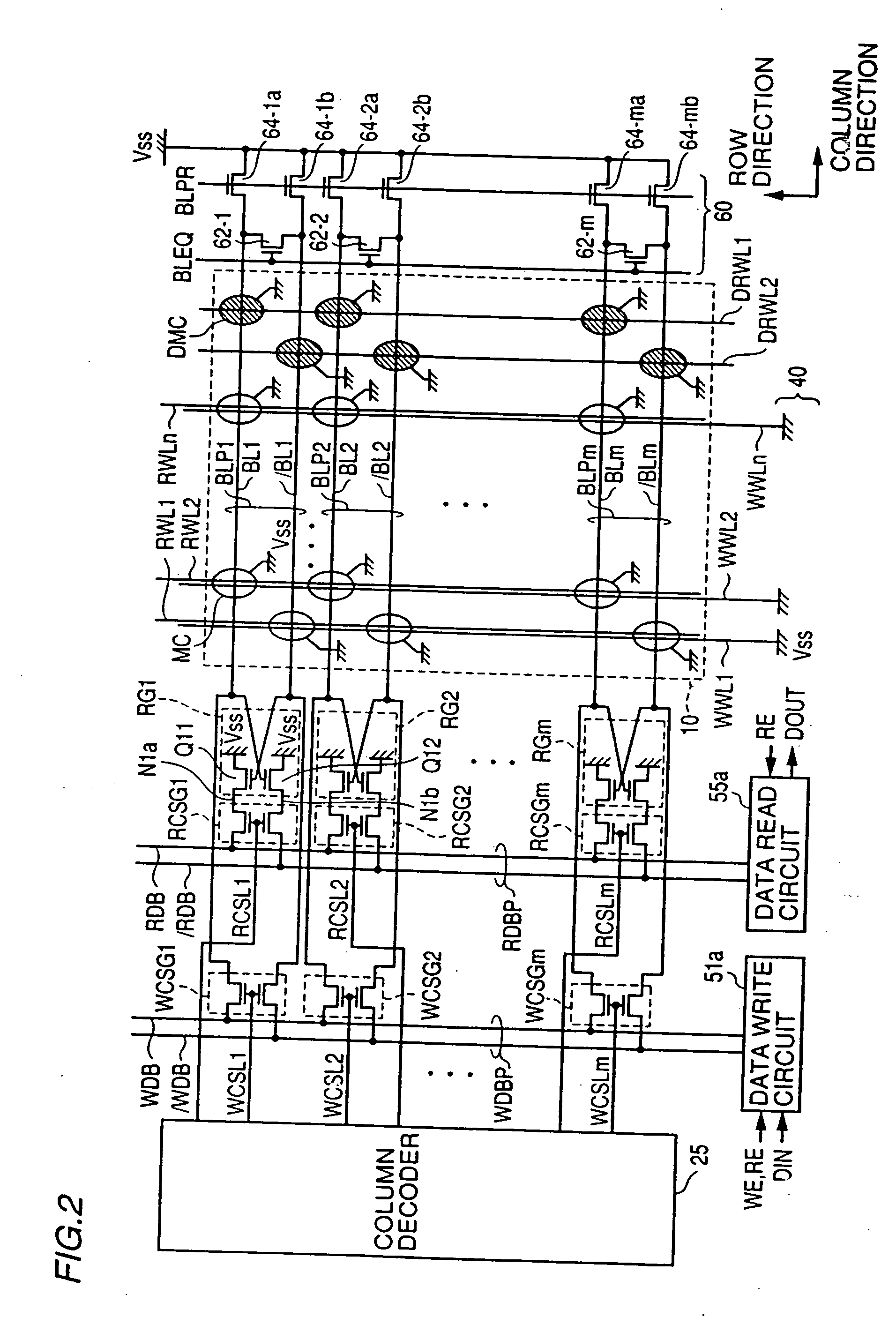

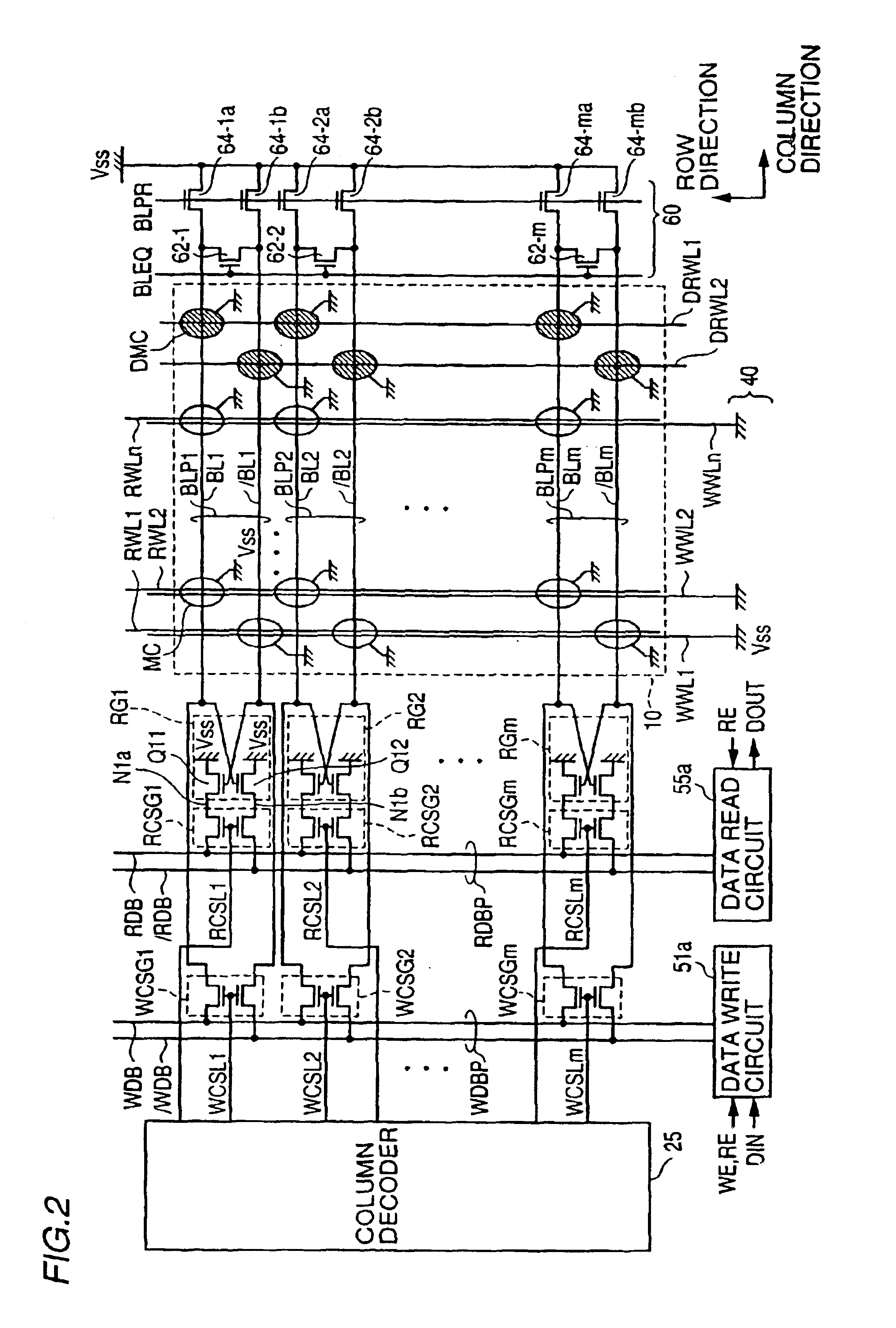

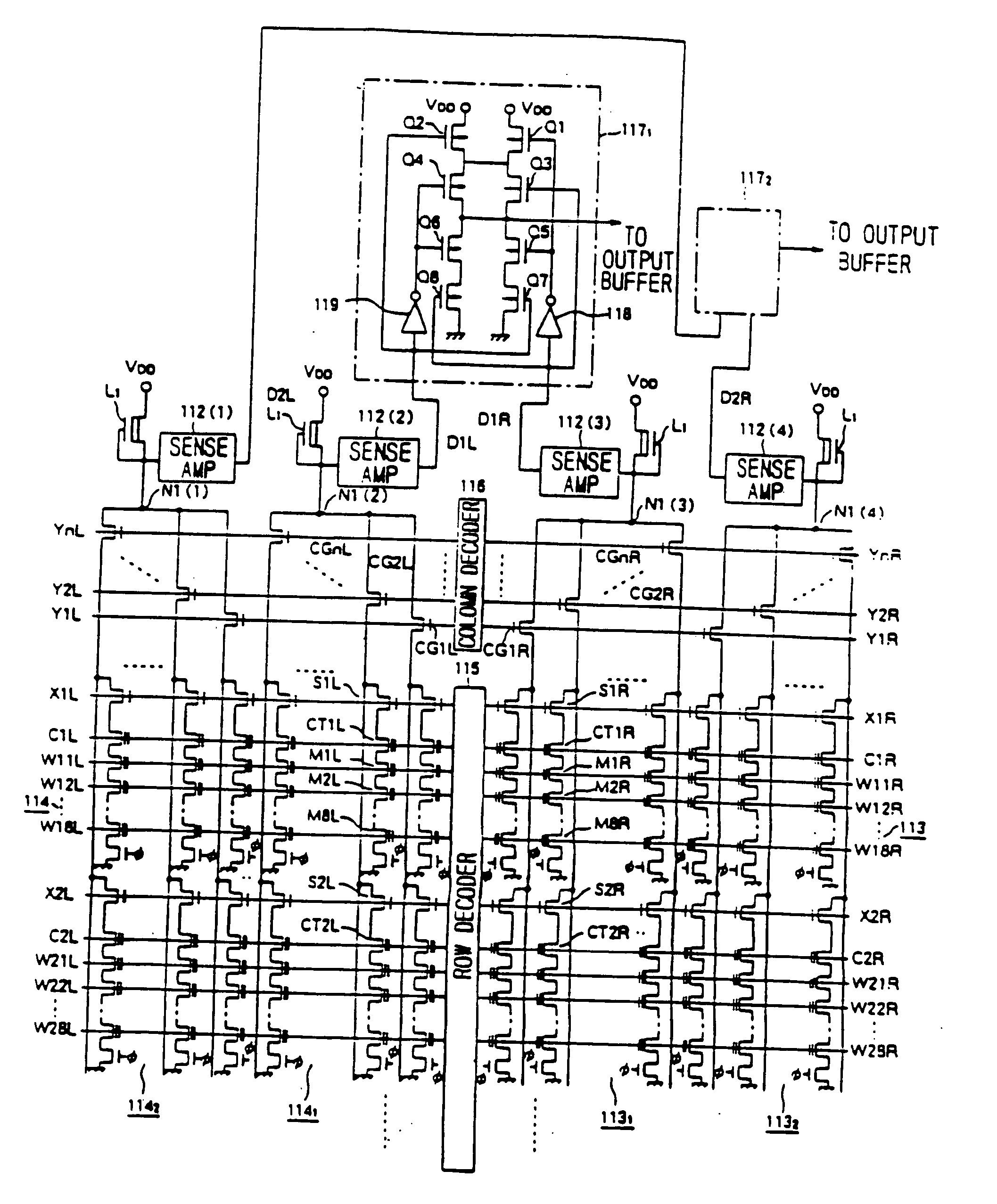

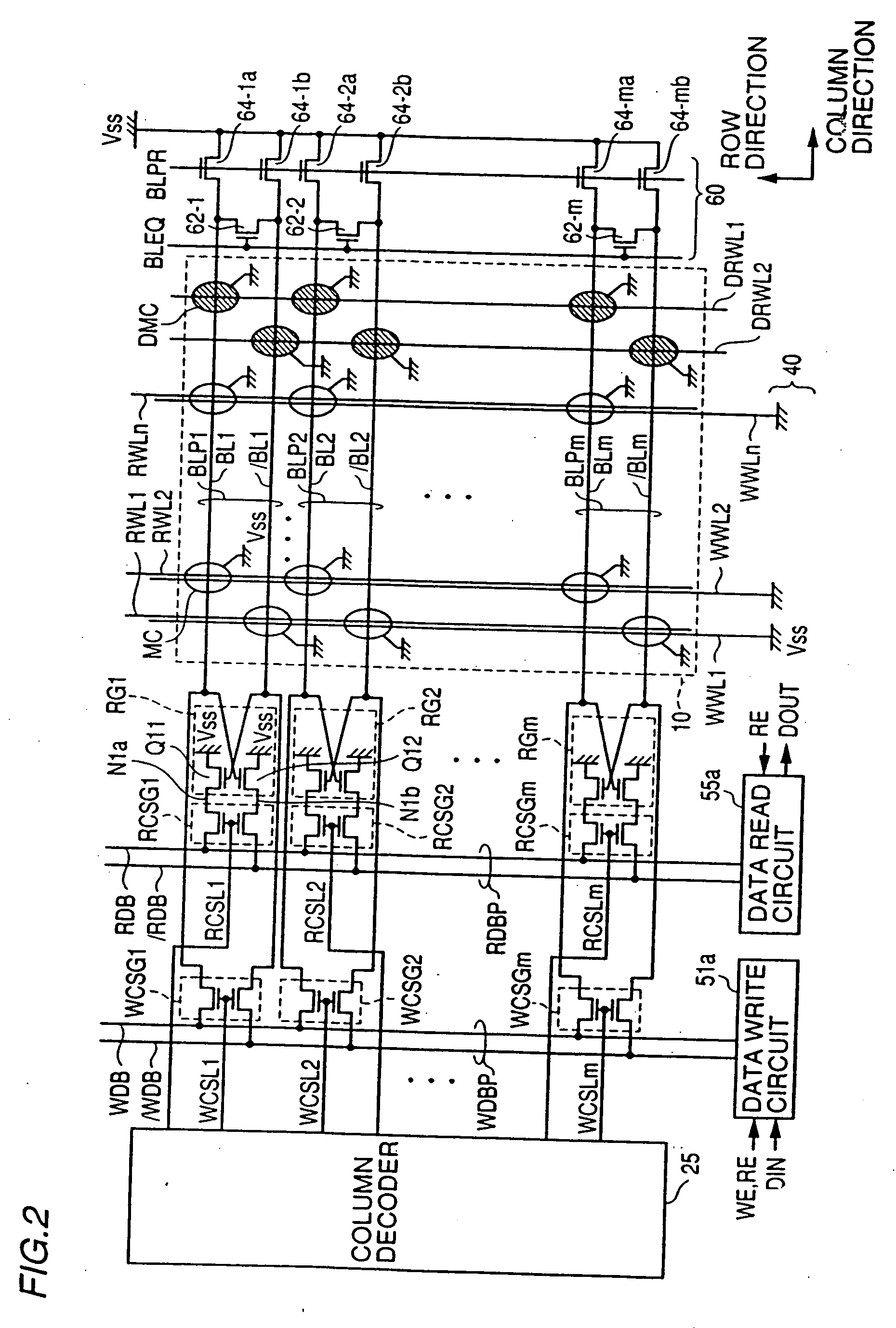

Thin film magnetic memory device including memory cells having a magnetic tunnel junction

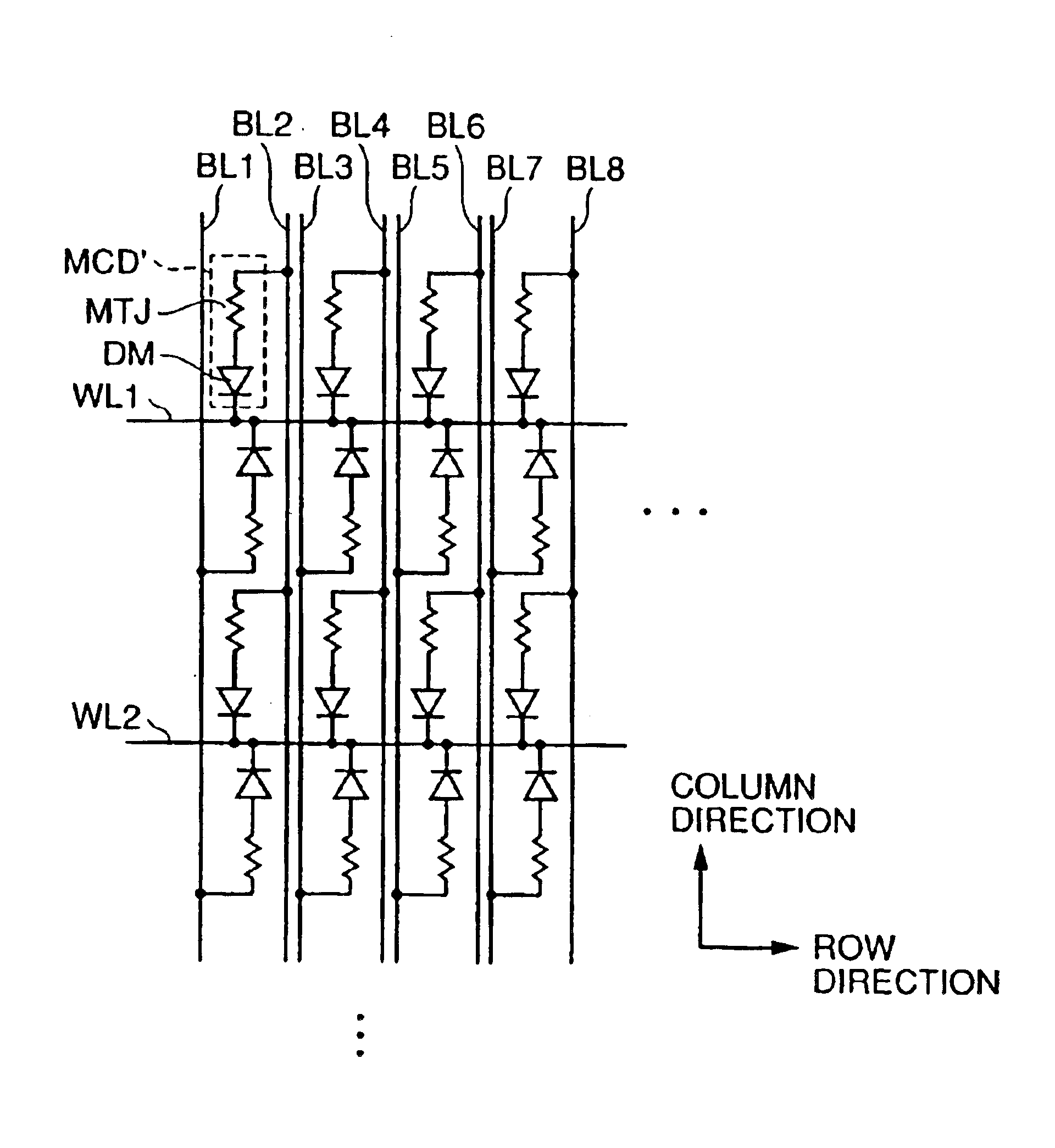

InactiveUS20050128860A1Improve data reading speedGain is not constantMagnetic-field-controlled resistorsSolid-state devicesComputer hardwareBit line

In the data read operation, a memory cell and a dummy memory cell are respectively coupled to two bit lines of a selected bit line pair, and a data read current is supplied thereto. In the selected memory cell column, a read gate drives the respective voltages on a read data bus pair, according to the respective voltages on the bit lines. A data read circuit amplifies the voltage difference between the read data buses so as to output read data. The use of the read gate enables the read data buses to be disconnected from a data read current path. As a result, respective voltage changes on the bit lines are rapidly produced, whereby the data read speed can be increased.

Owner:RENESAS TECH CORP

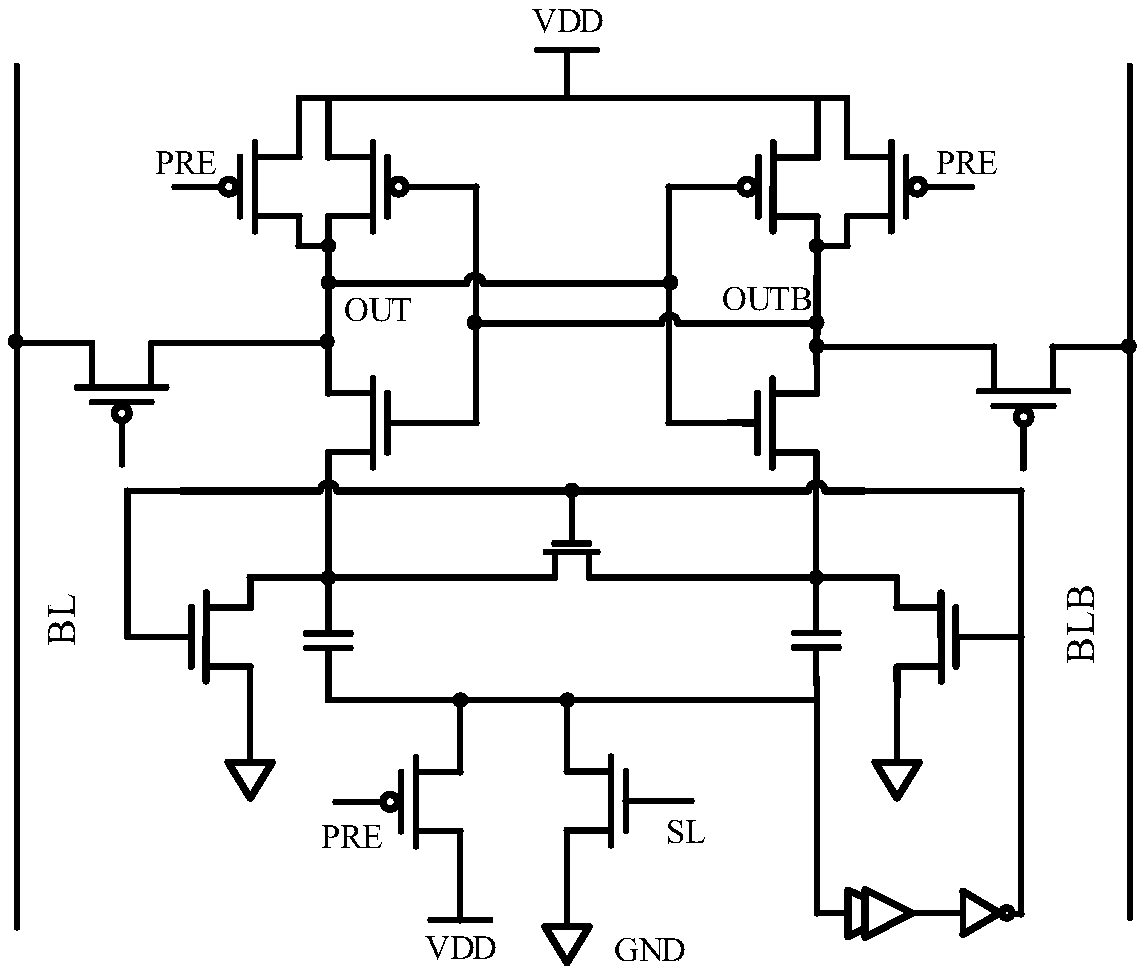

A sensitive amplifier circuit with ultra-low offset

PendingCN109448768AReduce power consumptionImprove data reading speedDigital storageCapacitanceStatic random-access memory

The invention discloses a sensitive amplifier circuit with ultra-low offset. According to the sensitive amplifier structure, the offset voltage can be greatly reduced, amplification of the bit line voltage difference and storage compensation of the threshold voltage difference are achieved through the capacitor storage voltage and the characteristic that the voltage is not suddenly changed, and the effect of greatly reducing the offset voltage is achieved. Meanwhile, along with great reduction of offset voltage, the data reading speed of the static random access memory can be effectively increased, the energy consumption during unit reading is reduced, and the margin of the reading voltage of the static random access memory is effectively improved.

Owner:ANHUI UNIVERSITY

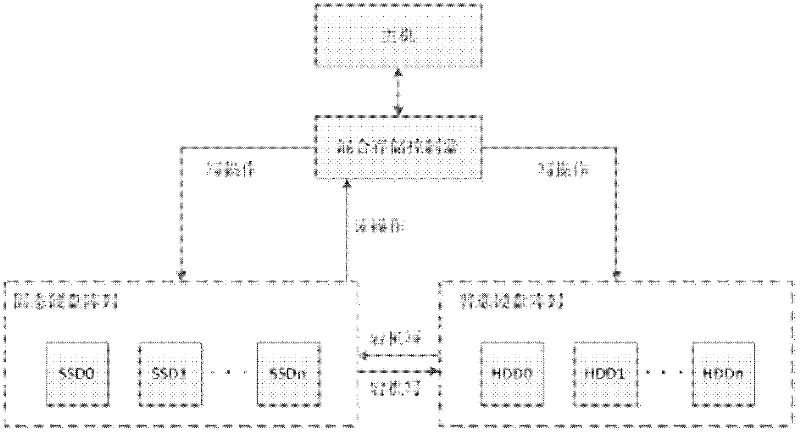

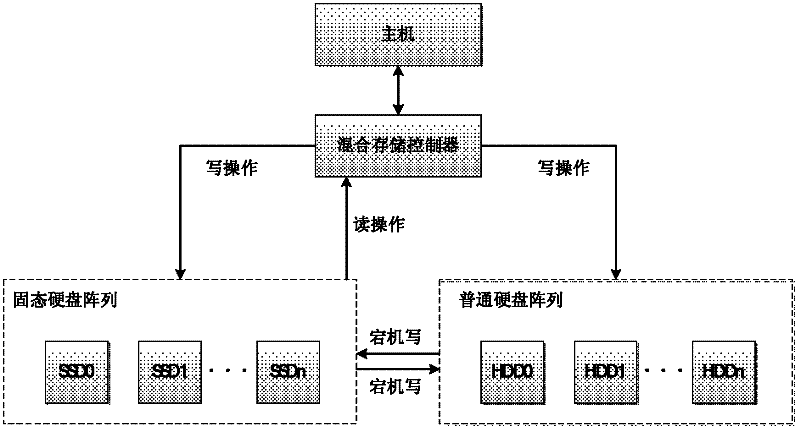

Hybrid storage control system and method

InactiveCN102541466AIncrease write speedImprove data reading speedInput/output to record carriersControl systemSolid-state drive

The invention discloses a hybrid storage control system and method. By partitioning a hard disc array into a solid hard disc array and a magnetic disc type hard disc array according to different types, and using the solid hard disc array as a default data reading source, data reading speed of a system is increased on condition that security performance of the system is not decreased. In addition the data is written into a normal hard disc in mode of writing-in-order, such that disc head seeking is not necessary during writing operation, and that the speed in writing the data into the normal hard disc matches with the speed in writing the data into the solid hard disc, thereby further improving the speed of data writing. The invention is applicable for a variety of storage systems both including the solid hard disc and the magnetic disc type hard disc.

Owner:忆正存储技术(武汉)有限公司

Input sensor containing display device and method for driving the same

ActiveUS7612818B2Data efficientImprove data reading speedTelevision system detailsTelevision system scanning detailsDisplay deviceComputer science

An input sensor containing a display device including a group of pixel circuits arranged in a matrix, a group of optical sensor circuits arranged in a matrix, a display driving circuit which provides a display signal to the display element group and which provides a driving signal to the display element group, a read circuit which identifies an optical sensor to read a sense signal from this optical sensor, and a read signal processing section which processes the sense signal output by the read circuit in accordance with a command. The read signal processing section has an interface section which transfers, when the command requesting execution of an application is set to the interface section, the command to a command register.

Owner:JAPAN DISPLAY CENTRAL CO LTD

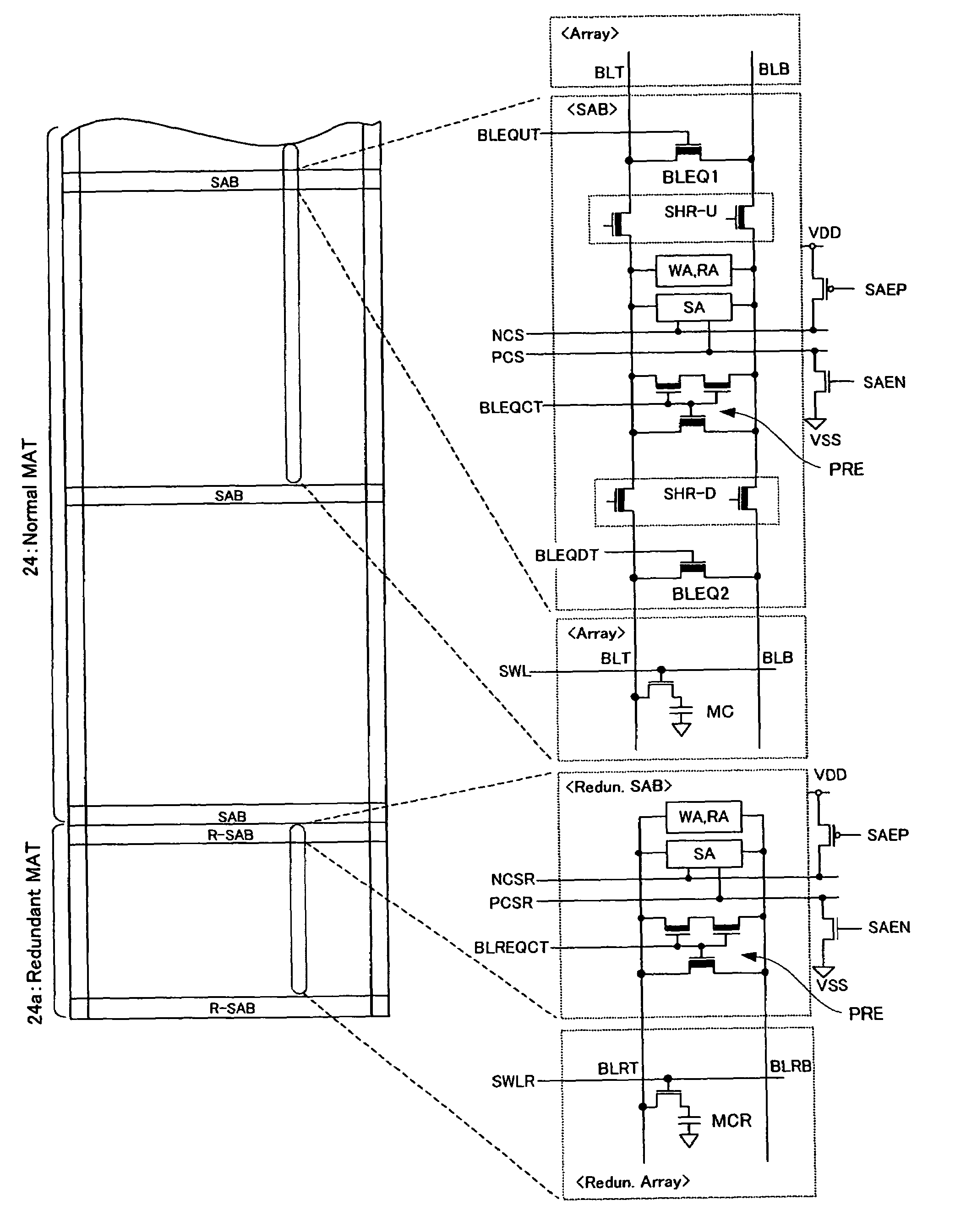

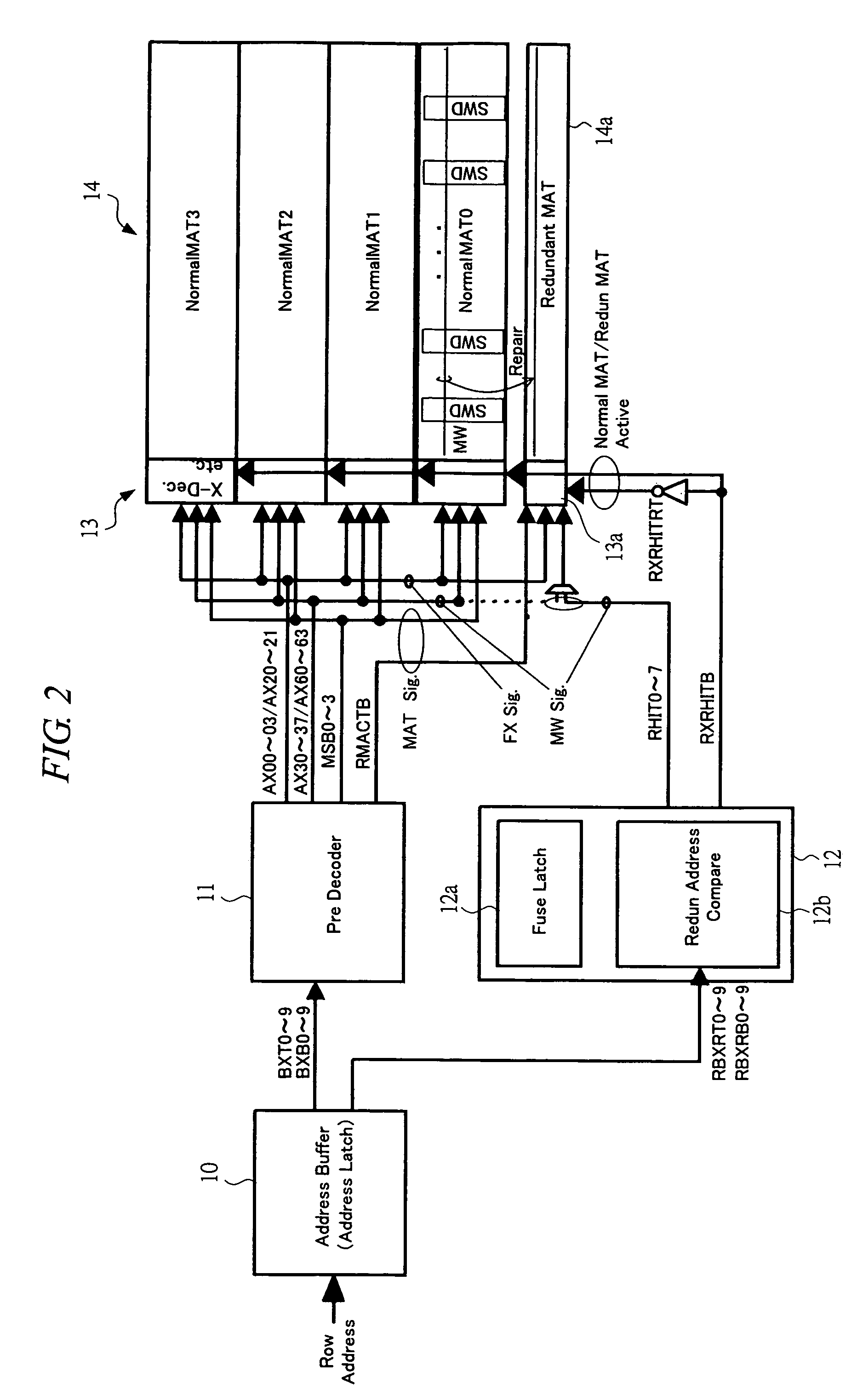

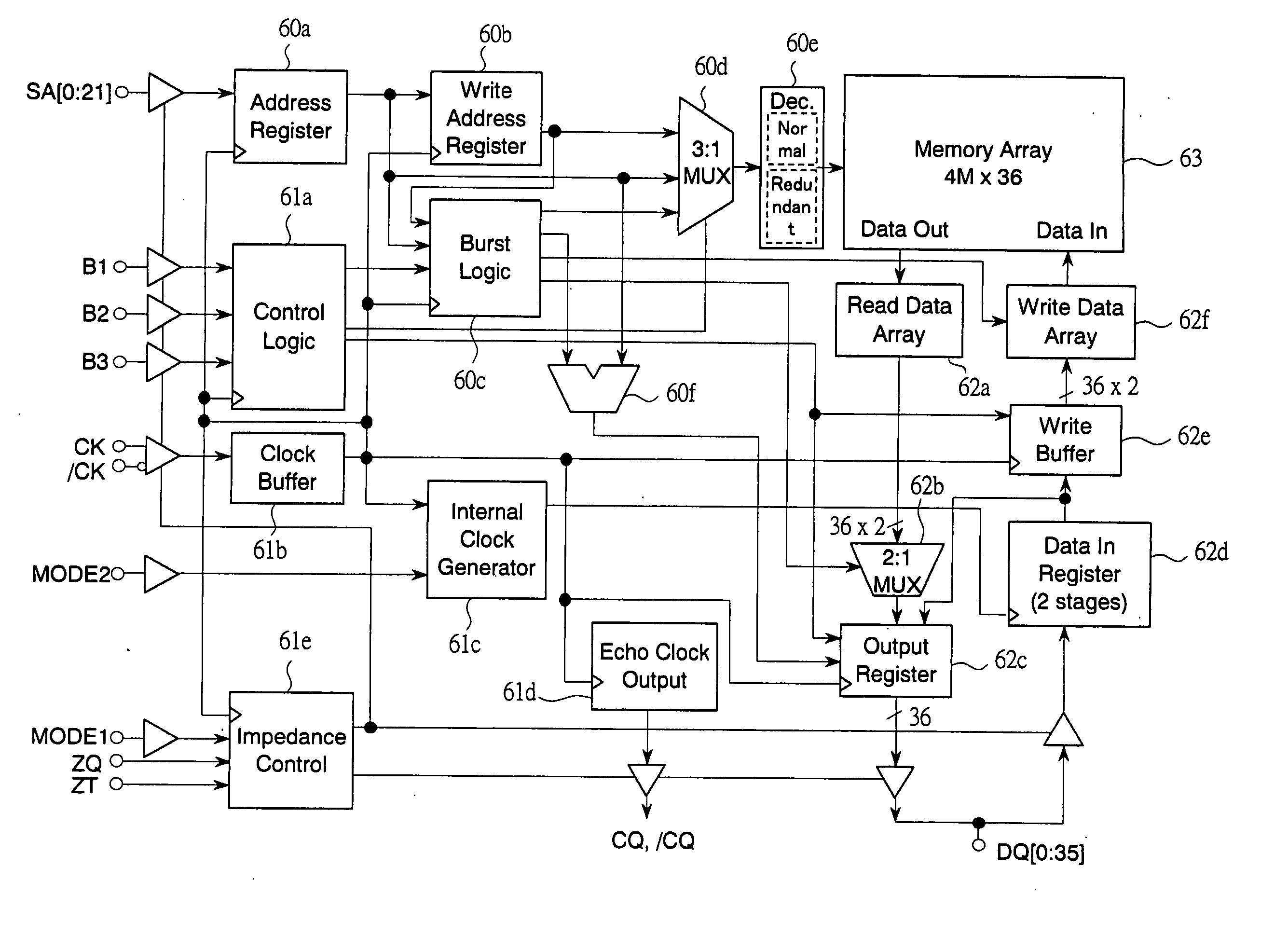

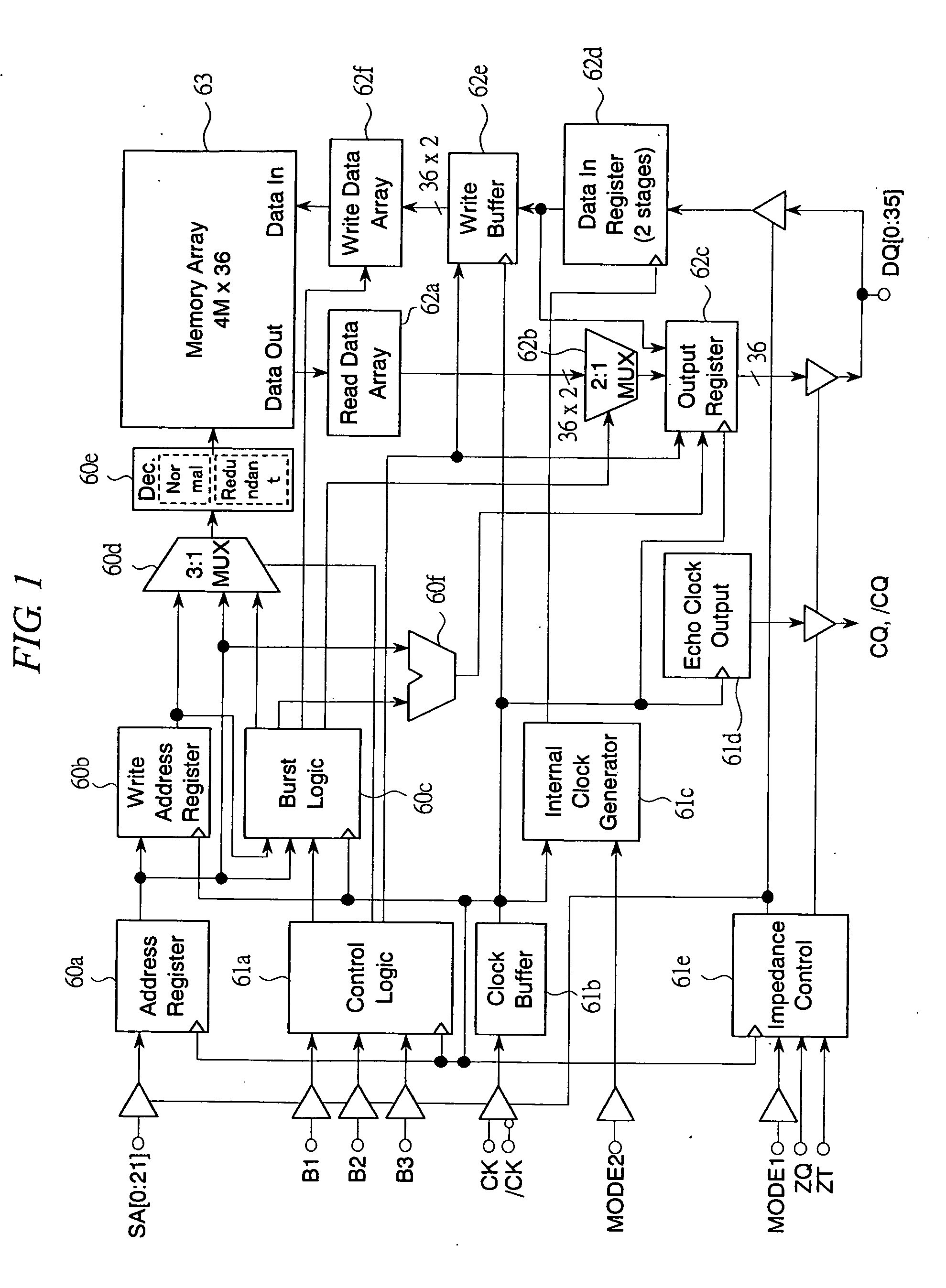

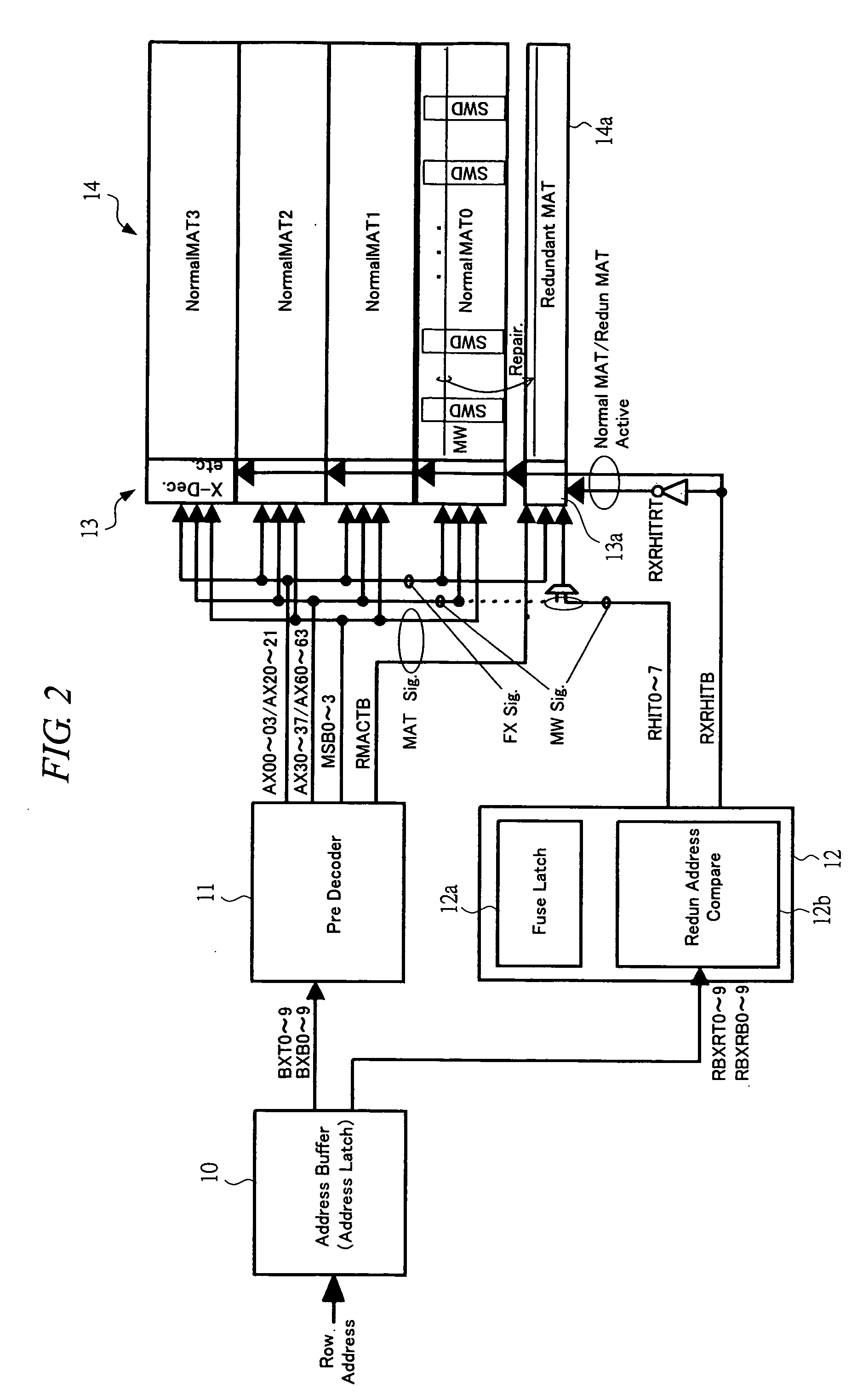

Semiconductor memory device

InactiveUS7184330B2Reduce access latencyImprove reliabilityDigital storageBit lineAudio power amplifier

A semiconductor memory device capable of improving the reliability when driving a word line and capable of reducing the access delay due to the defect relief is provided. In order to prevent the multiple selection of a sub-word line of a normal memory mat and a sub-word line of a redundant memory mat, the start of the redundant memory mat is delayed from that of the normal memory mat, and in order to compensate the start delay, the shared circuit is eliminated and the bit line length is reduced in the redundant memory mat. By doing so, the read time of the bit lines is reduced and the signal amount is increased. Consequently, the same activation timing of the sense amplifier as that of the normal memory mat can be used also in the redundant memory mat.

Owner:HITACHI LTD +1

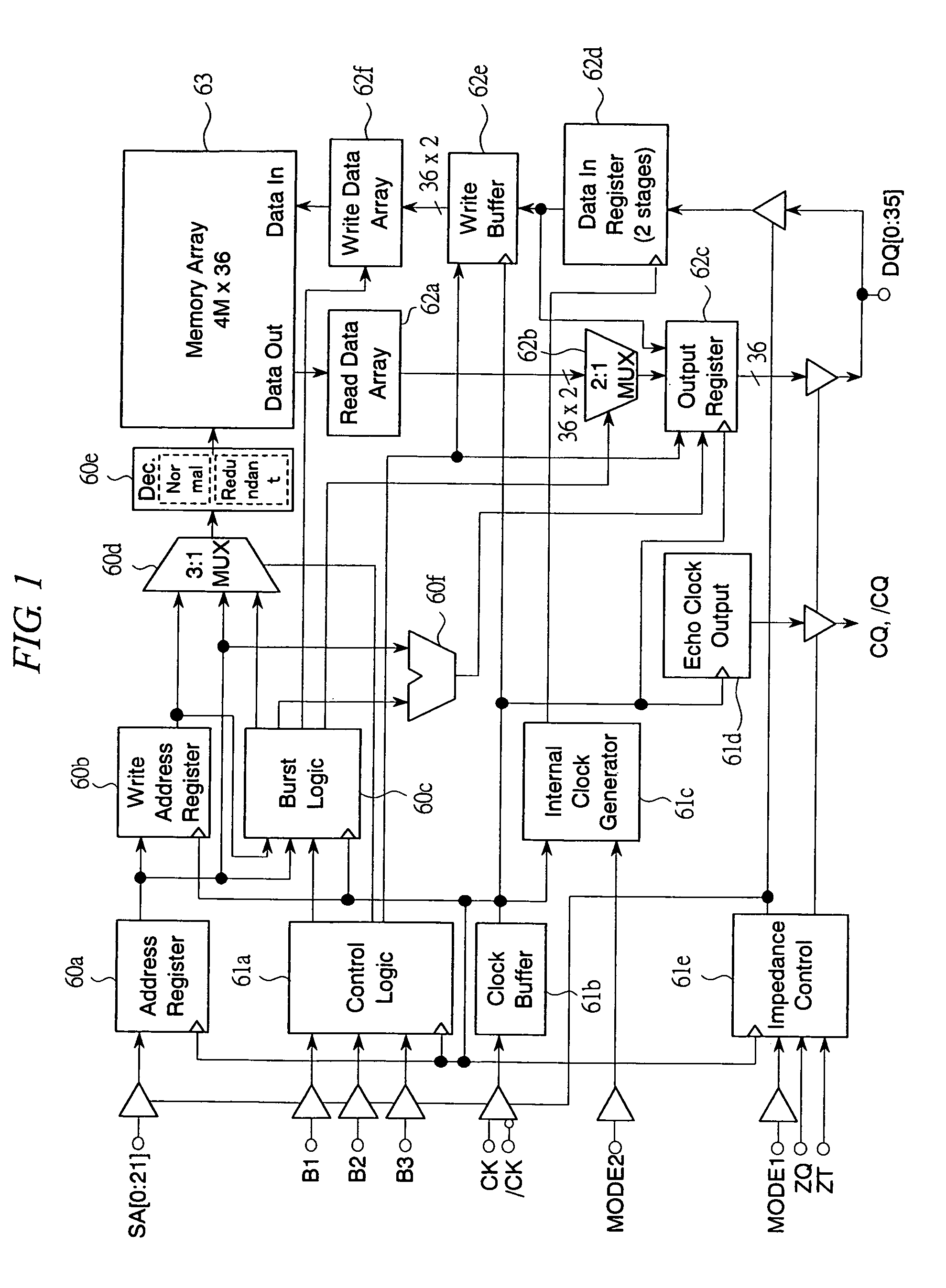

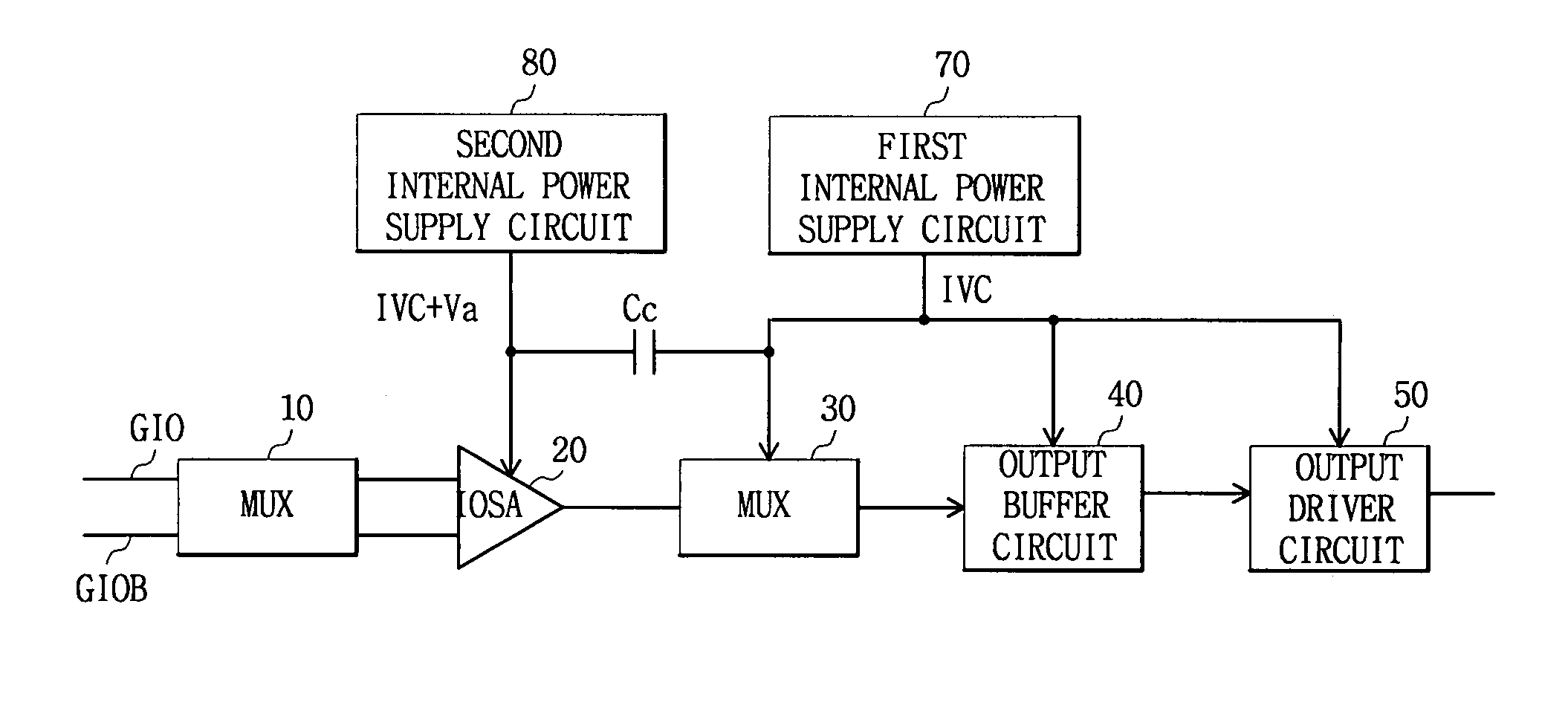

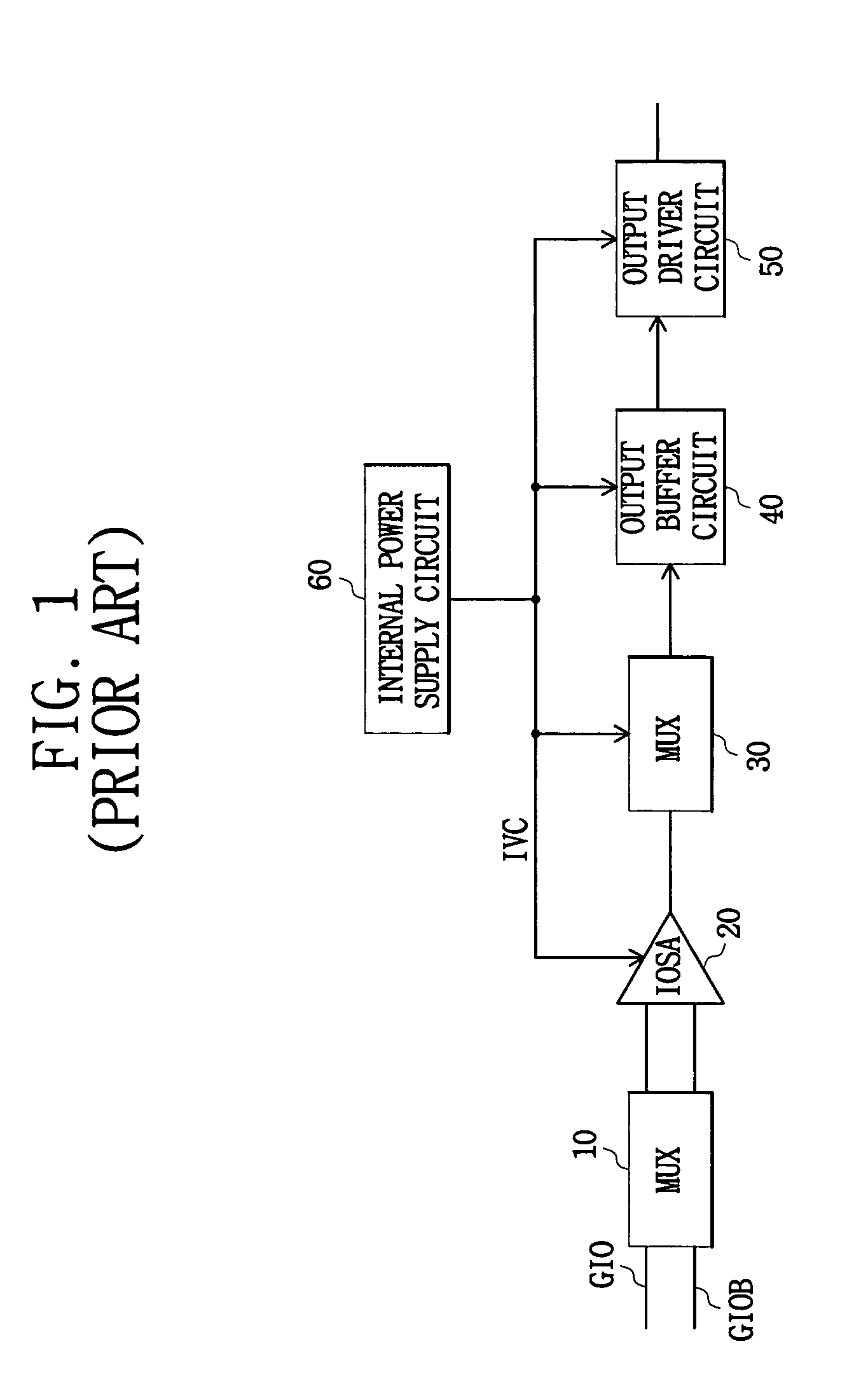

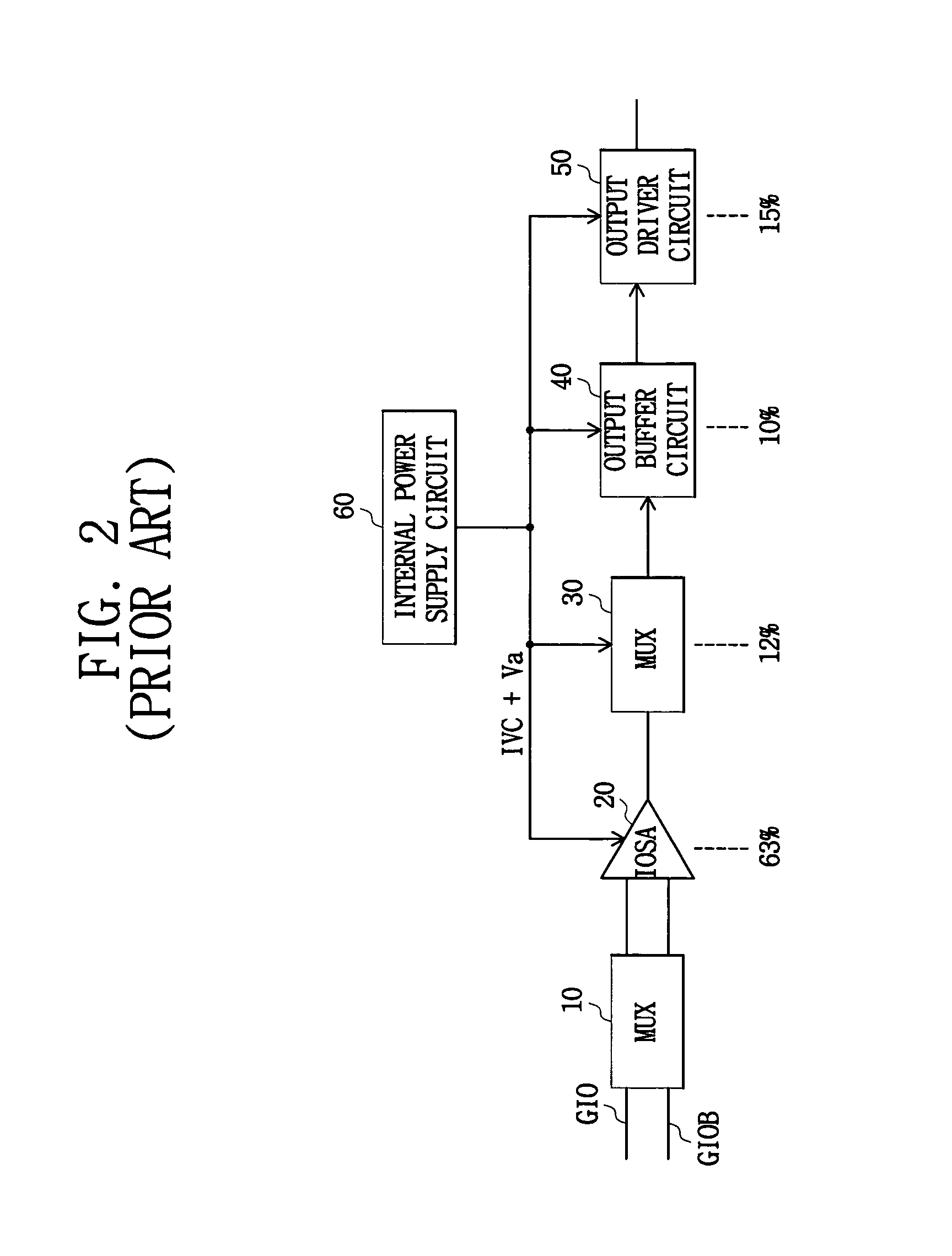

Method and apparatus for increasing data read speed in a semiconductor memory device

InactiveUS7102952B2Improve data reading speedReduce power consumptionDigital storageAudio power amplifierHemt circuits

A semiconductor memory device having a data read path maintains a higher power voltage supplied to an input / output sense amplifier in the input / output path, through which data passes during a data read operation, than the voltage supplied to other circuit components in the data read path, thereby achieving a high data read speed.

Owner:SAMSUNG ELECTRONICS CO LTD

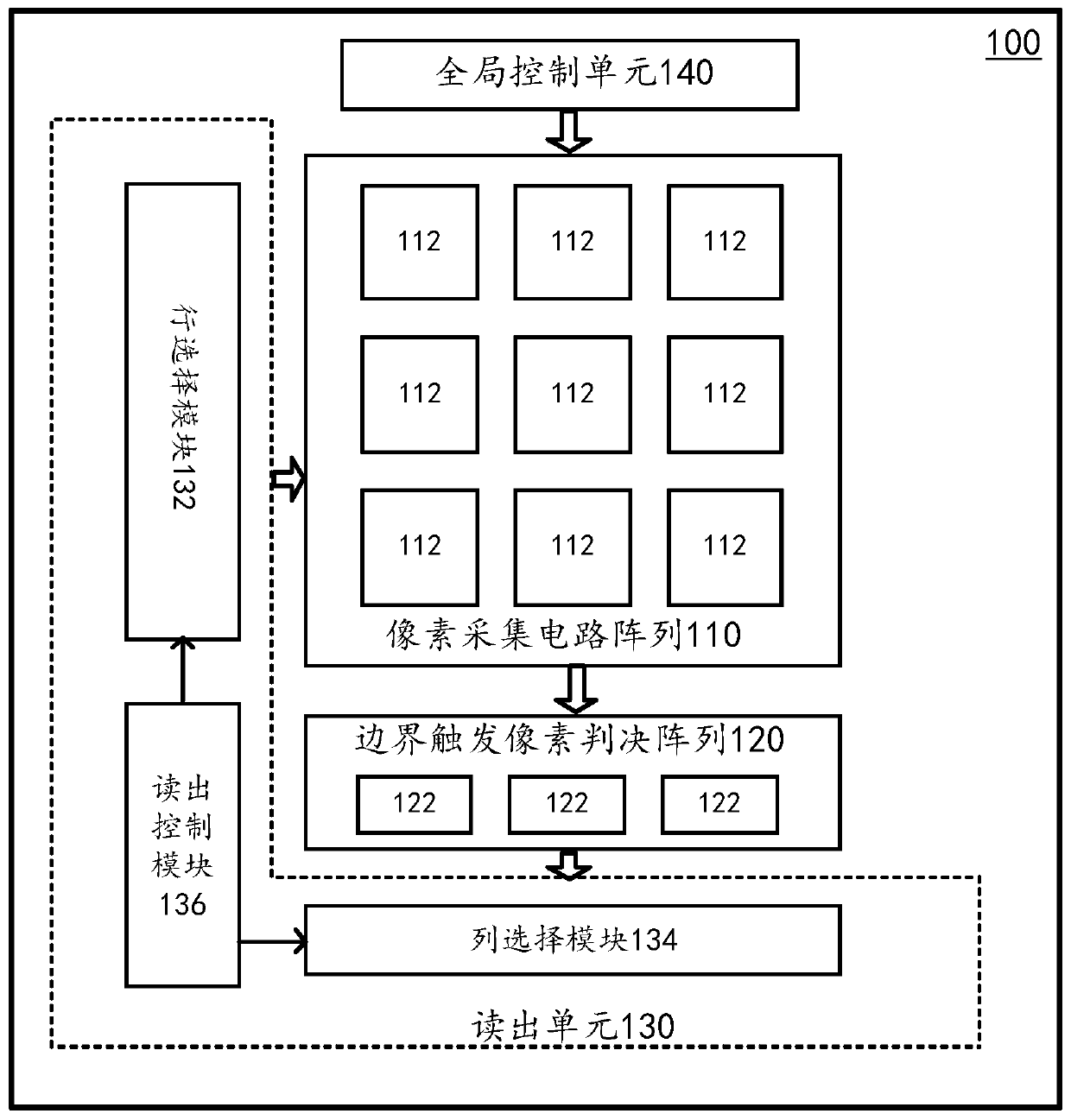

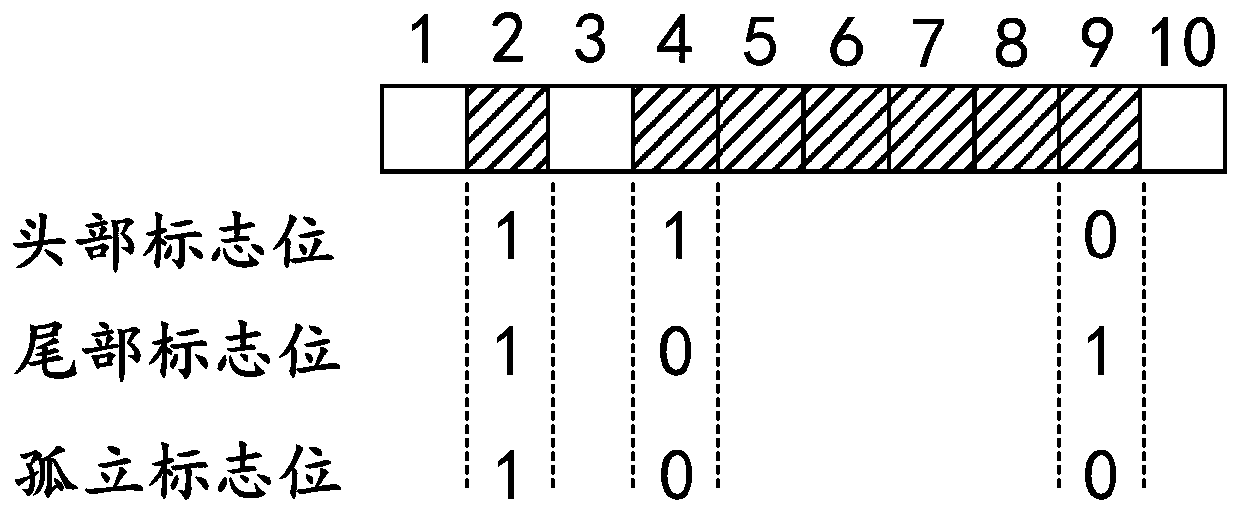

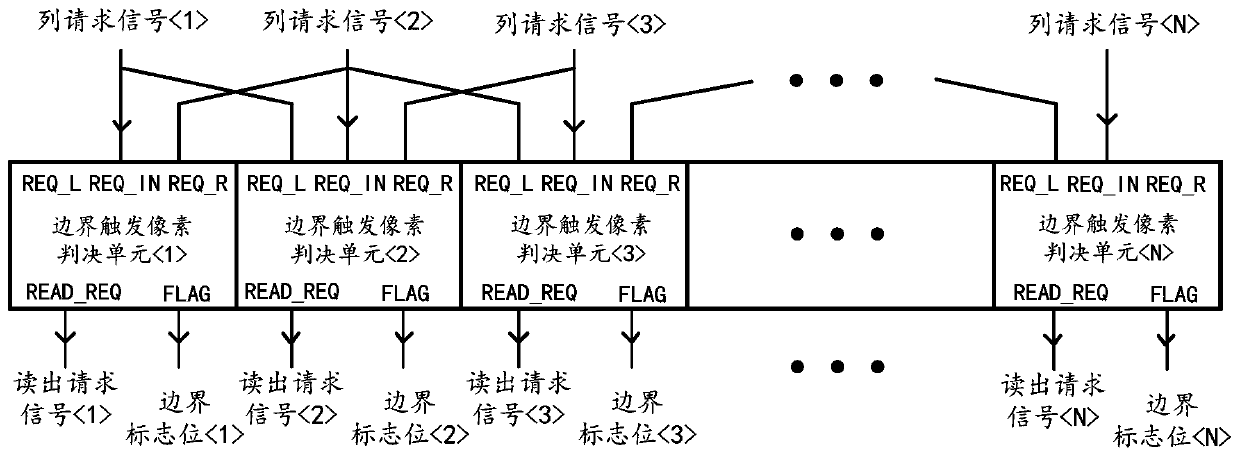

Image sensor and image acquisition system

ActiveCN110536083AReduce congestionReduce data volumeTelevision system detailsColor television detailsComputer scienceImage acquisition

The invention discloses an image sensor and an image acquisition system. The image sensor comprises a pixel acquisition circuit array composed of a plurality of pixel acquisition circuits, and the pixel acquisition circuits are suitable for monitoring light intensity changes in a view field and entering a trigger state when the light intensity changes meet a certain condition; the boundary triggerpixel decision array is suitable for determining a trigger pixel acquisition circuit at the boundary from the pixel acquisition circuits at the trigger state; and the reading unit is suitable for responding to the trigger pixel acquisition circuit located at the boundary and outputting corresponding address information of the trigger pixel acquisition circuit.

Owner:OMNIVISION SENSOR SOLUTION (SHANGHAI) CO LTD

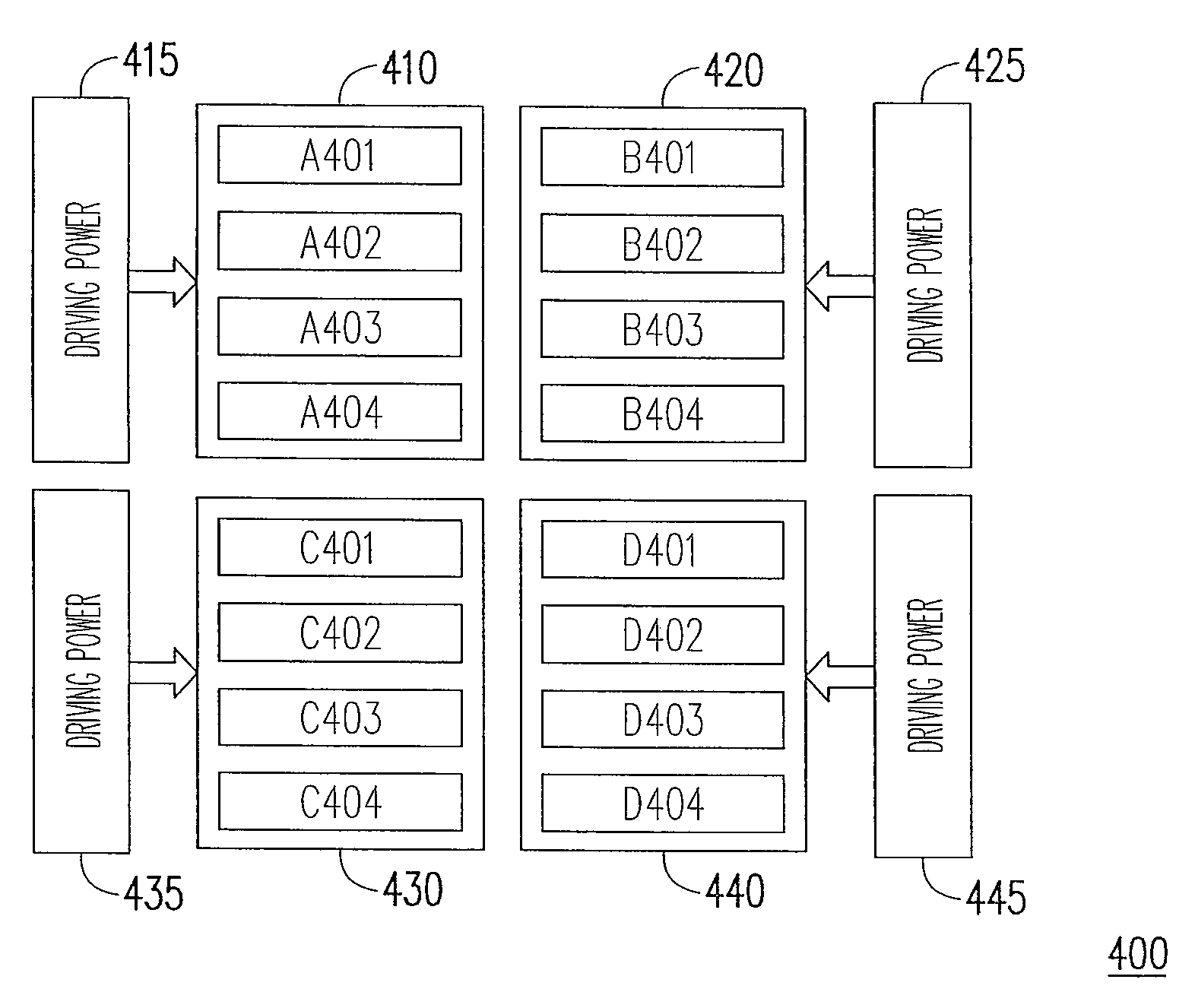

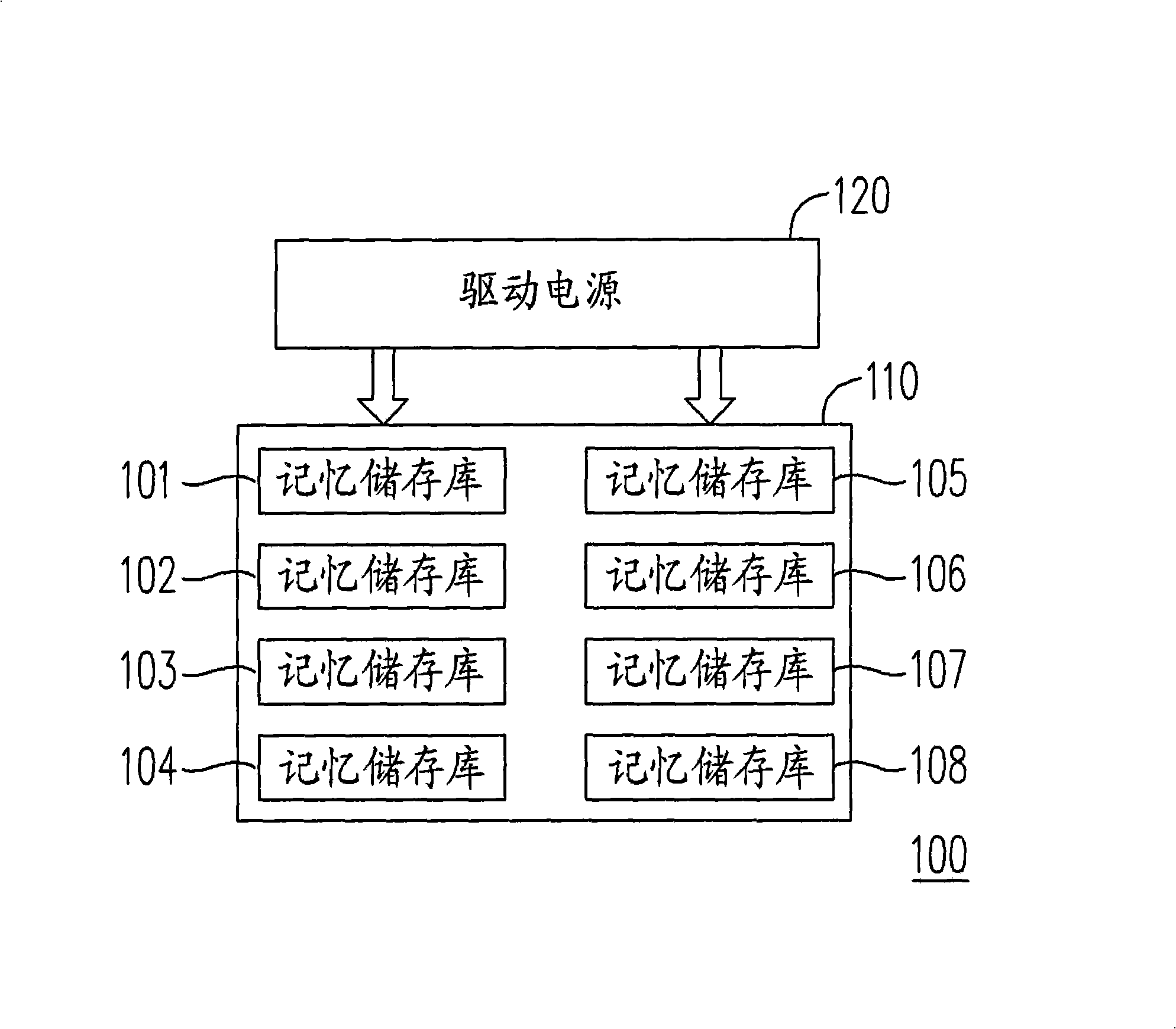

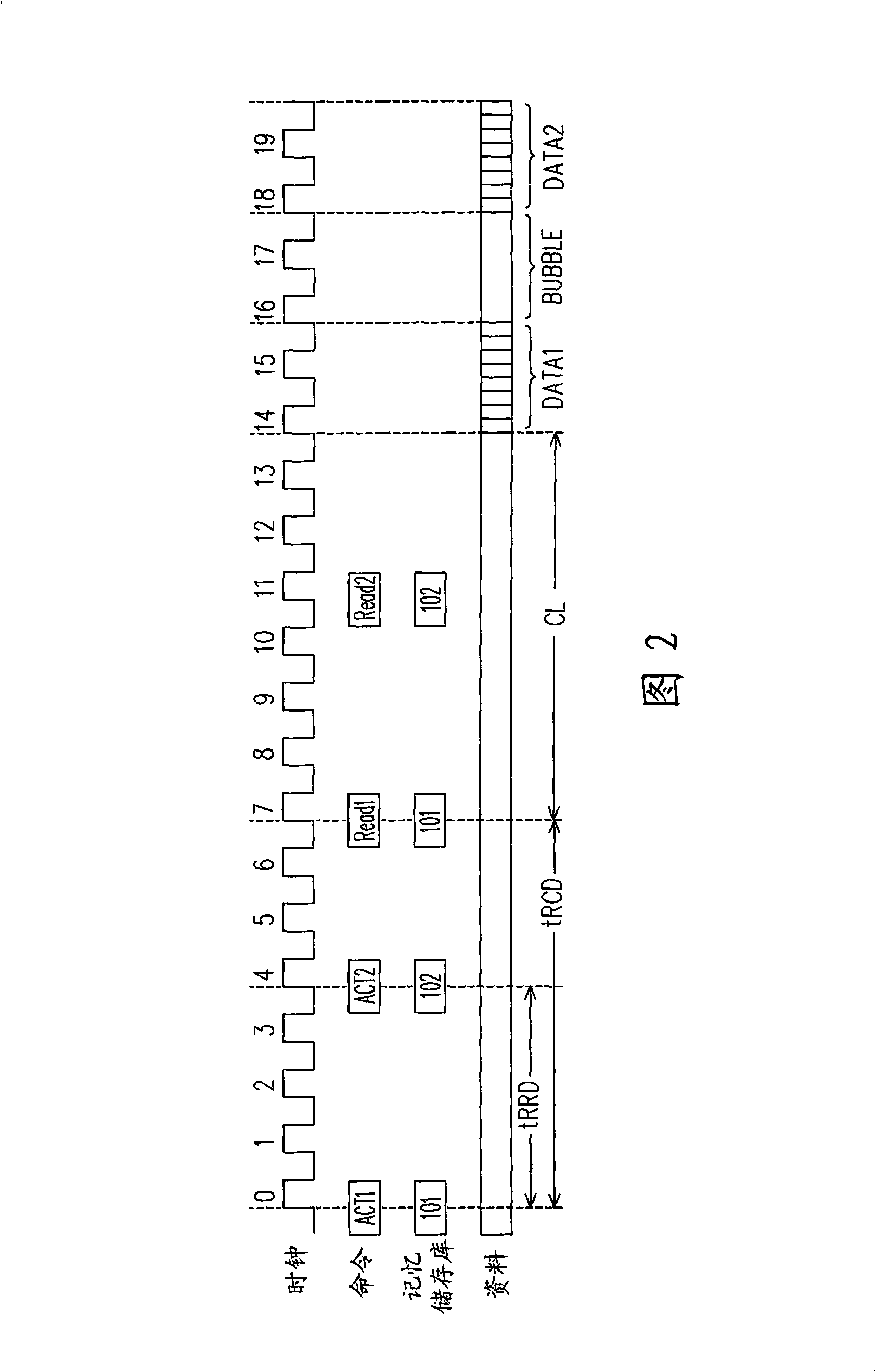

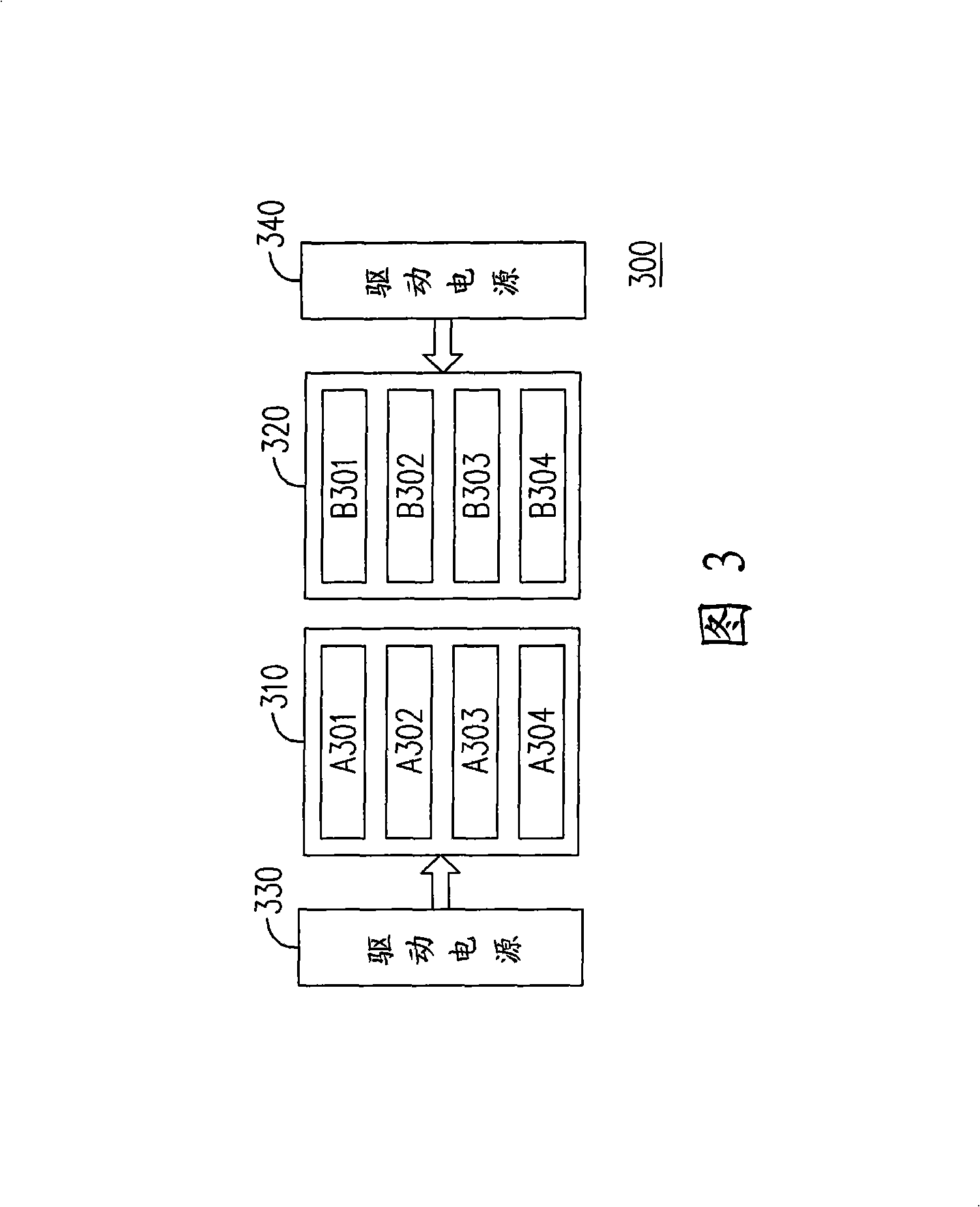

Memory and operation method thereof

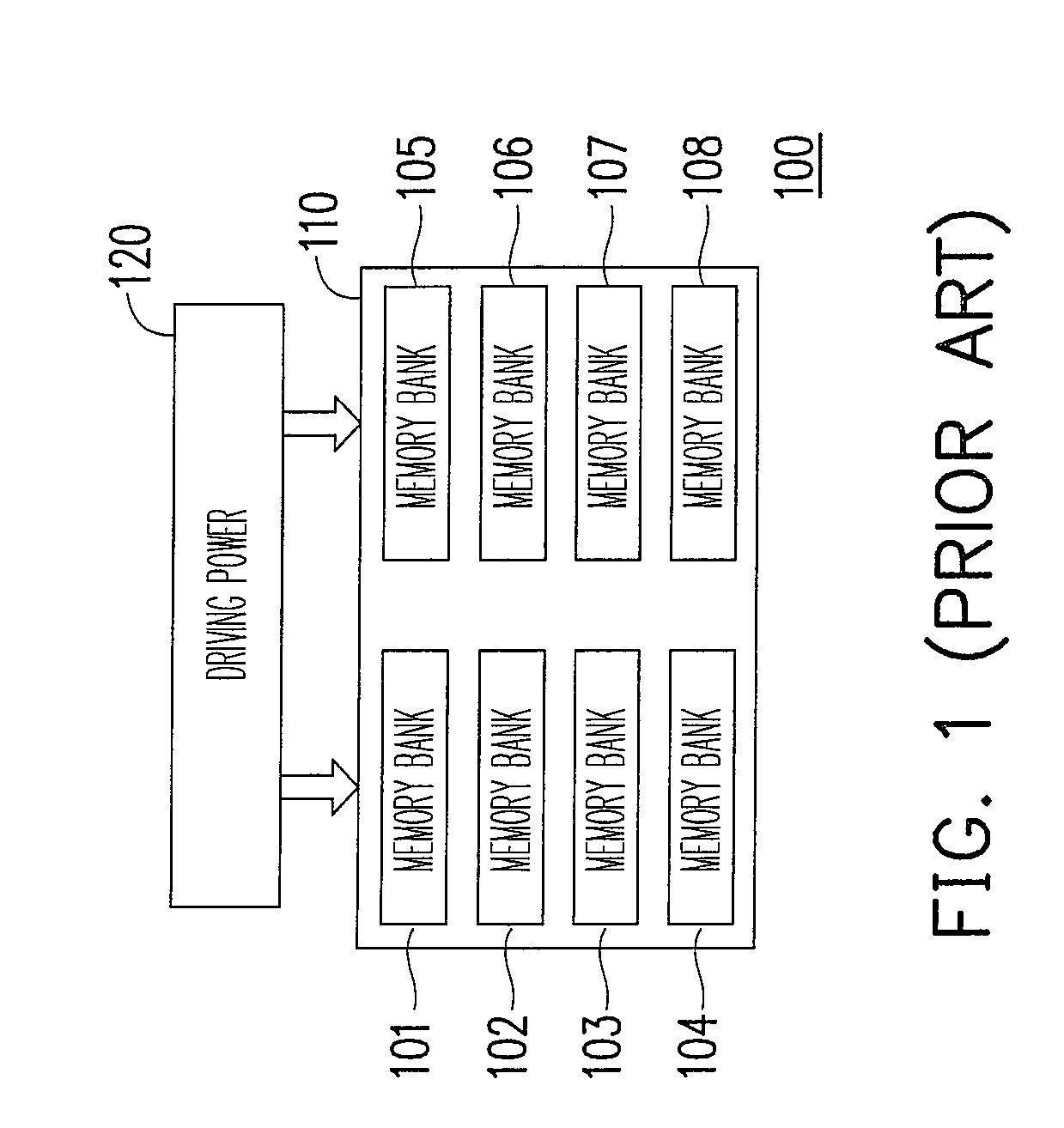

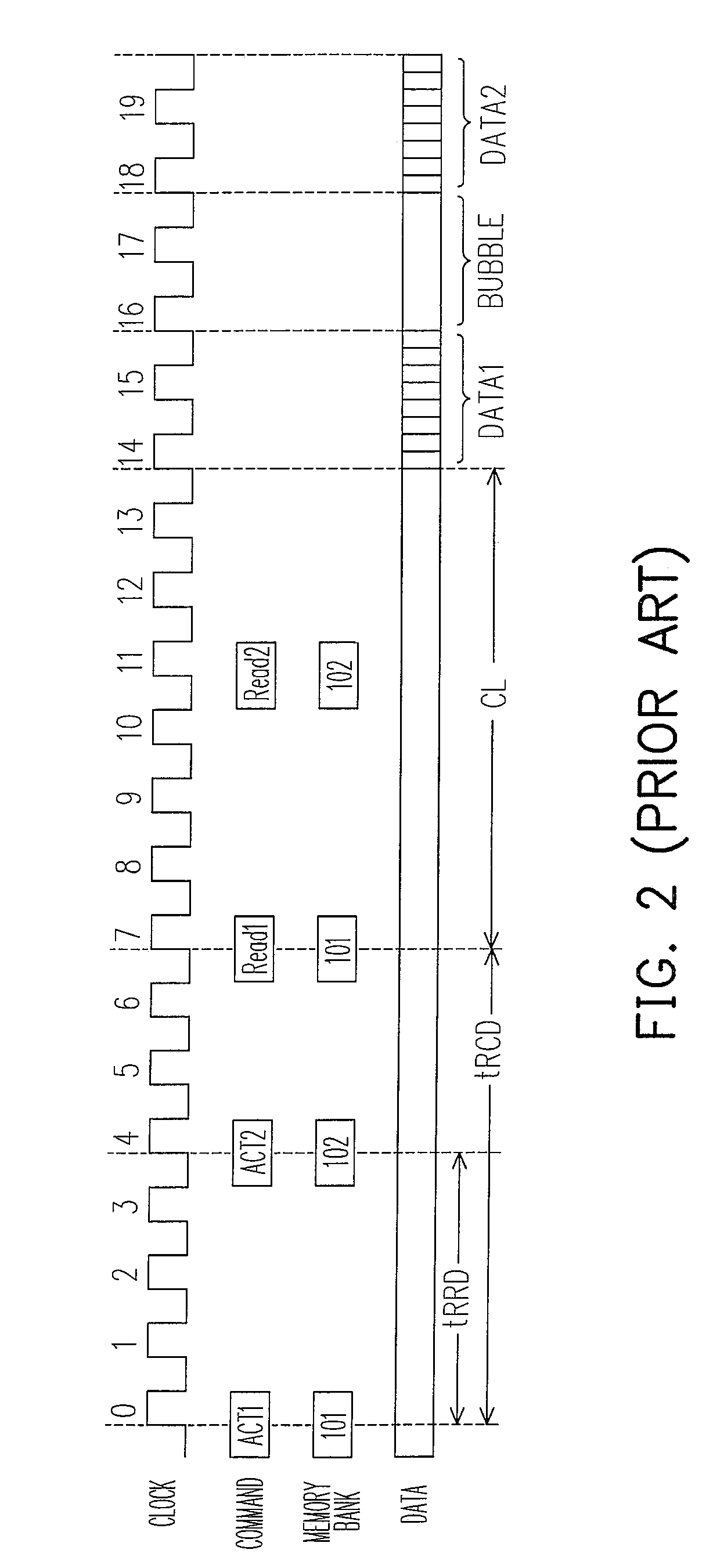

ActiveUS7447102B2Shorten the time intervalImprove selection efficiencyDigital storageComputer hardwareMemory bank

A memory and an operation method thereof are provided. The present invention divides memory banks of the memory into a plurality of memory groups, wherein each memory group has an independent driving power for providing an operating voltage to the corresponding memory bank in the memory group. The present invention specifies two tRRD times which are an inter-group interval and an intra-group interval. The intra-group interval is the minimum time interval between selecting one row of memory banks in a memory group to selecting another row in the memory banks of the same memory group and the inter-group interval is the minimum time interval between selecting one row of the memory banks in one memory group to selecting another row in a different memory group. Further, the inter-group interval is shorter than or equal to the intra-group interval.

Owner:NAN YA TECH

Thin film magnetic memory device including memory cells having a magnetic tunnel junction

InactiveUS6856539B2Improve data reading speedGain is not constantMagnetic-field-controlled resistorsSolid-state devicesComputer hardwareBit line

In the data read operation, a memory cell and a dummy memory cell are respectively coupled to two bit lines of a selected bit line pair, and a data read current is supplied thereto. In the selected memory cell column, a read gate drives the respective voltages on a read data bus pair, according to the respective voltages on the bit lines. A data read circuit amplifies the voltage difference between the read data buses so as to output read data. The use of the read gate enables the read data buses to be disconnected from a data read current path. As a result, respective voltage changes on the bit lines are rapidly produced, whereby the data read speed can be increased.

Owner:RENESAS ELECTRONICS CORP

Semiconductor memory device

InactiveUS20050265091A1Improve reading speedImprove data reading speedDigital storageBit lineAudio power amplifier

A semiconductor memory device capable of improving the reliability when driving a word line and capable of reducing the access delay due to the defect relief is provided. In order to prevent the multiple selection of a sub-word line of a normal memory mat and a sub-word line of a redundant memory mat, the start of the redundant memory mat is delayed from that of the normal memory mat, and in order to compensate the start delay, the shared circuit is eliminated and the bit line length is reduced in the redundant memory mat. By doing so, the read time of the bit lines is reduced and the signal amount is increased. Consequently, the same activation timing of the sense amplifier as that of the normal memory mat can be used also in the redundant memory mat.

Owner:HITACHI LTD +1

Current-sense amplifier with low-offset adjustment and method of low-offset adjustment thereof

ActiveUS8320211B1Slow memory data read speedReduce detection accuracyCurrent/voltage measurementRead-only memoriesElectricityAudio power amplifier

A current-sense amplifier with low-offset adjustment and a low-offset adjustment method thereof are disclosed. The current-sense amplifier includes a sensing unit, an equalizing unit and a bias compensation unit. The sensing unit includes a sense amplifier, a latch circuit, a first precharged bit line, and a second precharged bit line. The equalizing unit is electrically connected to the first and the second precharged bit line for regulating a voltage of the first precharged bit line and a voltage of the second precharged bit line to the same electric potential. The bias compensation unit is electrically connected to the sense amplifier for compensating an input offset voltage of the current-sense amplifier.

Owner:NATIONAL TSING HUA UNIVERSITY

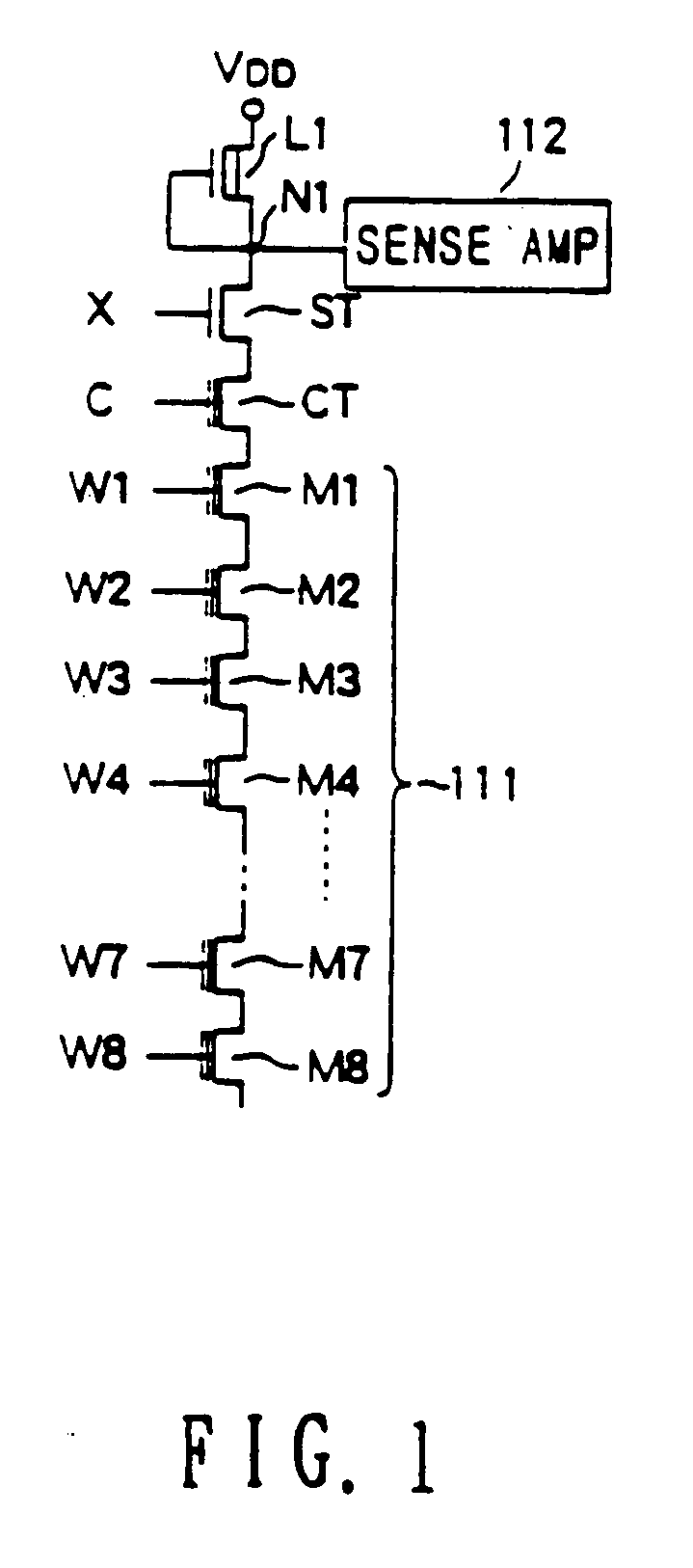

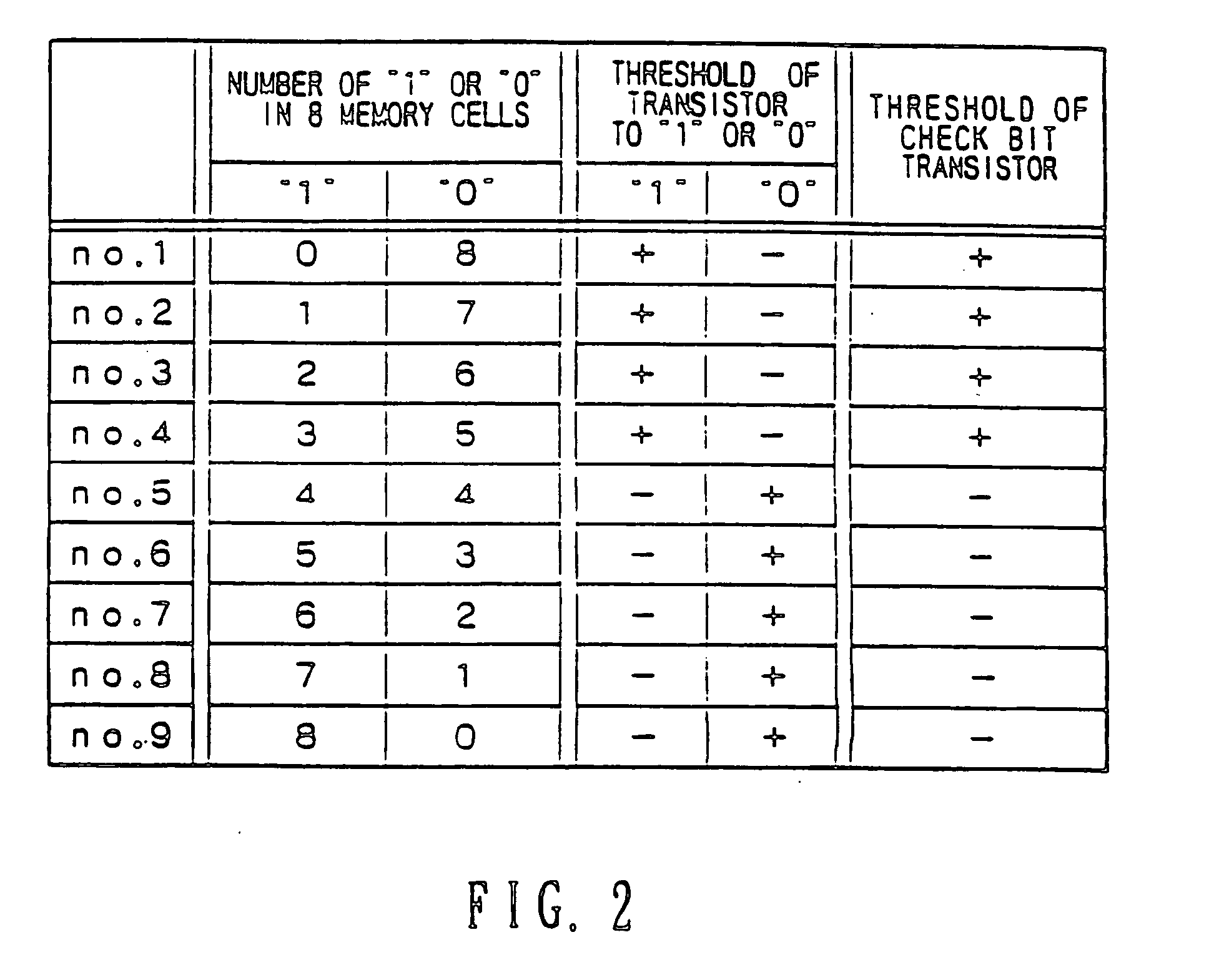

Non-volatile semiconductor memory device and data programming method

InactiveUS20060193173A1Improve data reading speedRead-only memoriesDigital storageElectron injectionChip size

In a non-volatile semiconductor memory, a large current can be flowed through the memory cell during reading. The number of the column lines can be reduced. The electron injection to the floating gates of the respective memory cells is averaged to reduce the electron emission from the floating gates of the respective memory cells is also averaged to reduce the dispersion of the threshold voltages thereof. An increase in chip size due to latch circuits can be prevented. By noting that either of a plurality of “0” or “1” of the binary data are stored such in the memory cells of the memory cell bundle or block, a negative threshold voltage in allocated to the memory cells for storing the more bit side data of the binary data. A single column line is used in common for the two adjacent memory blocks. To inject electrons to the floating gates of the memory cells, voltage is increased gradually and stopped when electrons have been injected up to a predetermined injection rate. Electrons are once emitted from the floating gates, and thereafter the electrons are injected again to store one of a binary data. Further, the data latch circuits can be formed at any positions remote from the memory cell array.

Owner:KK TOSHIBA

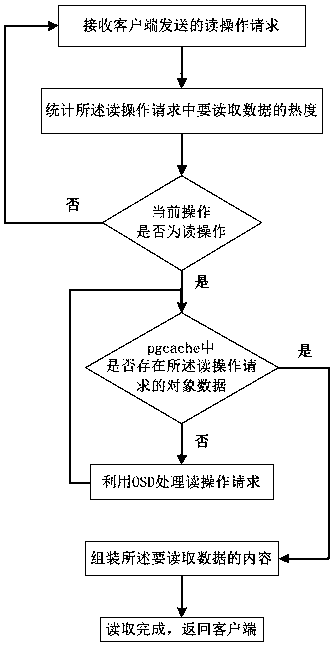

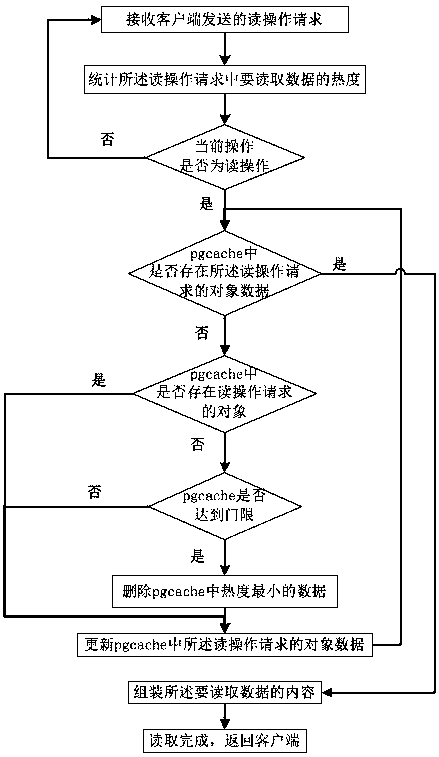

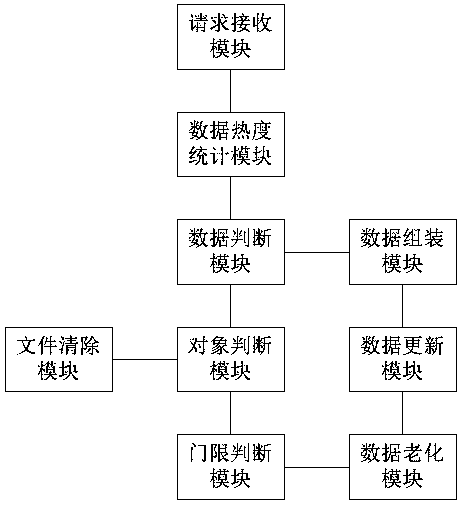

Data reading method, system and device based on distributed storage system

InactiveCN108958667ALower read latencyImprove data reading speedInput/output to record carriersClient-sideDistributed memory systems

The invention provides a data reading method based on a distributed storage system, which comprises the following steps: receiving a read operation request sent by a client; counting the heat of the data to be read in the read operation request; judging whether the current operation is a read operation or not, and if not, continuing to receive a read operation request sent by the client; if so, determining whether the object data requested by the read operation exists in the pgcache, and if so, assembling the contents of the data to be read; if not, processing the read operation request by theOSD, and after the processing is completed, assembling the contents of the data to be read. Therefore, the method can effectively reduce the read delay, improve the data read speed of the distributedstorage system, and further improve the read and write performance of the whole system by caching some hot data on the main pg and carrying out the data aging and hot data updating in the pgcache intime with the data reading

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

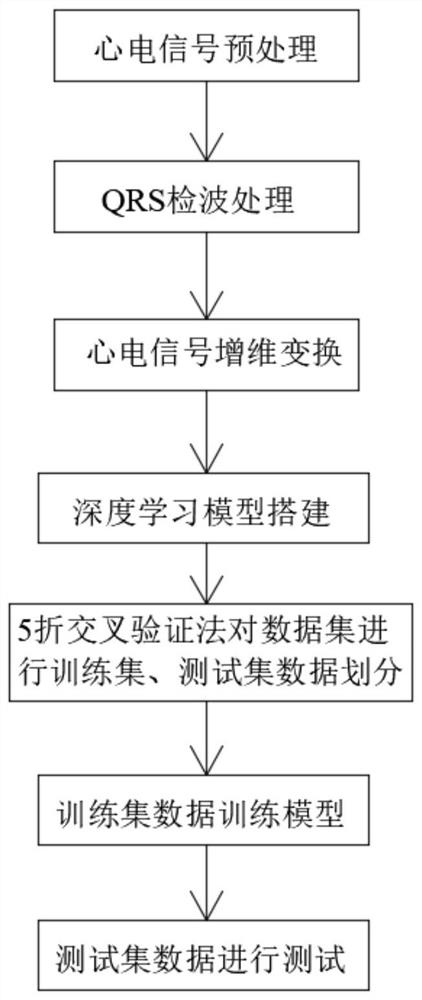

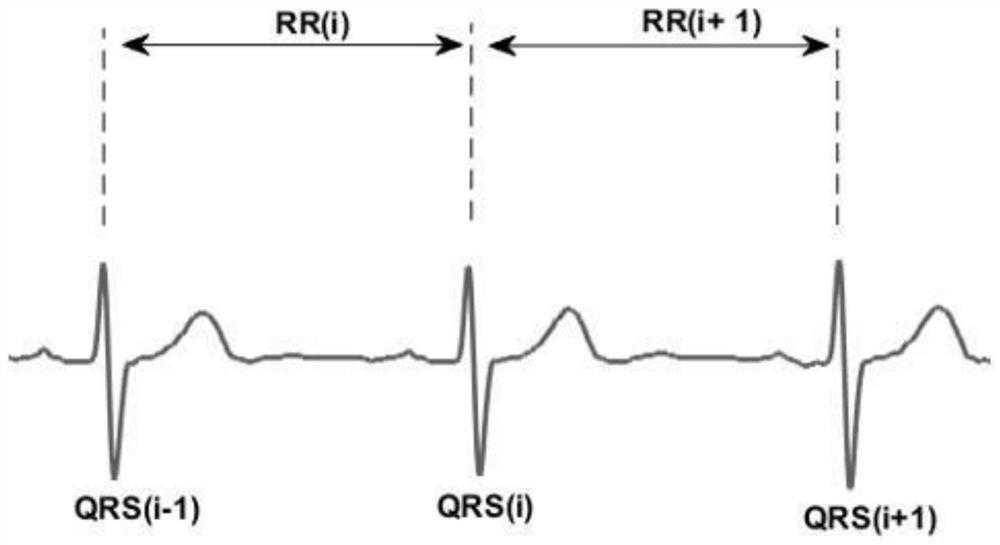

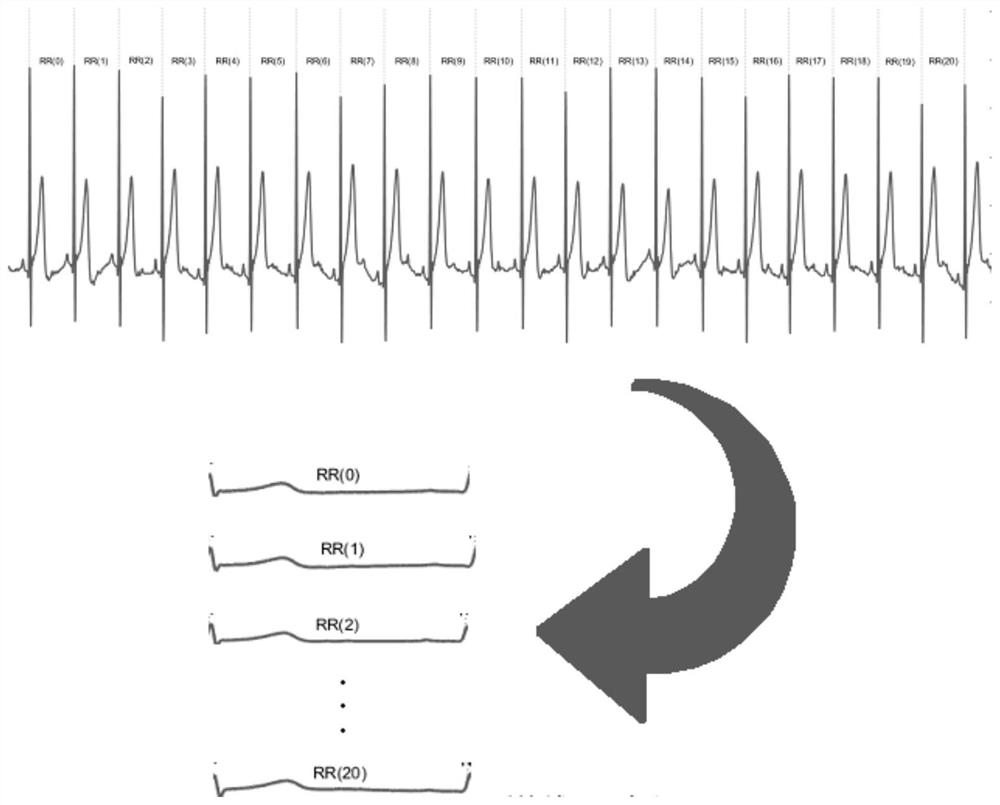

Atrial fibrillation event detection method based on deep learning

PendingCN111803062AImprove data reading speedImprove accuracyMedical imagingDiagnostic recording/measuringData subjectHeart beat

The invention provides an atrial fibrillation event detection method based on deep learning. The method can break through the constraint of insufficient features of a traditional atrial fibrillation detection algorithm and further improve the accuracy. The method comprises the following steps: S1, acquiring an electrocardiosignal for training an atrial fibrillation event detection deep learning model, and then performing preprocessing operation on the electrocardiosignal to remove interference and invalid data; S2, performing QRS detection processing on the preprocessed electrocardiosignal toextract heart beat information in the electrocardiosignal; S3, according to the QRS detection processing result, performing electrocardio dimension-increasing transformation processing; S4, building adeep learning model according to the data subjected to the dimension increasing transformation processing; and S5, carrying out training set and test set data division on the data set subjected to the dimension-increasing transformation processing through a five-fold cross validation method, and then carrying out training of the deep learning model through the training set data to finally obtainan atrial fibrillation detection model.

Owner:江苏正心智能科技有限公司

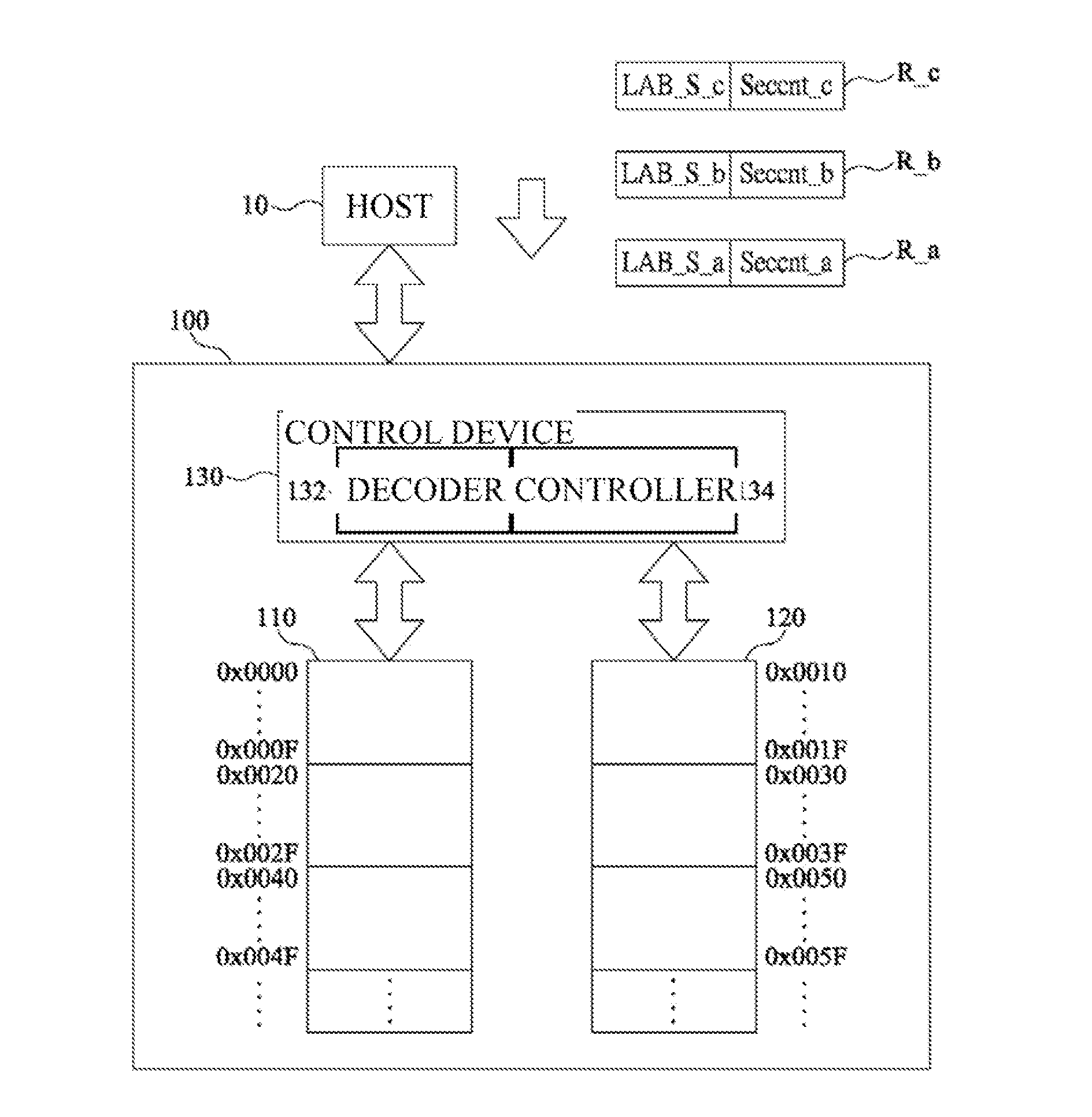

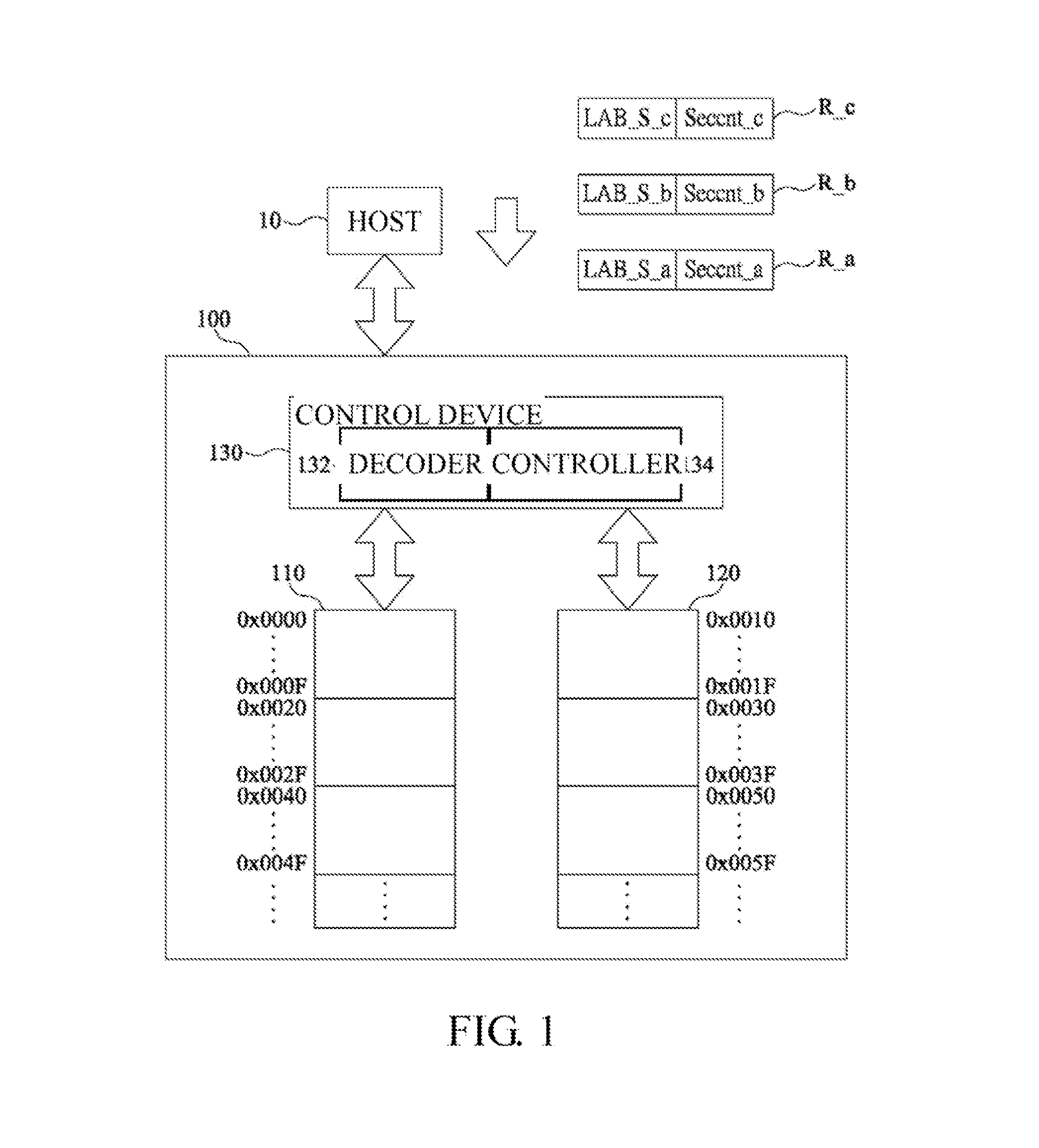

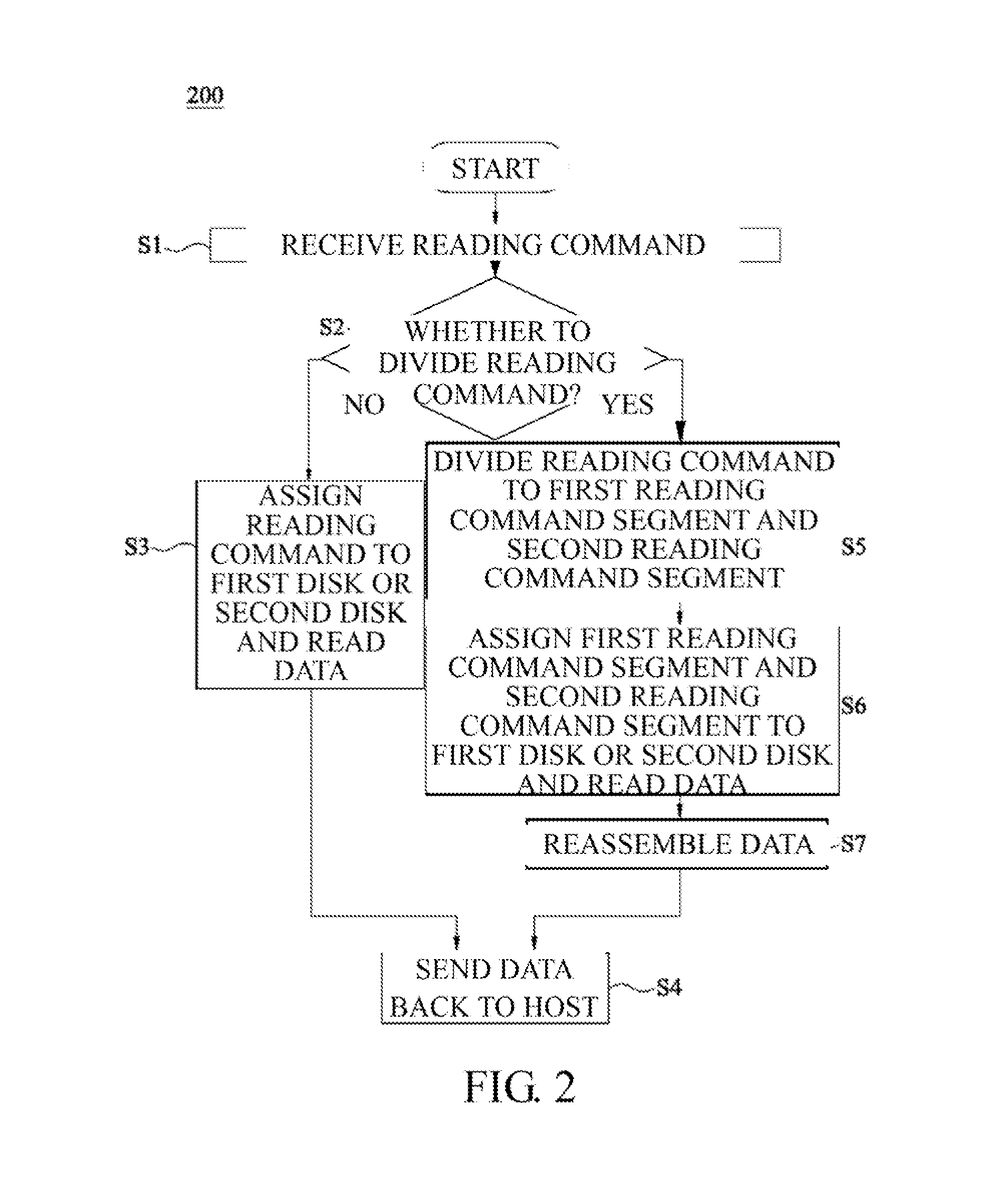

Disk array system and data processing method

ActiveUS20140351509A1Extended service lifeImprove data reading speedMemory architecture accessing/allocationInput/output to record carriersRAIDDisk array

A disk array system and a data processing method are provided. The data processing method is applied to the disk array system. The disk array system is a redundancy array of independent disk 0 (RAID 0) system The disk array system includes a plurality of disks. The data processing method includes: receiving a reading command; determining whether to divide the reading command to a plurality of reading command segments according to the reading command; and assigning the reading command to a corresponding disk of the disks to read data stored in the corresponding disk accordingly when it is determined that the reading command is not divided.

Owner:ASMEDIA TECHNOLOGY INC

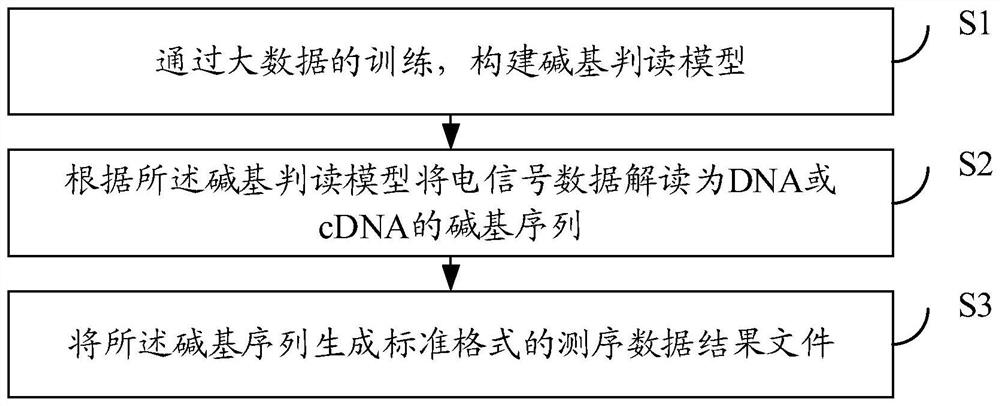

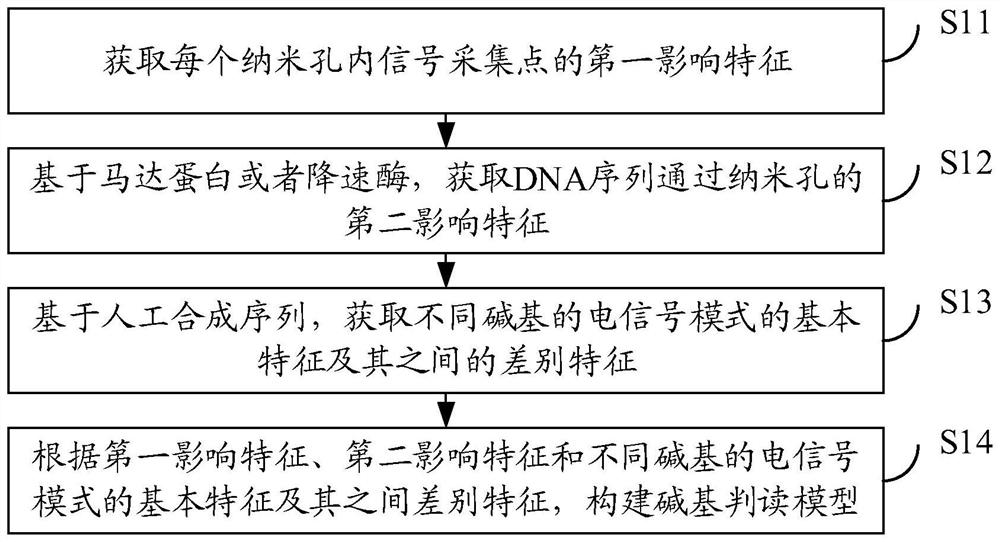

Base interpretation method based on nanopore electric signal, interpretation equipment and storage medium

InactiveCN112309503AImprove throughputReduced speed through the nanoporeMicrobiological testing/measurementBiostatisticsHigh fluxComputer science

The invention discloses a base interpretation method based on a solid nanopore electric signal, interpretation equipment and a storage medium. The method comprises the steps: constructing a base interpretation model through big data training; interpreting the electric signal data into a base sequence of DNA or cDNA according to the base interpretation model; and generating a sequencing data resultfile in a standard format from the base sequence. Through the embodiment of the invention, independent sequencing of each DNA molecule can be realized, PCR (Polymerase Chain Reaction) amplification is not needed, and meanwhile, the method has higher data reading speed and longer sequencing sequence reading length, and has the advantages of high flux, low cost and long reading length.

Owner:SHENZHEN RUHAN GENE SCI & TECH LTD

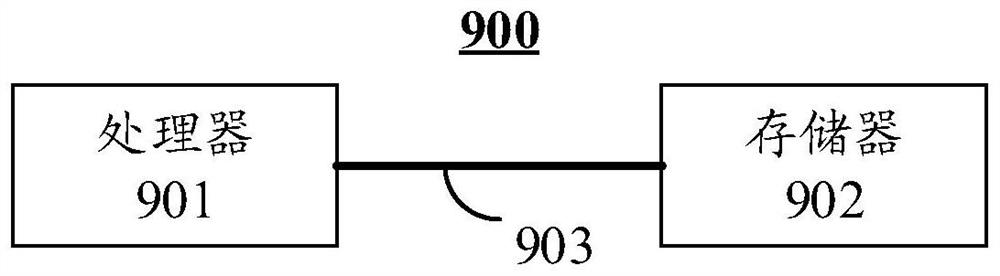

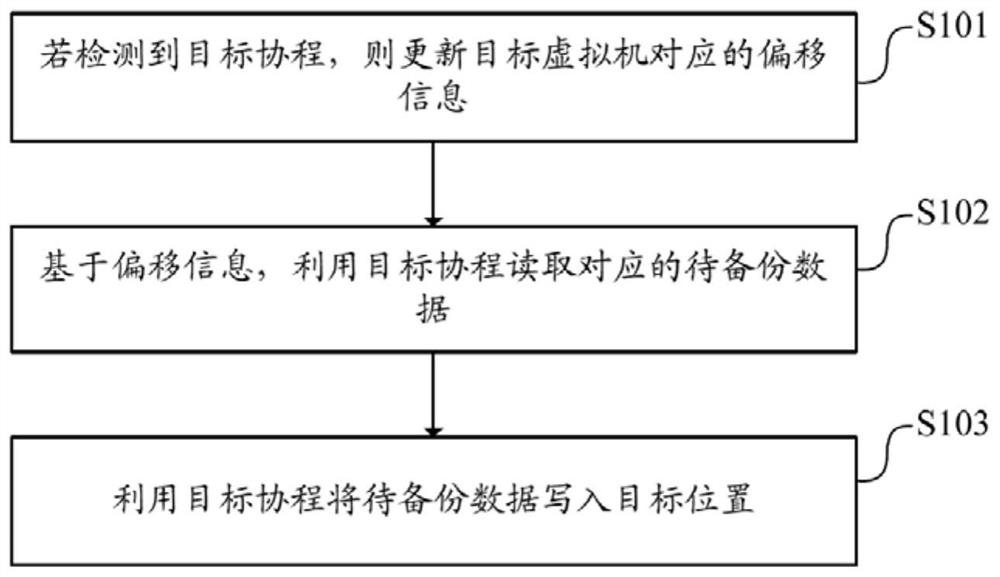

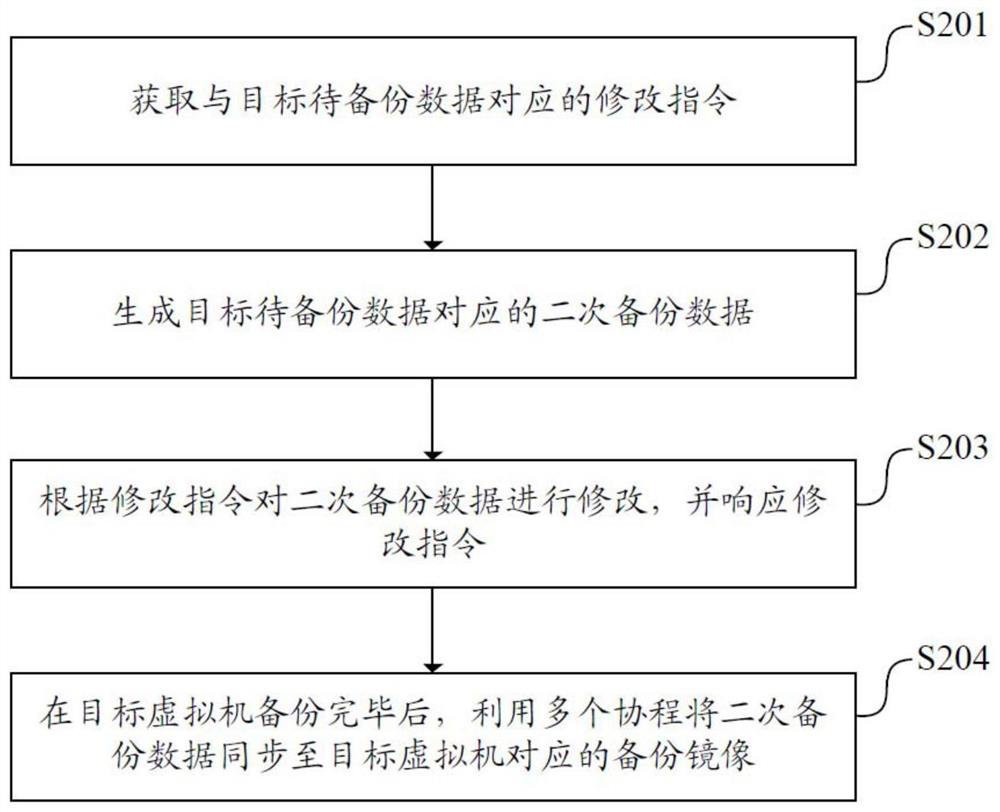

Virtual machine backup method and device, electronic equipment and readable storage medium

PendingCN112395050AImplement concurrent processingHigh speedSoftware simulation/interpretation/emulationRedundant operation error correctionSoftware engineeringProcessing

The invention discloses a virtual machine backup method and device, electronic equipment and a computer readable storage medium, and the method comprises the steps: updating offset information corresponding to a target virtual machine if a target coroutine is detected, wherein the target coroutine is any coroutine in an idle state in the plurality of coroutines; based on the offset information, reading corresponding to-be-backed-up data by utilizing the target coroutine; writing the to-be-backed-up data into the target position by utilizing the target coroutine; according to the method, in theprocess that a target coroutine reads to-be-backed-up data, other coroutines can also read the data; or read data can be written into the target coroutine, and other coroutines can read or write thedata in the process of writing the data into the target coroutine, so that concurrent processing of virtual machine backup is realized; and multiple coroutines are subjected to concurrent processing,so that the data reading speed and the data writing speed are greatly increased, the virtual machine backup speed is increased, and the backup time is shortened.

Owner:SANGFOR TECH INC

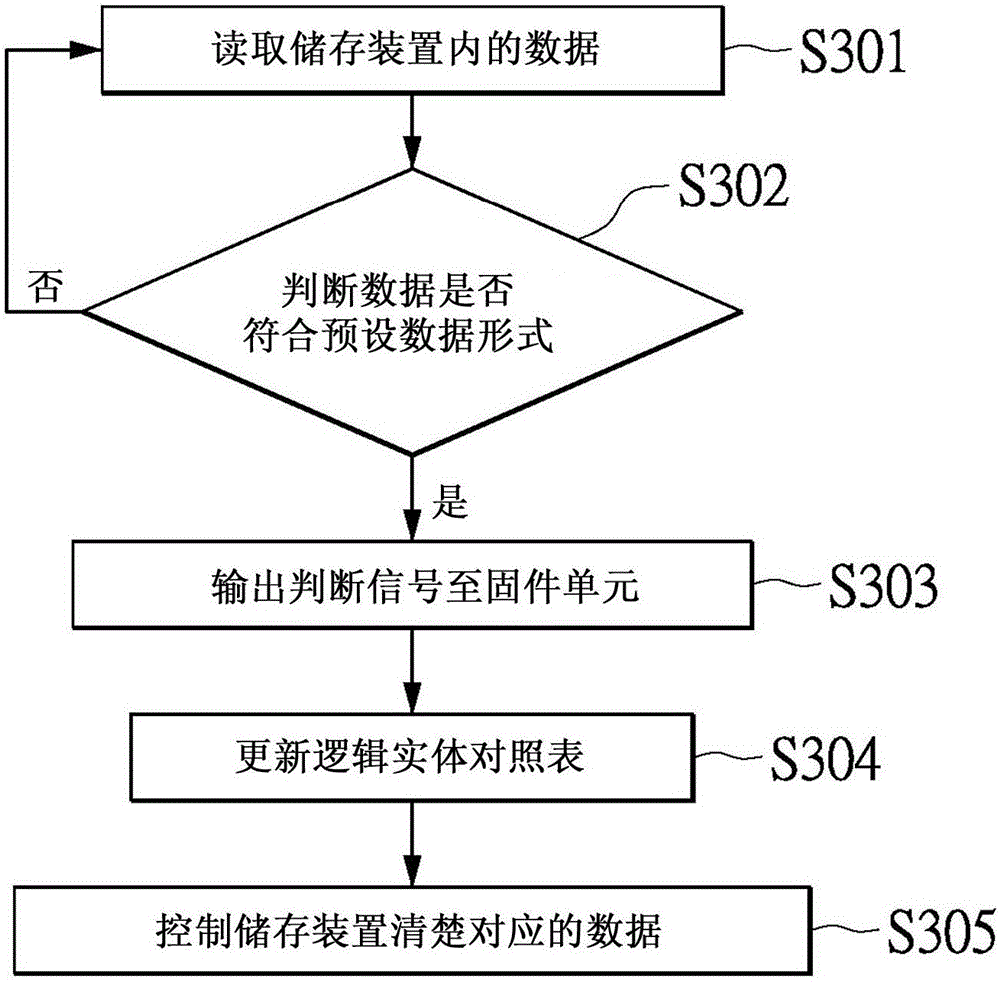

Method and device for layer and grade type data reading

ActiveCN104298670AImprove performanceImprove data reading speedWebsite content managementHierarchical databasesInternet privacyData store

Owner:TENCENT TECH (BEIJING) CO LTD

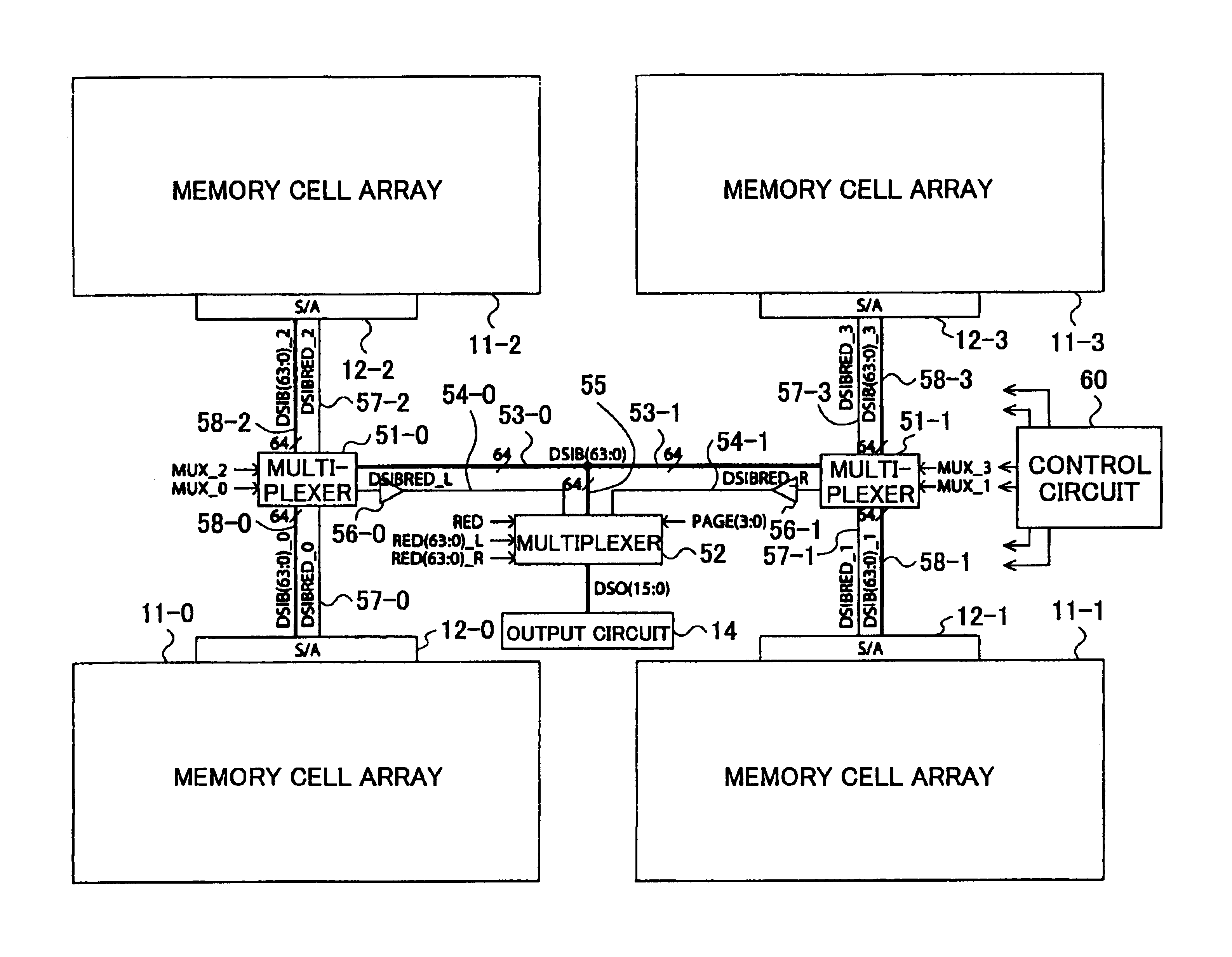

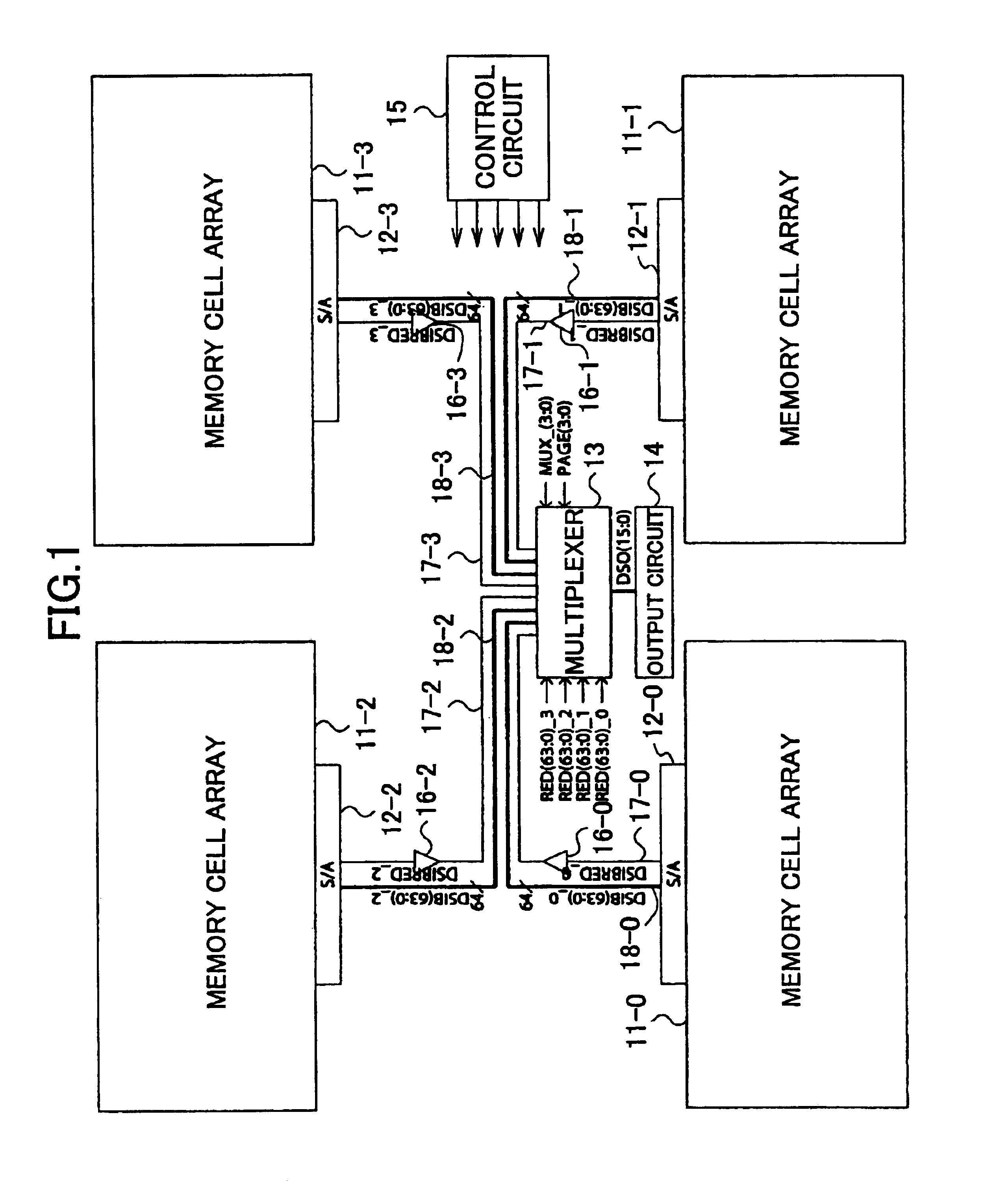

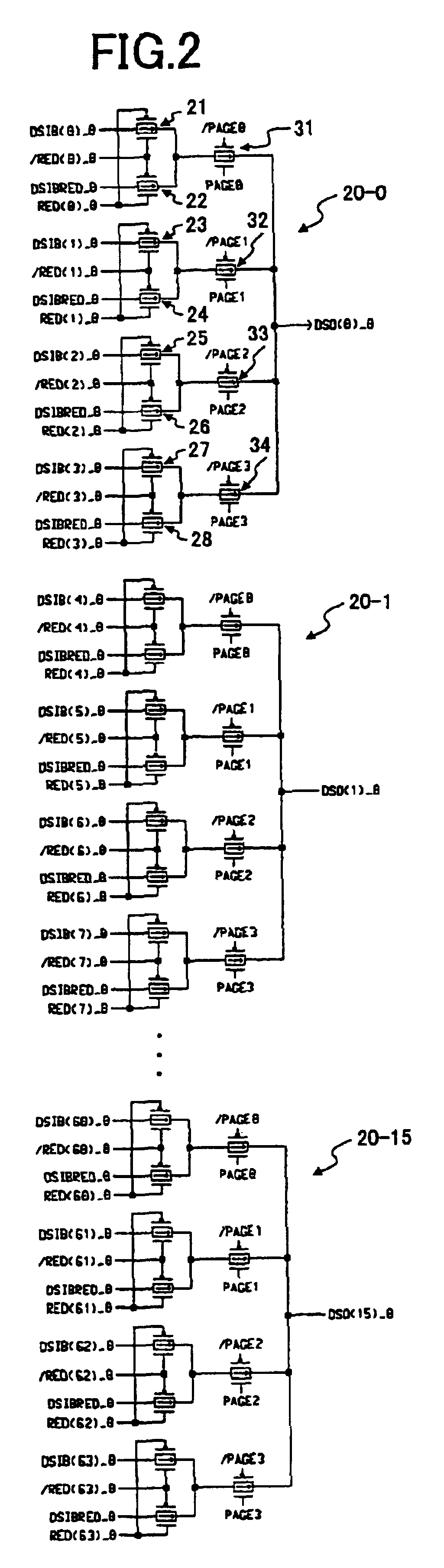

Semiconductor memory device with memory cell array divided into blocks

A semiconductor memory device includes a plurality of blocks, each of which includes a memory cell array, and outputs data signals and a redundancy signal. The semiconductor memory device further includes at least one first multiplexer which is coupled to the blocks, and selects one of the blocks, and a second multiplexer which performs redundancy processing based on the data signals and the redundancy signal which have undergone block selection by the first multiplexer.

Owner:FUJITSU SEMICON LTD

Thin film magnetic memory device including memory cells having a magnetic tunnel junction

InactiveUS20080117670A1Improve data reading speedGain is not constantMagnetic-field-controlled resistorsSolid-state devicesComputer hardwareBit line

In the data read operation, a memory cell and a dummy memory cell are respectively coupled to two bit lines of a selected bit line pair, to which a data read current is supplied. In the selected memory cell column, a read gate drives the respective voltages on a read data bus pair, according to the respective voltages on the bit lines. A data read circuit amplifies the voltage difference between the read data buses so as to output read data. The use of the read gate enables the read data buses to be disconnected from a data read current path. As a result, respective voltage changes on the bit lines are rapidly produced, and therefore, the data read speed can be increased.

Owner:RENESAS TECH CORP

Memorization body and operation method thereof

ActiveCN101276639AImprove data reading speedReduce the generation of data gapsDigital storageVoltageComputer hardware

The invention relates to a memory element and an operation method of the same. According to the invention, a plurality of memory storage libraries are divided into a plurality of memory groups, wherein, each memory group is equipped with an independent driving power supply for providing an operation voltage to the corresponding memory storage library. Two kinds of row-to-row relay time are set as an external interval and an internal interval respectively. A minimal interval of one row to another row in a same memory group is selected as the internal interval, a minimal interval between rows of different memory groups is selected as the external interval, wherein the external interval is less than or equal to the internal interval. The memory element of the invention is capable of improving data reading speed of the memory element, reducing generation of data slots, and avoiding waste of system data.

Owner:NAN YA TECH

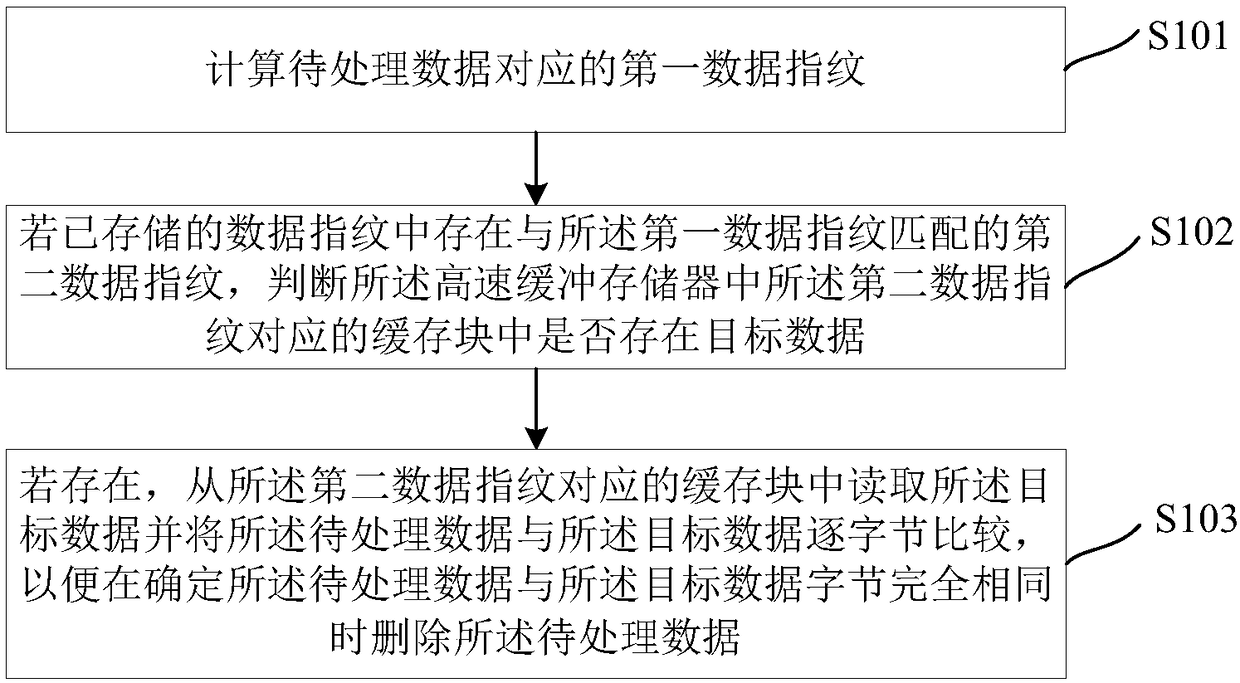

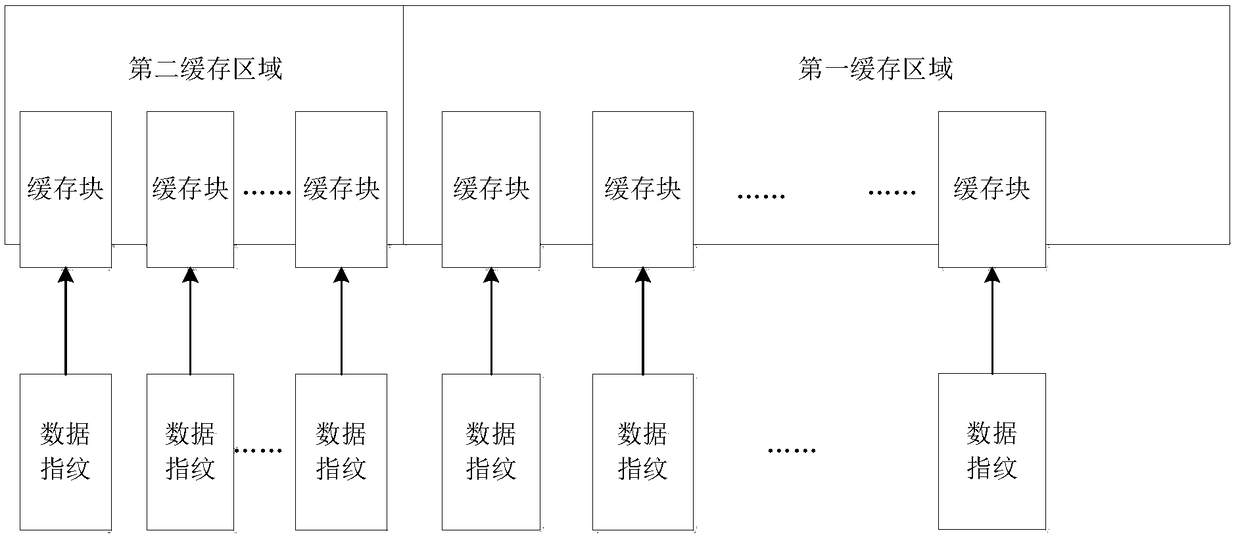

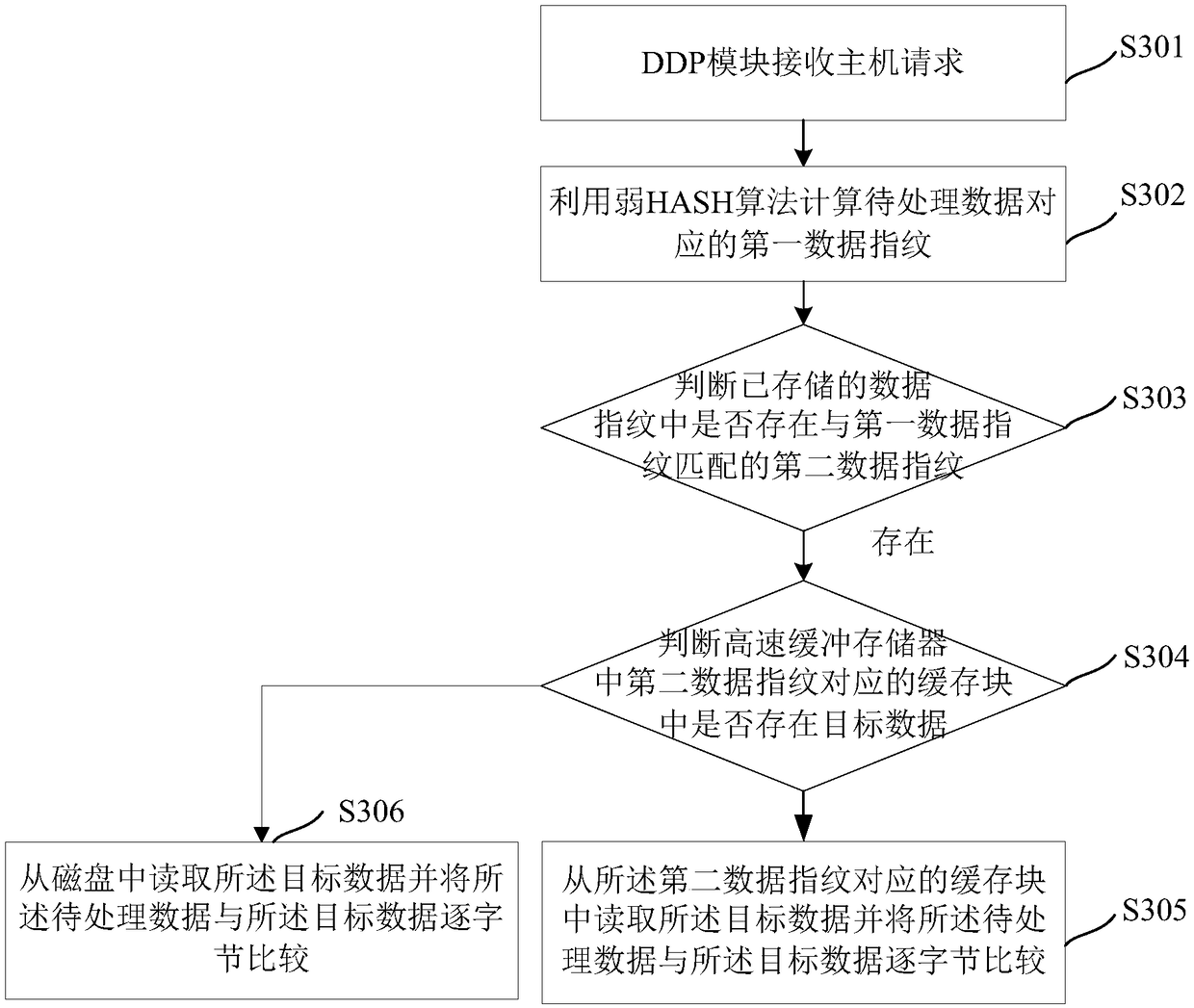

A method and a device for deleting duplicate data

InactiveCN108984123AImprove data reading speedImprove efficiencyInput/output to record carriersFingerprintData deduplication

The embodiment of the invention discloses a method and a device for deleting duplicate data. The method include: when determining whether the data to be processed needs to be deleted, obtaining a corresponding relationship between a data fingerprint stored in a cache memory and a buffer block storing the data, and if the data to be processed is obtained, calculating a first data fingerprint of thedata to be processed is calculated; if there is a second data fingerprint matched with the first data fingerprint in the stored data fingerprint, preferentially judging whether there is target data in the buffer block corresponding to the second data fingerprint in the cache memory; if there is, reading the target data from the buffer block corresponding to the second data fingerprint without reading the target data from the disk, and comparing the data to be processed with the target data byte by byte so as to delete the data to be processed when it is determined that the data to be processed is identical to the bytes of the target data. The method preferentially reads target data from a cache memory, reduces the number of disk reads, improves the data reading speed, and improves the efficiency of deleting duplicate data.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

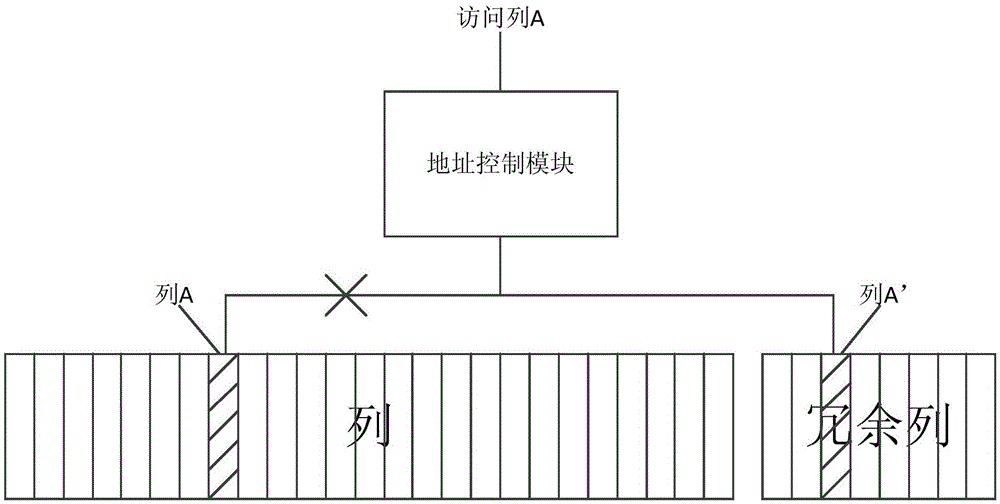

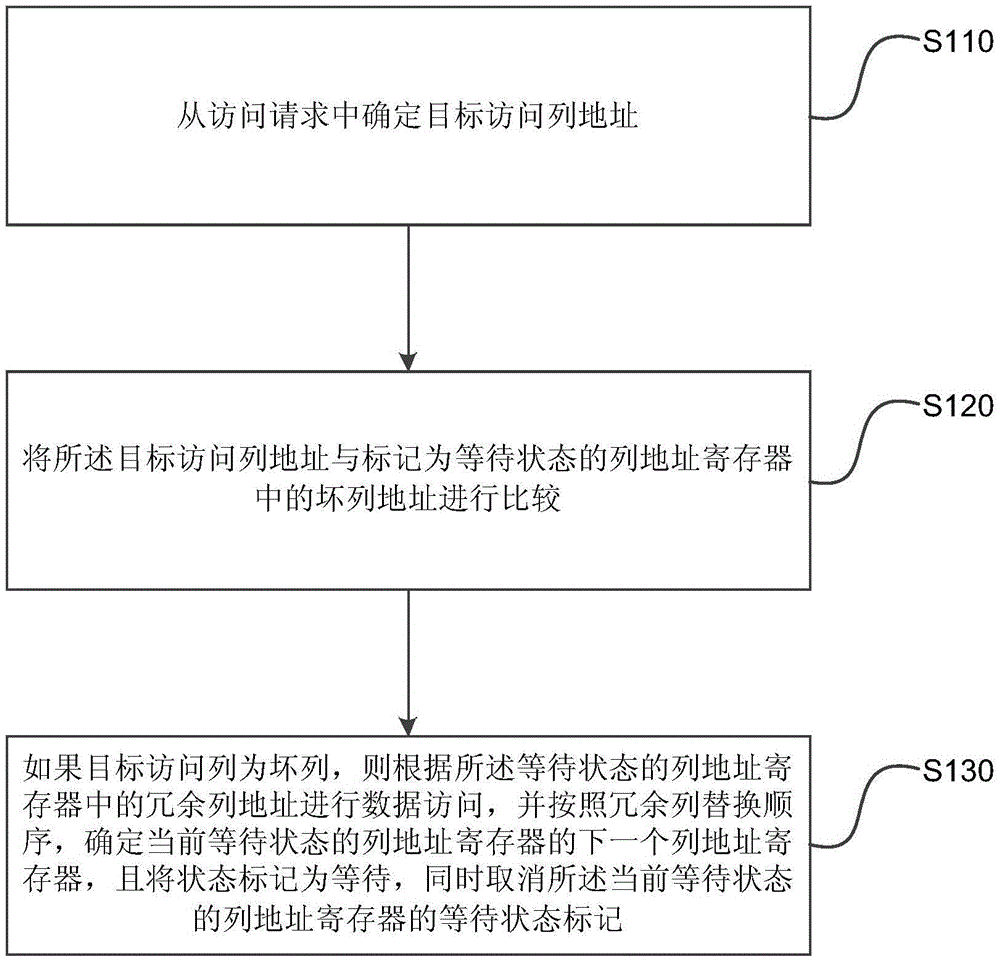

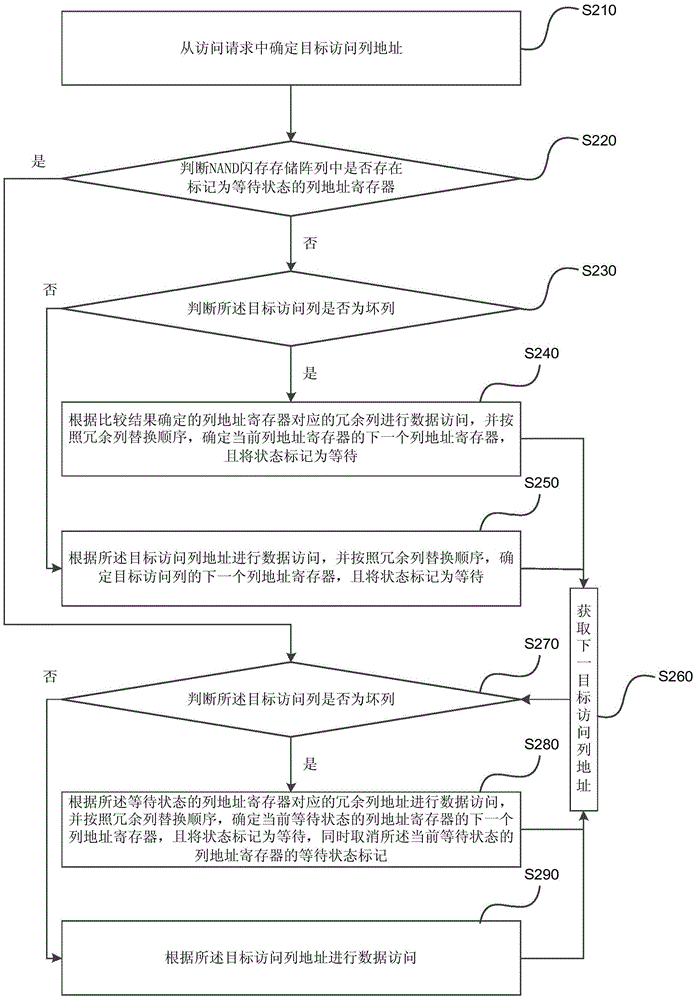

NAND flash memory data reading method and device and NAND flash memory

ActiveCN105677246AImprove data reading speedReduce waiting timeInput/output to record carriersMemory adressing/allocation/relocationProcessor registerData access

The embodiment of the invention discloses an NAND flash memory data reading method and device and an NAND flash memory. The method includes the steps that an object access column address is determined in an access request; the object access column address is compared with a bad column address in a column address register marked in a waiting state; if the object access column address is a bad column, data access is conducted according to a redundancy column address corresponding to the column address register in the waiting state, the next column address register of the current column address register in the waiting state is determined according to a redundancy column substituting sequence, the next column address register is marked to be in a waiting state, and meanwhile a waiting state marker of the current column address register in the waiting state is canceled. By adopting the technical scheme in the embodiment, data reading speed of the NAND flash memory can be increased, waiting time of a user is shortened, and user experience is improved.

Owner:GIGADEVICE SEMICON (BEIJING) INC

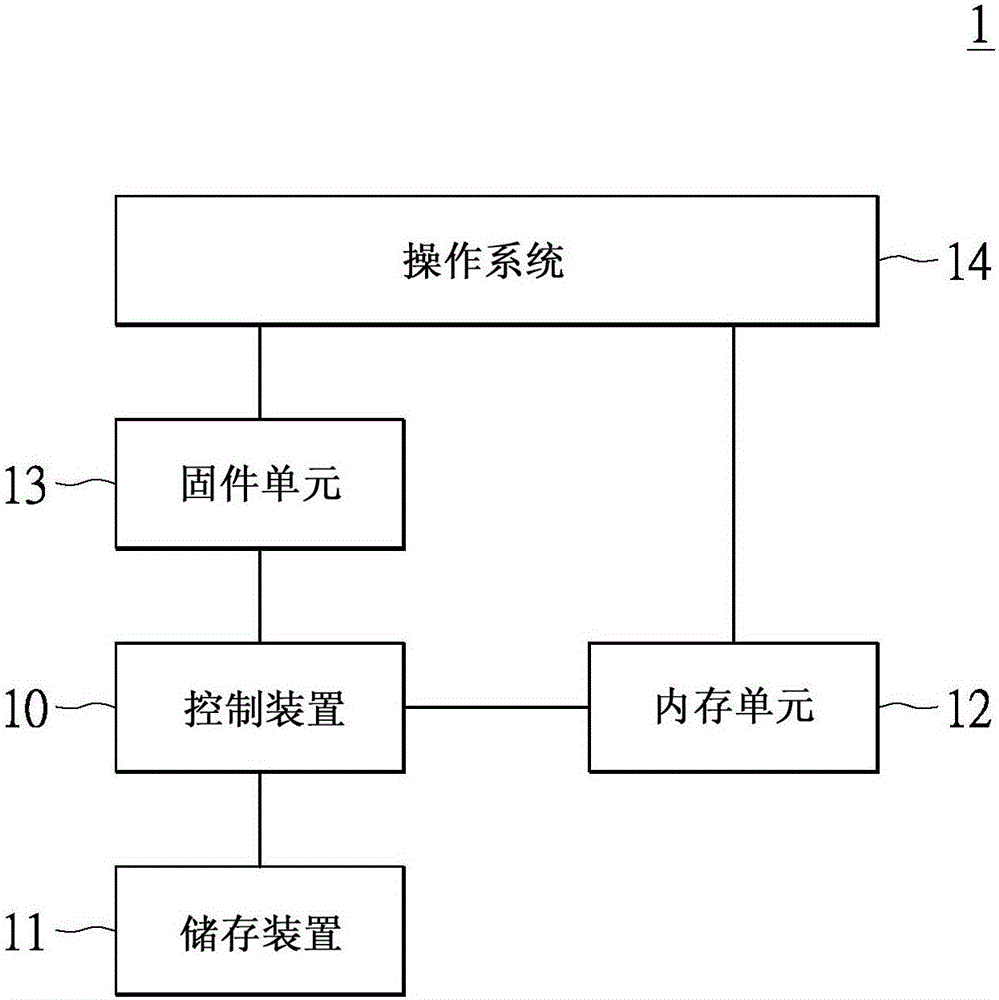

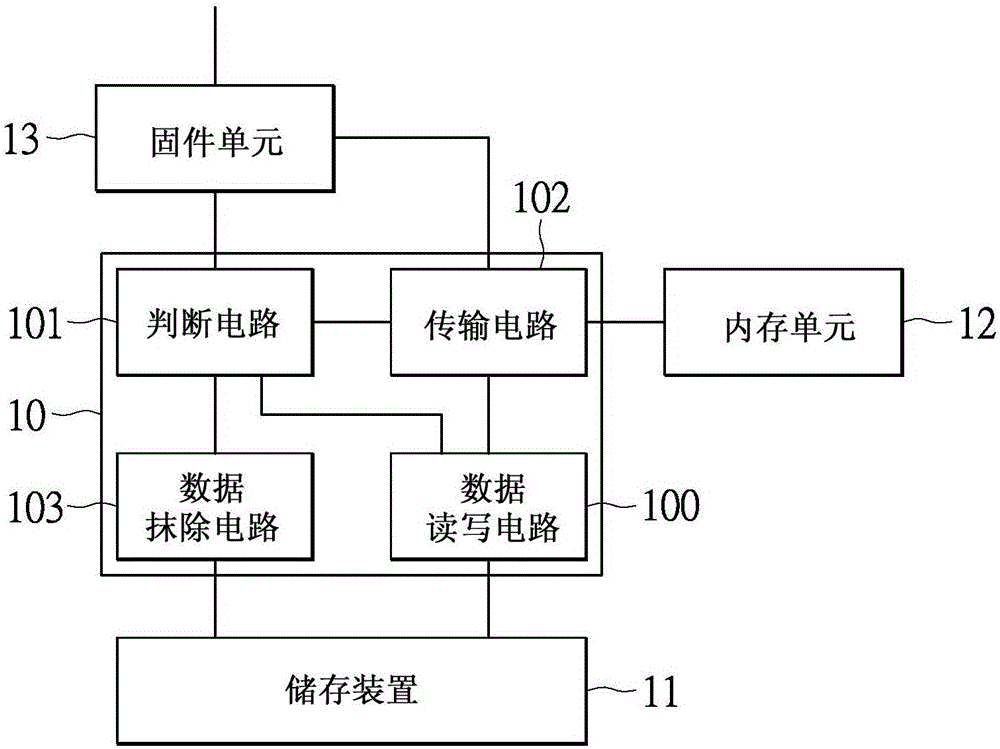

Control device of storage system and storage space recovery method of storage system

ActiveCN107436729AExtend your lifeImprove data reading speedInput/output to record carriersRecovery methodDummy data

The invention provides a control device of a storage system and a storage space recovery method of the storage system. The control device comprises a data read-write circuit and a judgment circuit, wherein the judgment circuit is coupled to the data read-write circuit, and the data read-write circuit reads data stored in a storage device. The judgment circuit receives the data and judges whether the data accords with one of multiple preset data forms or not. When the data accords with one of the preset data forms, the judgment circuit outputs a judgment signal to a firmware unit. The firmware unit updates a logical entity comparison table according to the judgment signal, and a logic address of the data points to one of a plurality of dummy data spaces of a memory unit. The dummy data spaces store the preset data forms respectively. Finally, a control device controls the storage device to remove data.

Owner:RAYMX MICROELECTRONICS CORP

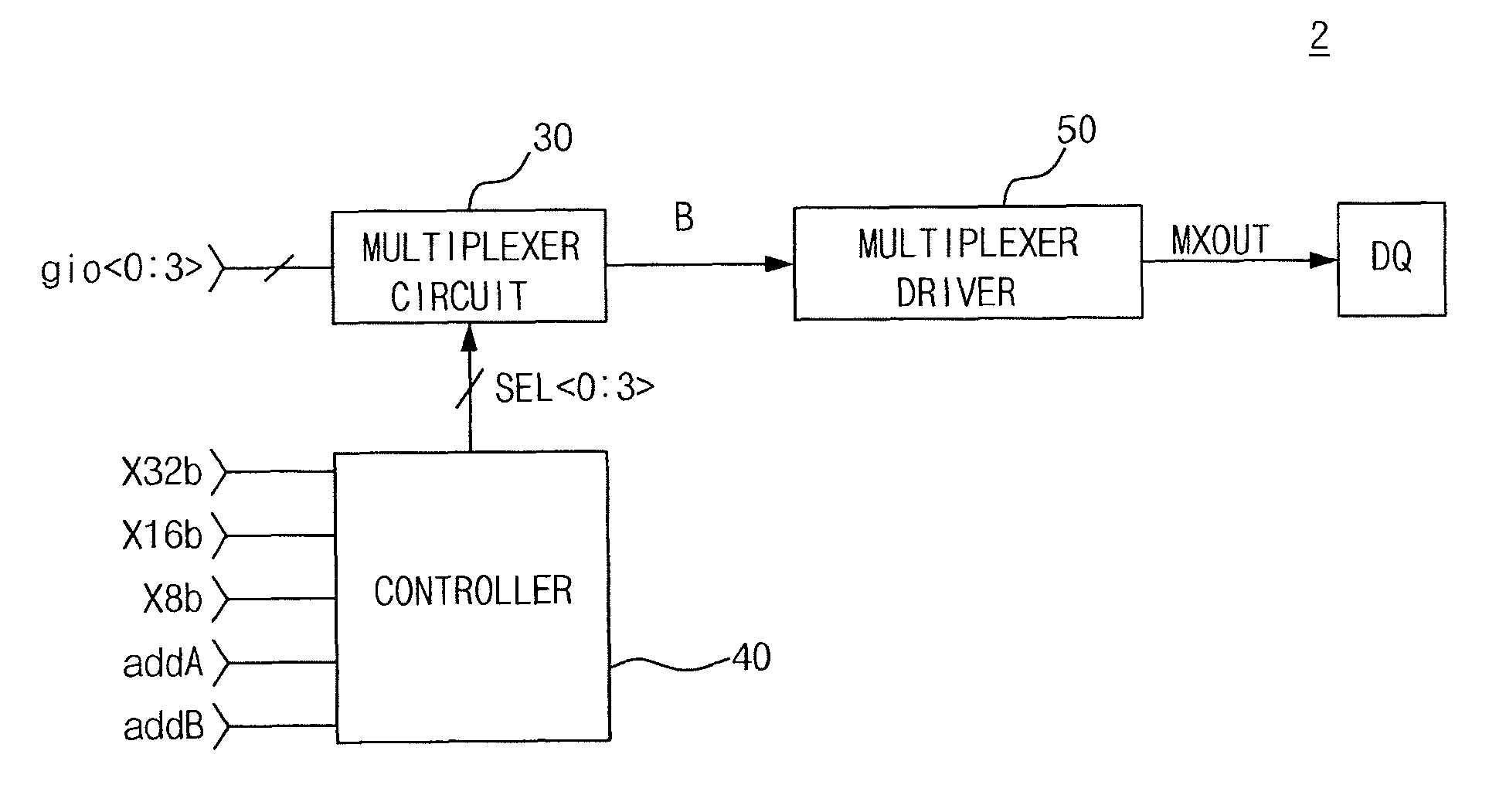

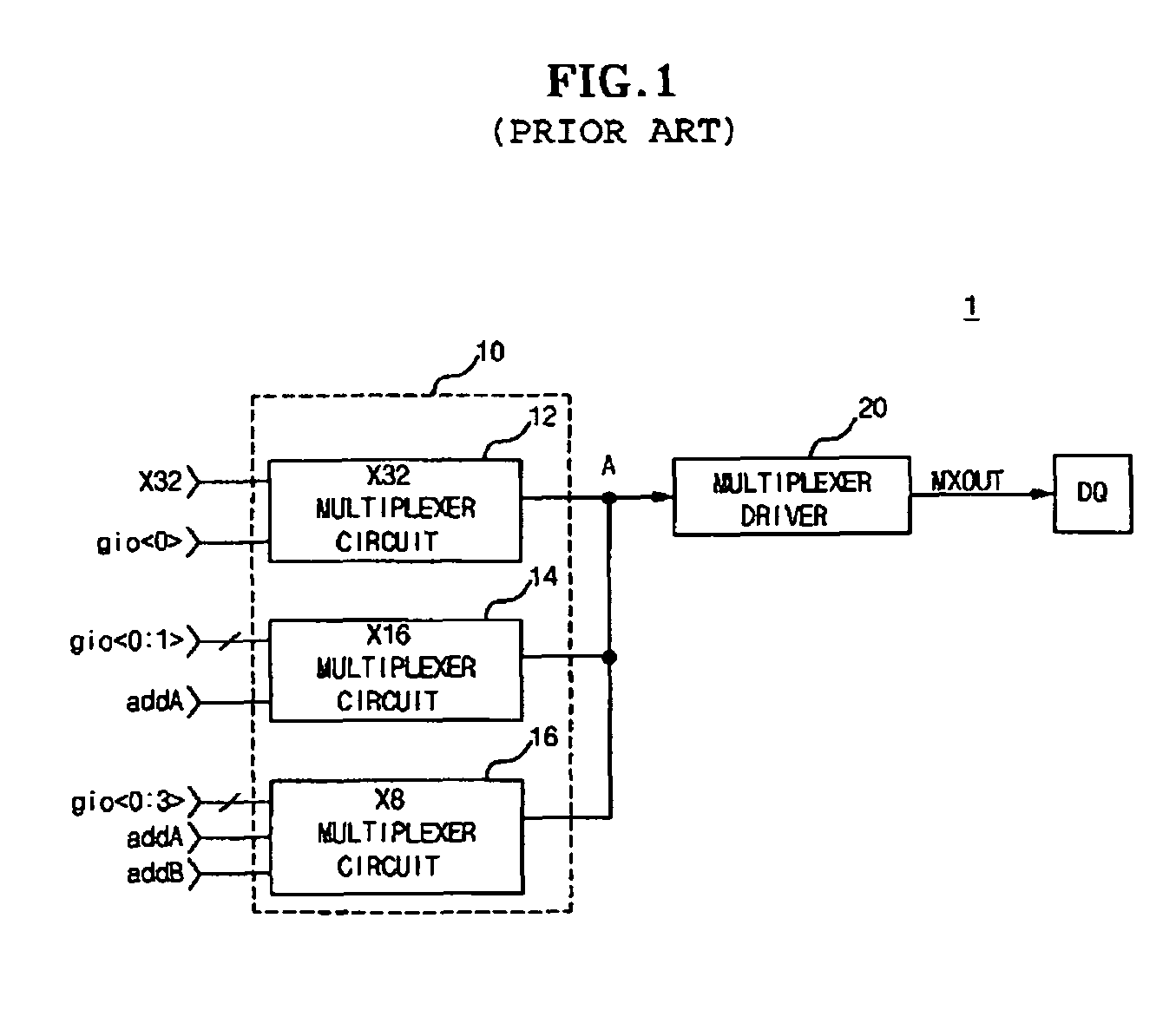

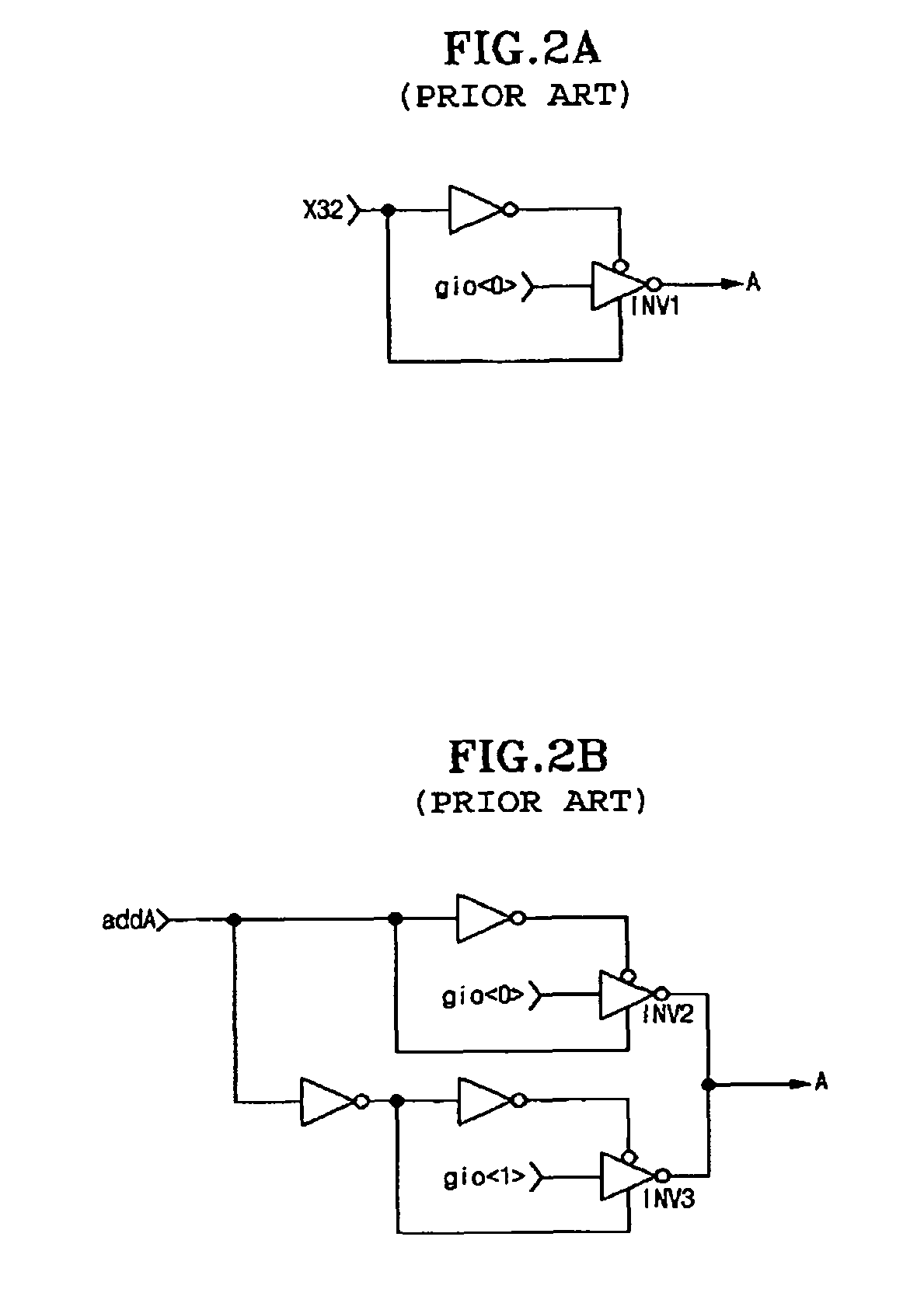

Data output circuit for semiconductor memory device

The present invention relates to a semiconductor memory, and more specifically, to a data output circuit capable of differentiating global data lines in accordance to an operation mode to output them to a data input / output pin. The present invention includes: a multiplexer selecting any one of a plurality of global input / output lines which can receive variable data bandwidth directed by control signals and which can output data carried on the selected global input / output line, and a controller generating the control signals in accordance to operation mode signals corresponding to a data bandwidth and address signals provided for selecting data and providing them to the multiplexer. Thereby, the present invention can realize an improved data read speed by reducing the loading of the global input / output line.

Owner:SK HYNIX INC