Thin film magnetic memory device including memory cells having a magnetic tunnel junction

a magnetic memory, thin film technology, applied in semiconductor devices, digital storage, instruments, etc., can solve the problems of degrading the operation reliability of the mram device, mtj memory cells having such characteristics are extremely susceptible to magnetic noise, and the data read speed cannot be increased, so as to reduce the amount of data write current, and improve the operation reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

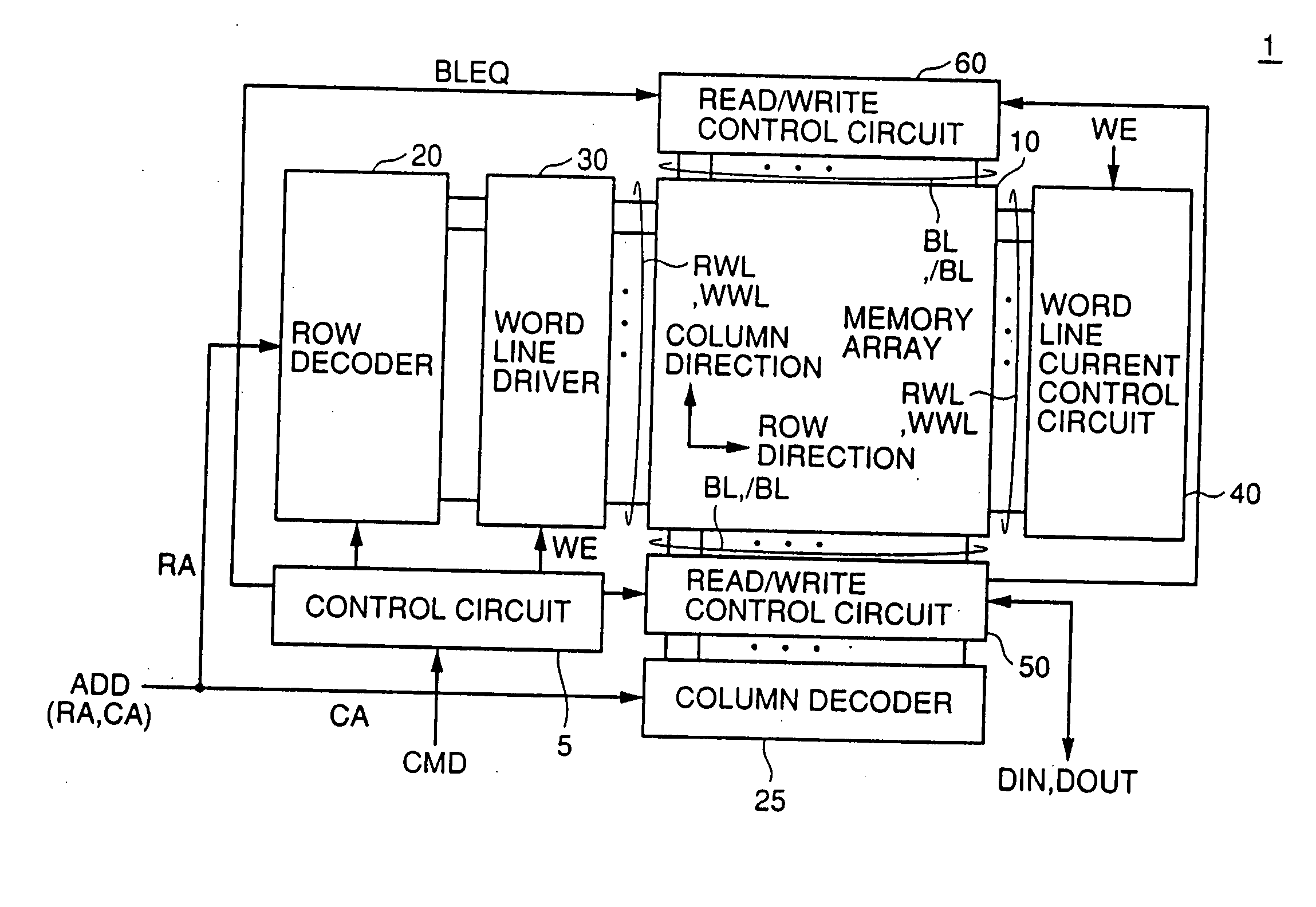

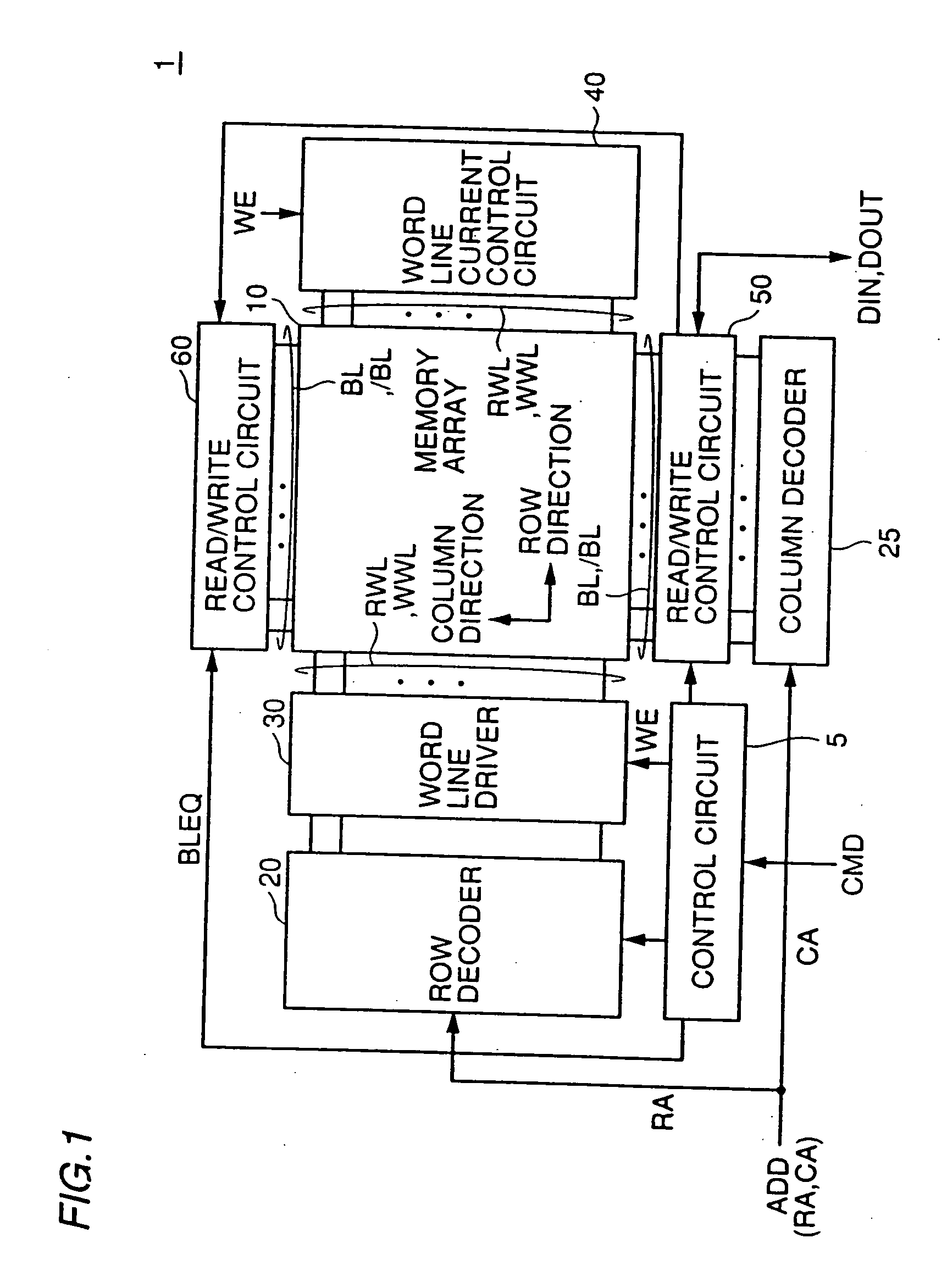

[0162] Referring to FIG. 1, an MRAM device 1 according to the first embodiment of the present invention conducts random access in response to an external control signal CMD and address signal ADD, thereby conducting input of write data DIN and output of read data DOUT.

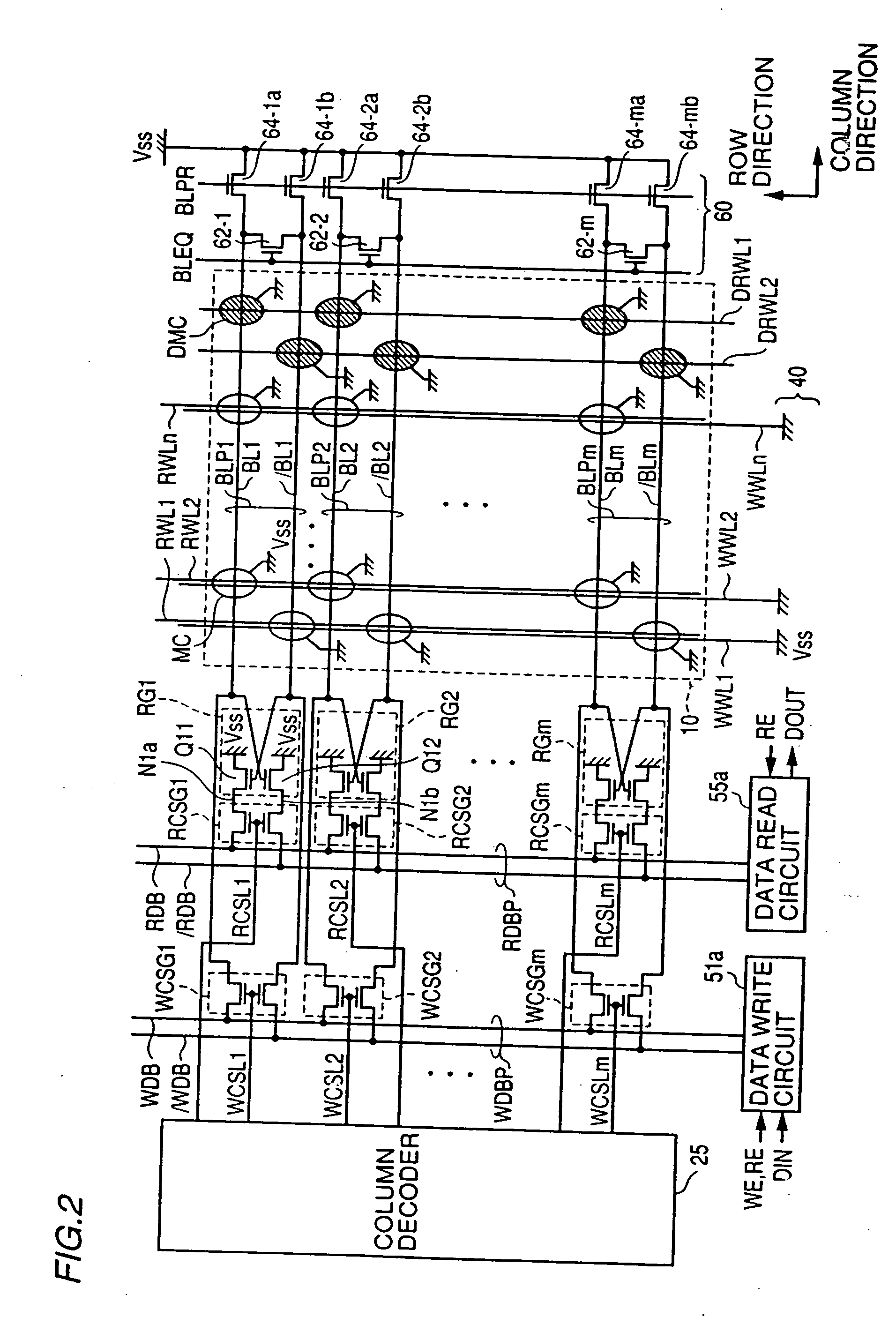

[0163] The MRAM device 1 includes a control circuit 5 for controlling the overall operation of the MRAM device 1 in response to the control signal CMD, and a memory array 10 having a plurality of MTJ memory cells arranged in n rows by m columns. Although the structure of the memory array 10 will be described later in detail, a plurality of write word lines WWL and a plurality of read word lines RWL are provided corresponding to the respective MTJ memory cell rows. Folded bit line pairs are provided corresponding to the respective MTJ memory cell columns. Each bit line pair is formed from bit lines BL and / BL. Note that, hereinafter, a set of bit lines BL and / BL is also generally referred to as a bit line pair BLP.

[0...

second embodiment

Modification of Second Embodiment

[0290] Referring to FIG. 14, a data write current adjustment circuit 230 according to the modification of the second embodiment outputs a reference voltage Vref for adjusting the amount of the data write current. Note that the data write current adjustment circuit 230 shown in FIG. 13 may be replaced either with the data write current adjustment circuit 200 for adjusting the data write current ±Iw to be supplied to the bit line or with the data write current adjustment circuit 21 for adjusting the data write current Ip to be supplied to the write word line.

[0291] Referring to FIG. 14, the data write current adjustment circuit 230 includes a tuning input portion 231a and a voltage adjustment portion 231b for adjusting the reference voltage Vref according to the setting of the tuning input portion 231a.

[0292] The voltage adjustment portion 231b includes a P-channel MOS transistor 232 electrically coupled between a node Nt1 producing the reference vol...

third embodiment

[0321] In the third embodiment is described the structure in which the bit lines BL and write word lines WWL receiving the data write current are formed in a plurality of wiring layers.

[0322]FIG. 16 shows the bit line arrangement according to the third embodiment of the present invention.

[0323] Referring to FIG. 16, the data write and read operations to and from the memory array 10 are conducted through the data I / O line pair DI / OP by the data write circuit 51b and the data read circuit 55d, respectively, based on the same structure as that of FIG. 15.

[0324] The bit lines BL1 to BLm, / BL1 to / BLm forming the bit line pairs BLP1 to BLPm, column selection gates CSG1 to CSGm, and column selection lines CSL1 to CSLm are provided corresponding to the respective memory cell columns.

[0325] The bit lines BL1 to BLm are formed in a wiling layer different from that of the bit lines / BL1 to / BLm. For example, the bit lines BL1 to BLm are each formed in a metal wiring layer M3, whereas the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More