Patents

Literature

31results about How to "Lower Input Offset Voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

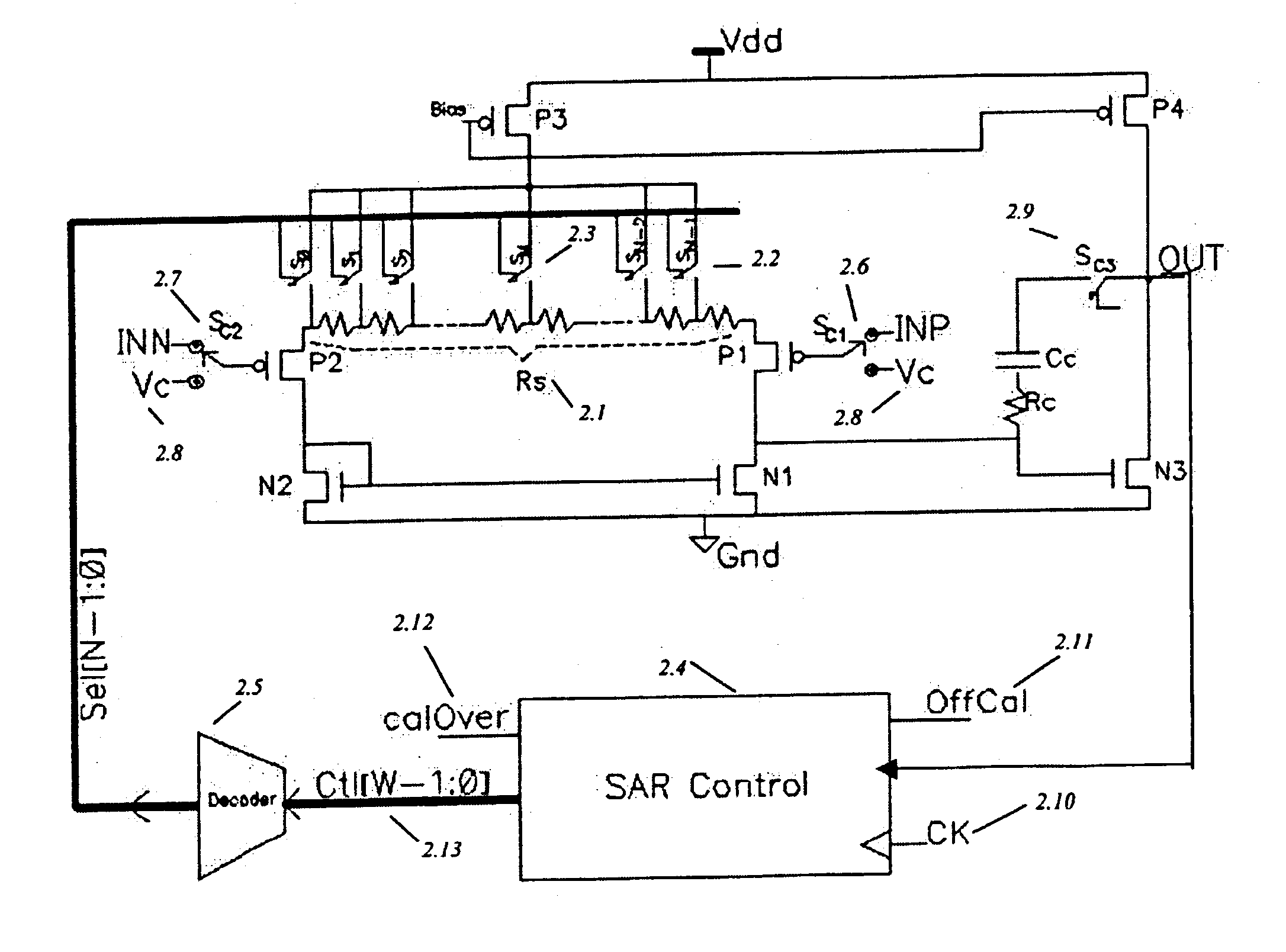

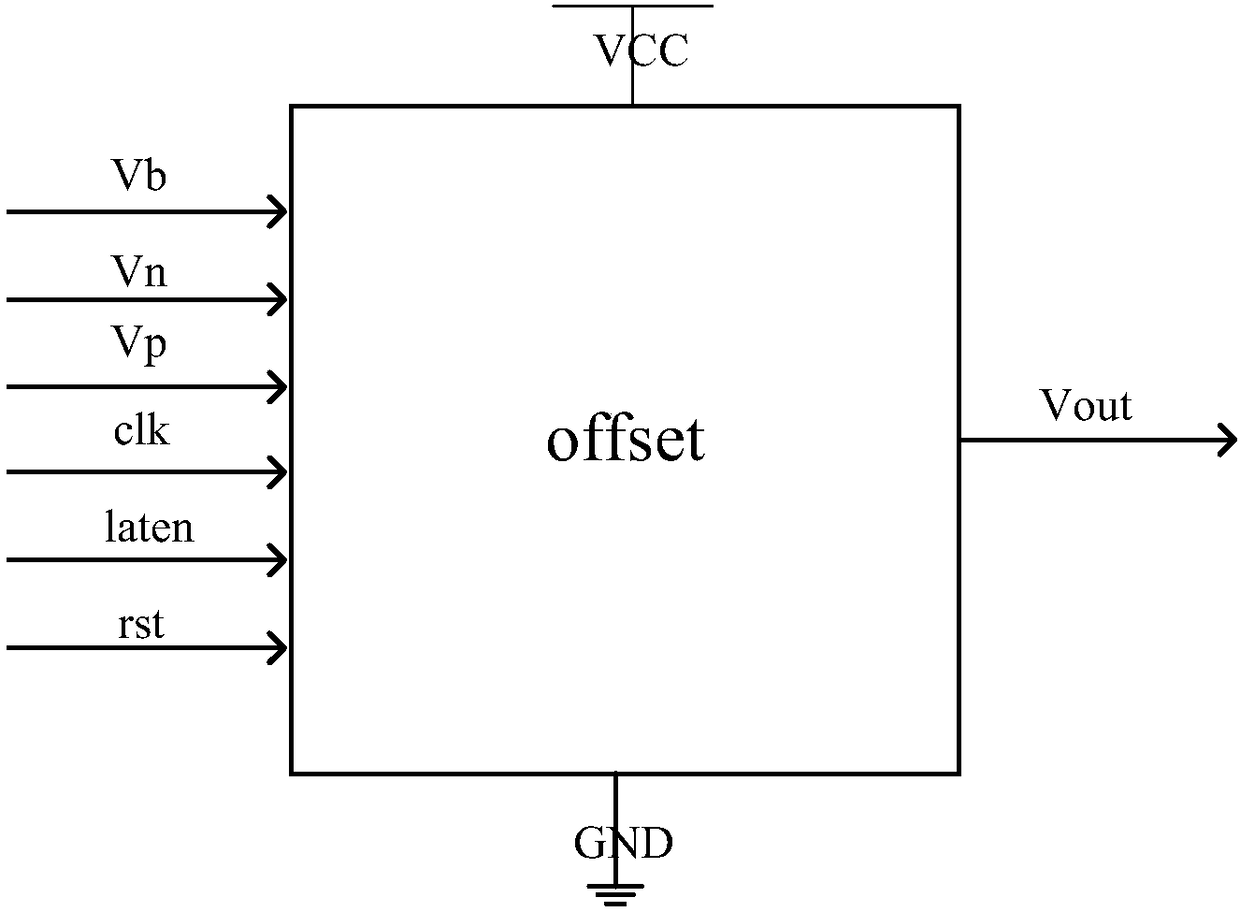

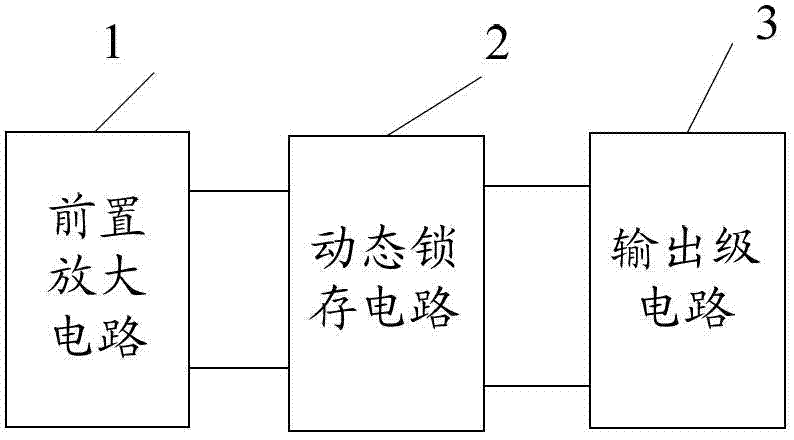

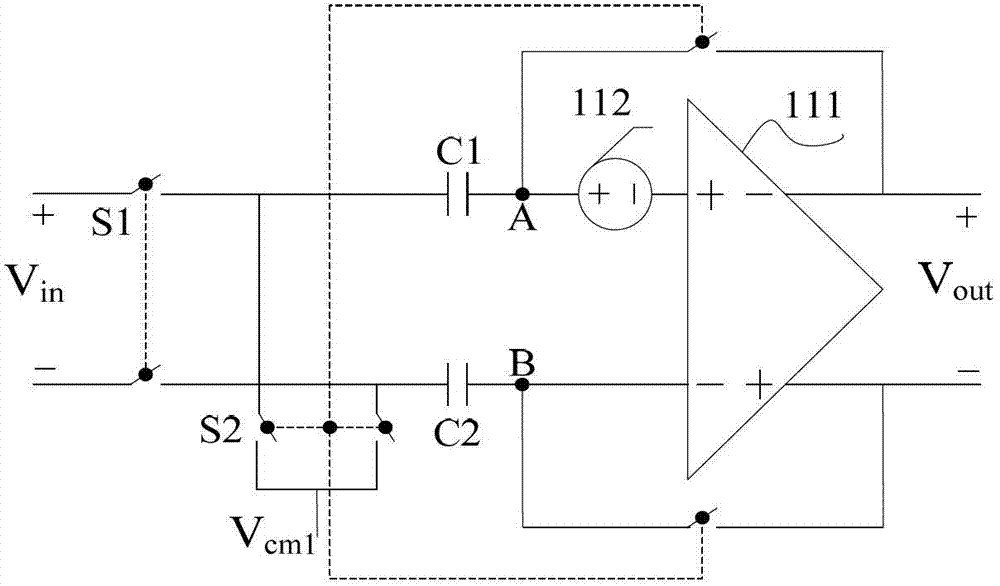

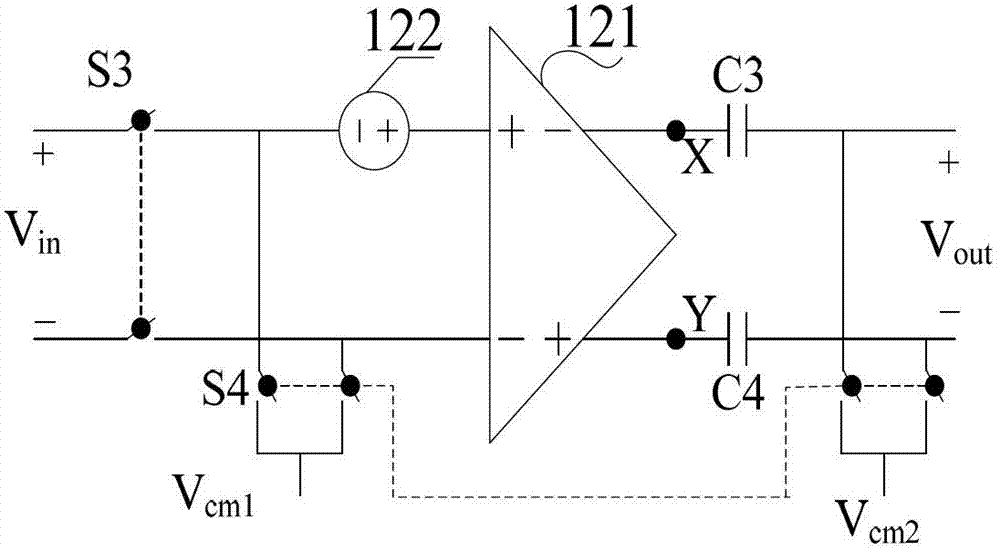

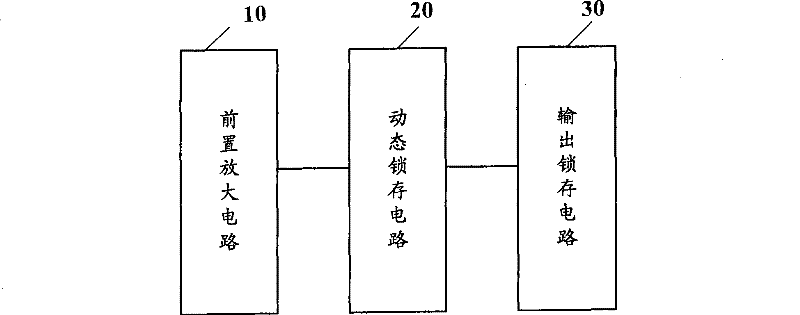

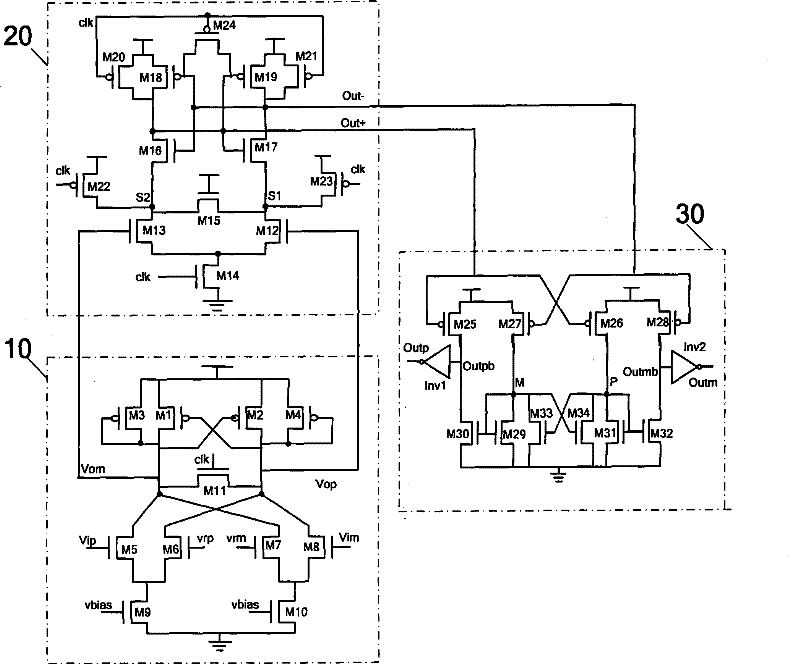

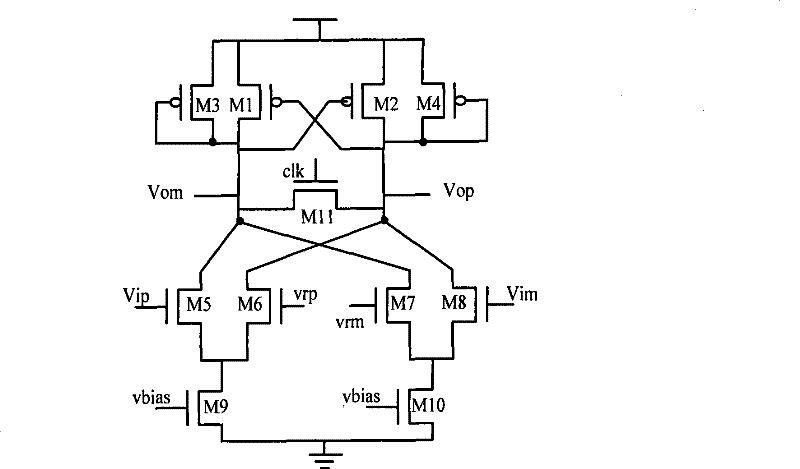

Dynamic comparator

ActiveCN102647189ALower Input Offset VoltageMeet the needs of the designAnalogue/digital conversionElectric signal transmission systemsEngineeringComparator

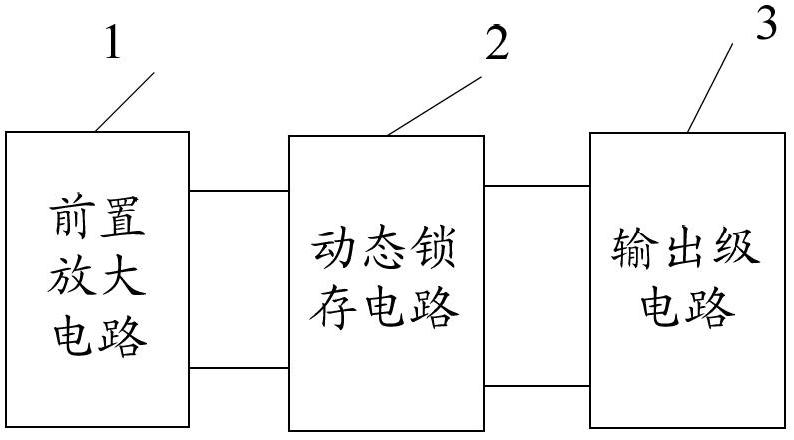

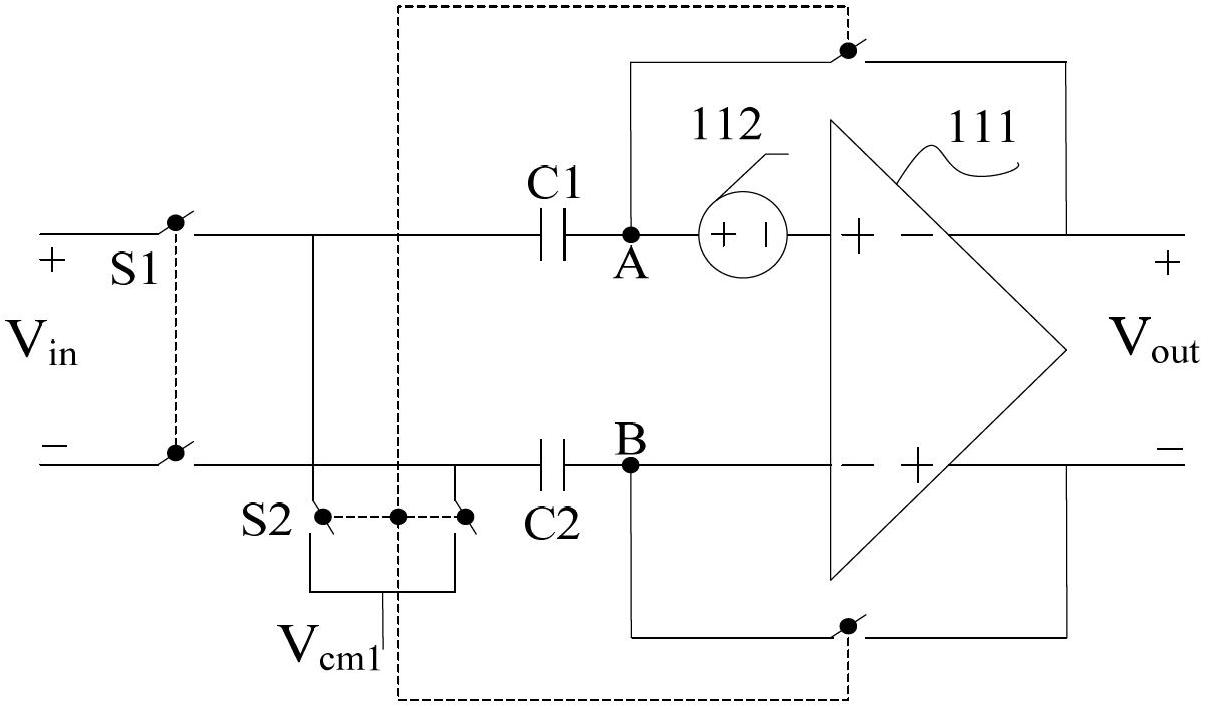

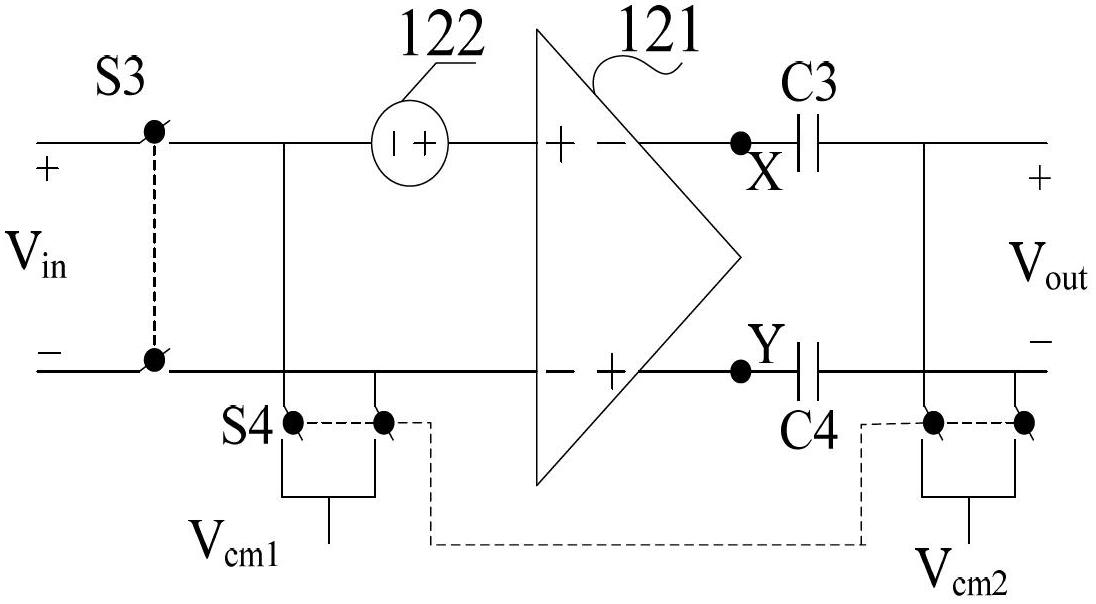

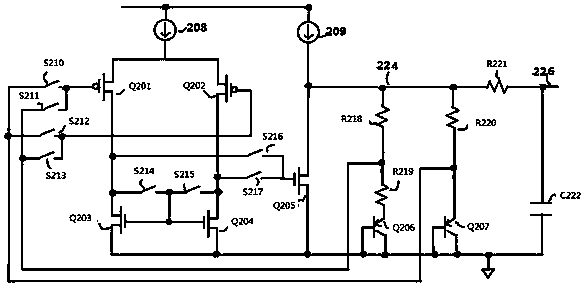

The invention provides a dynamic comparator. The dynamic comparator comprises a pre-amplification circuit, a dynamic latch circuit and an output-stage circuit which are connected in sequence, wherein the pre-amplification circuit comprises a first-stage amplification unit adopting an input detuning storage technology and a second-stage amplification unit adopting an output detuning storage technology; the dynamic latch circuit is used for amplifying the output signal of the pre-amplification circuit, and transforming the amplified signal into a digital logical output level; the output-stage circuit is used for outputting the digital logical output level at a latched phase, and outputting logic zero at a rest phase. The dynamic comparator provided by the invention adopts a detuning canceling technology and a structure isolating kickback noise in the pre-amplification circuit, thus effectively reducing the input detuning voltage, and greatly meeting the demands for design of high speed and high precision analog-digital convertors.

Owner:昆山启达微电子有限公司

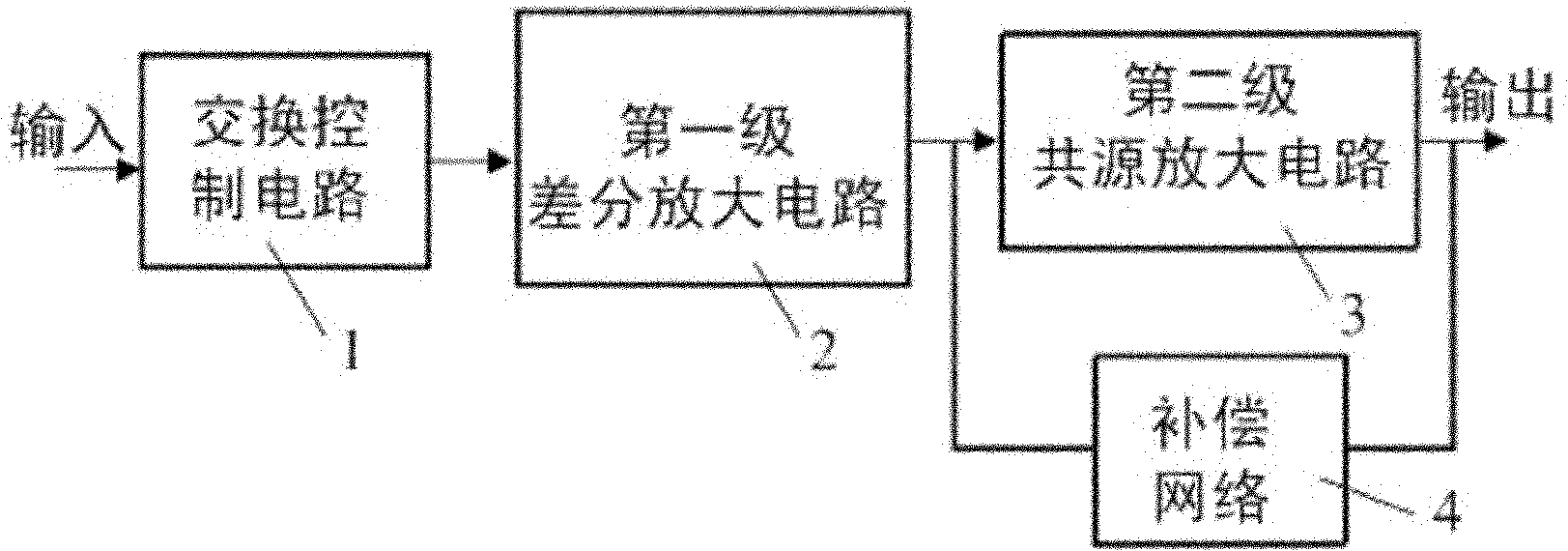

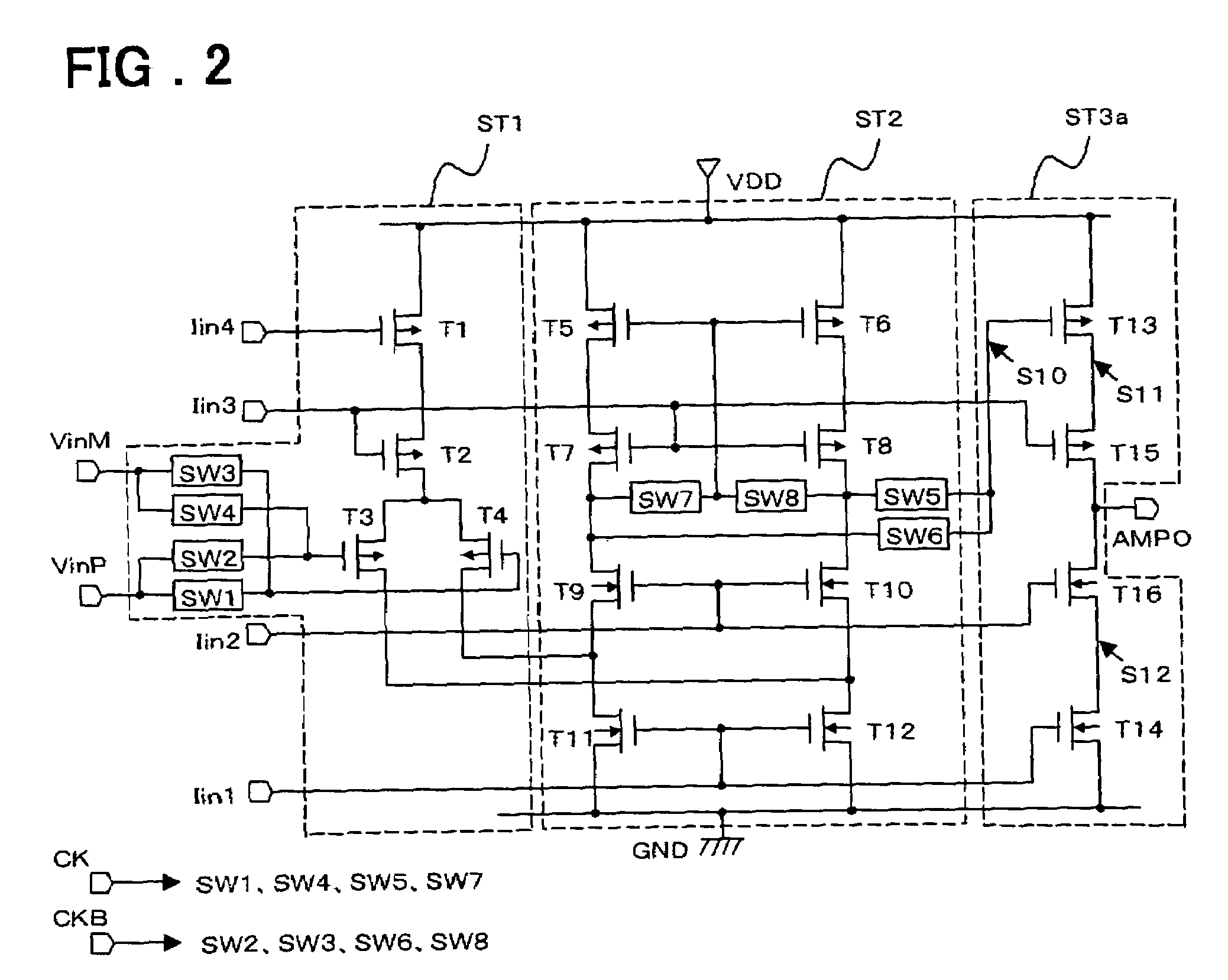

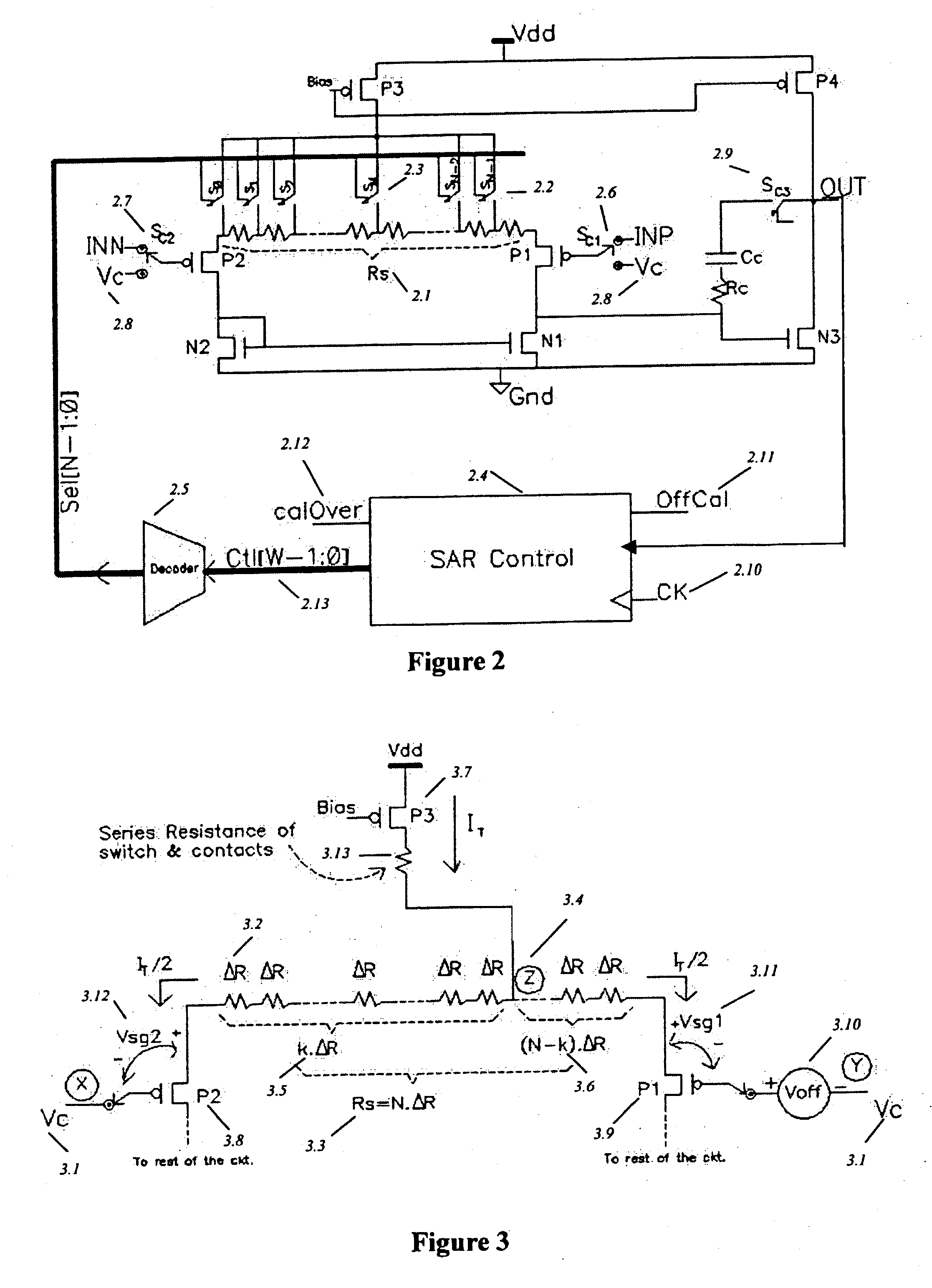

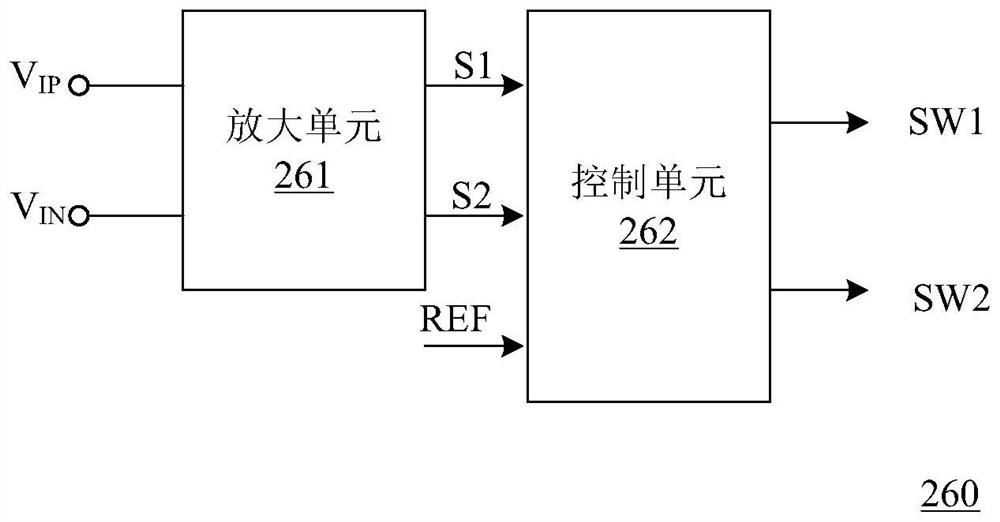

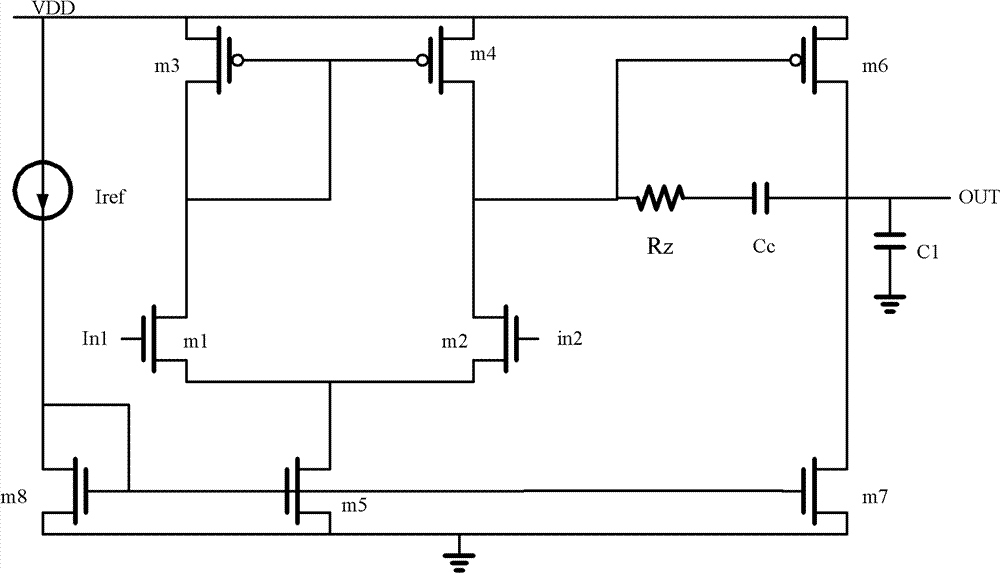

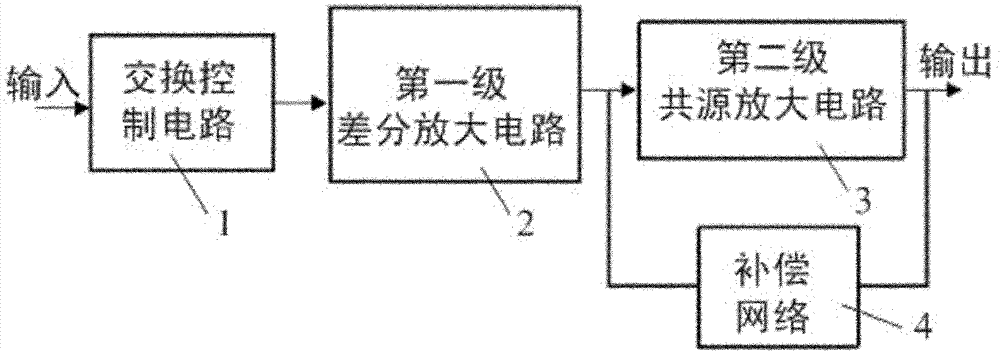

Circuit structure for reducing input offset voltage of two-stage operational amplifier

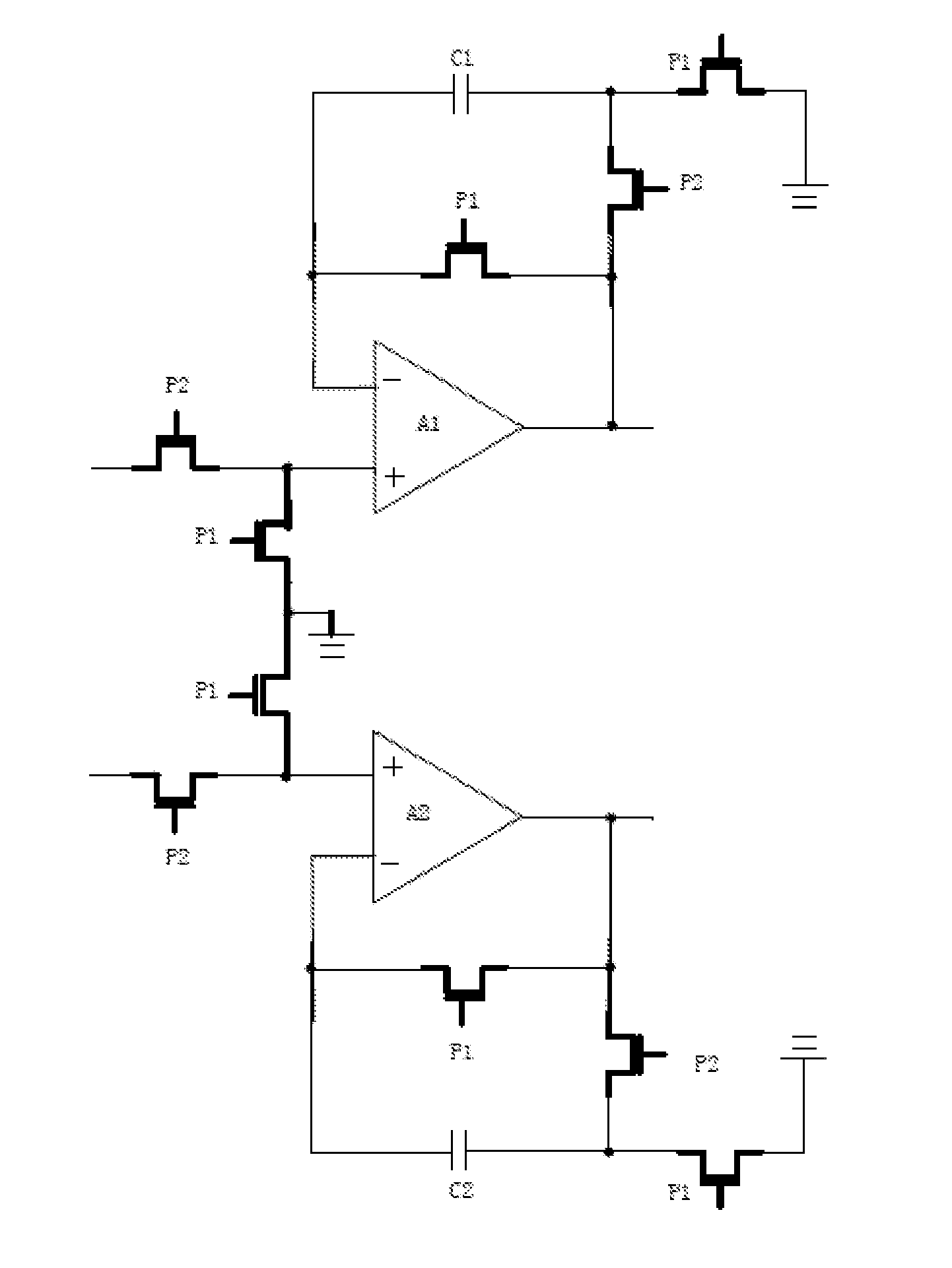

ActiveCN102130659ALower Input Offset VoltageLower Offset VoltageDifferential amplifiersDc-amplifiers with dc-coupled stagesCMOSAudio power amplifier

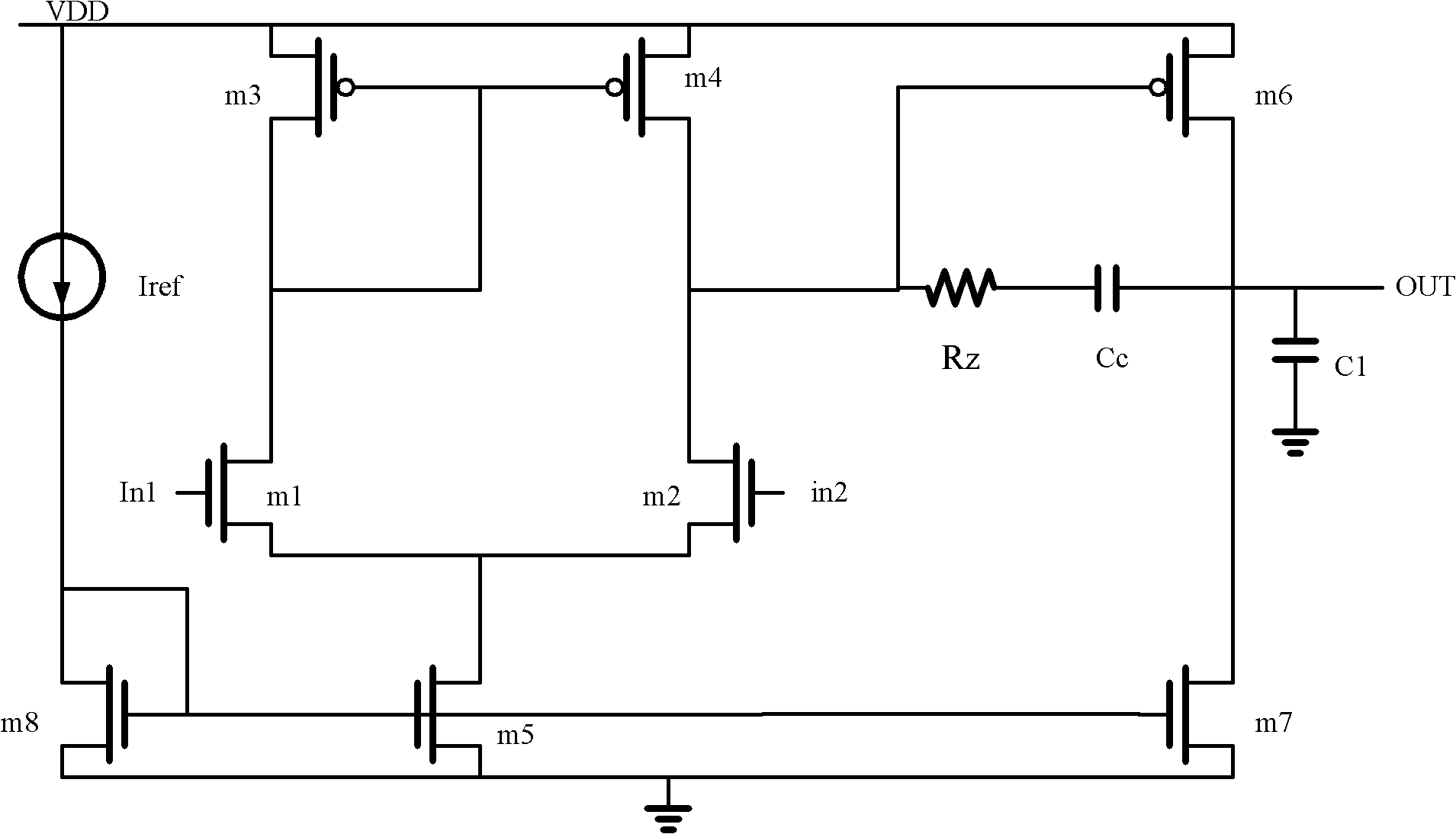

The invention provides a circuit structure for reducing input offset voltage of a two-stage operational amplifier, which comprises a switching control circuit, a first-stage differential amplification circuit, a second-stage common-source amplification circuit and a compensation network, wherein the output end of the switching control circuit is connected with the input end of the first-stage differential amplification circuit, the output end of the first-stage differential amplification circuit is connected with the input end of the second-stage common-source amplification circuit, and the compensation network is further connected between the input end and the output end of the second-stage common-source amplification circuit. The circuit structure has the benefits that the offset of theoperational amplifier is reduced by adopting an MOS (metal oxide semiconductor) switching tube to control and exchange signals at the positive and the negative input ends and the signals at the output end of the operational amplifier; as only the MOS switching tube is increased in the circuit, the circuit structure only needs very small area and very low power consumption; and the circuit does not affect the gain of the operational amplifier, the phase margin, the power supply voltage rejection ratio, the common-mode input range and other performance indexes while reducing the input offset voltage of the operational amplifier, and can be applied in mainstream CMOS (complementary metal oxide semiconductor) circuit systems.

Owner:XIAN JIEHANG ELECTRONICS SCI & TECH CO LTD

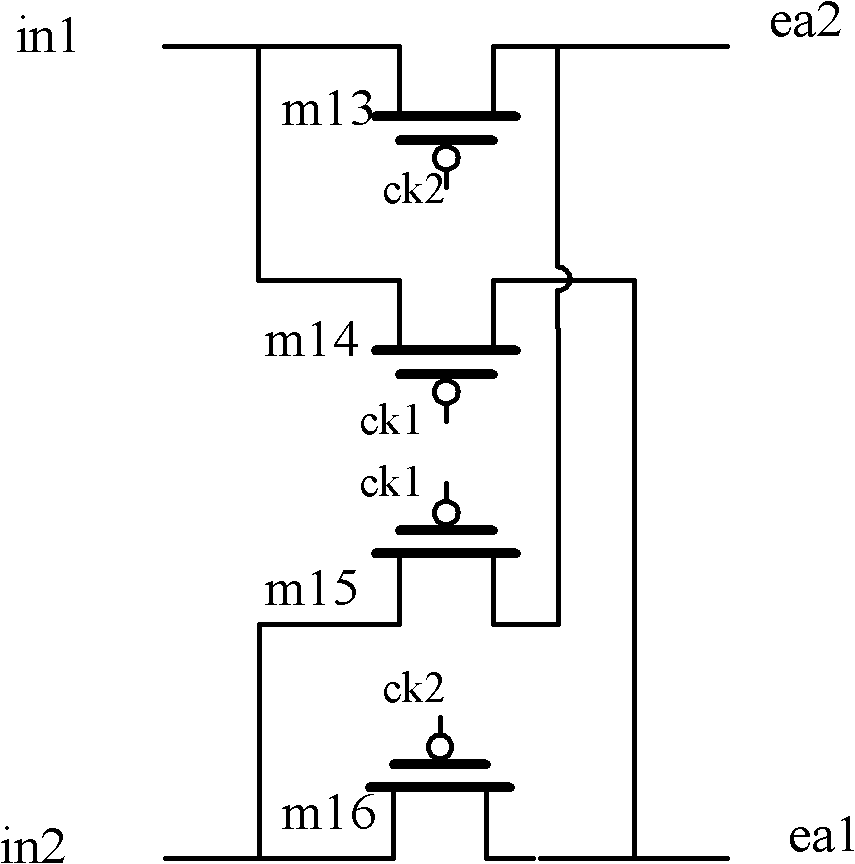

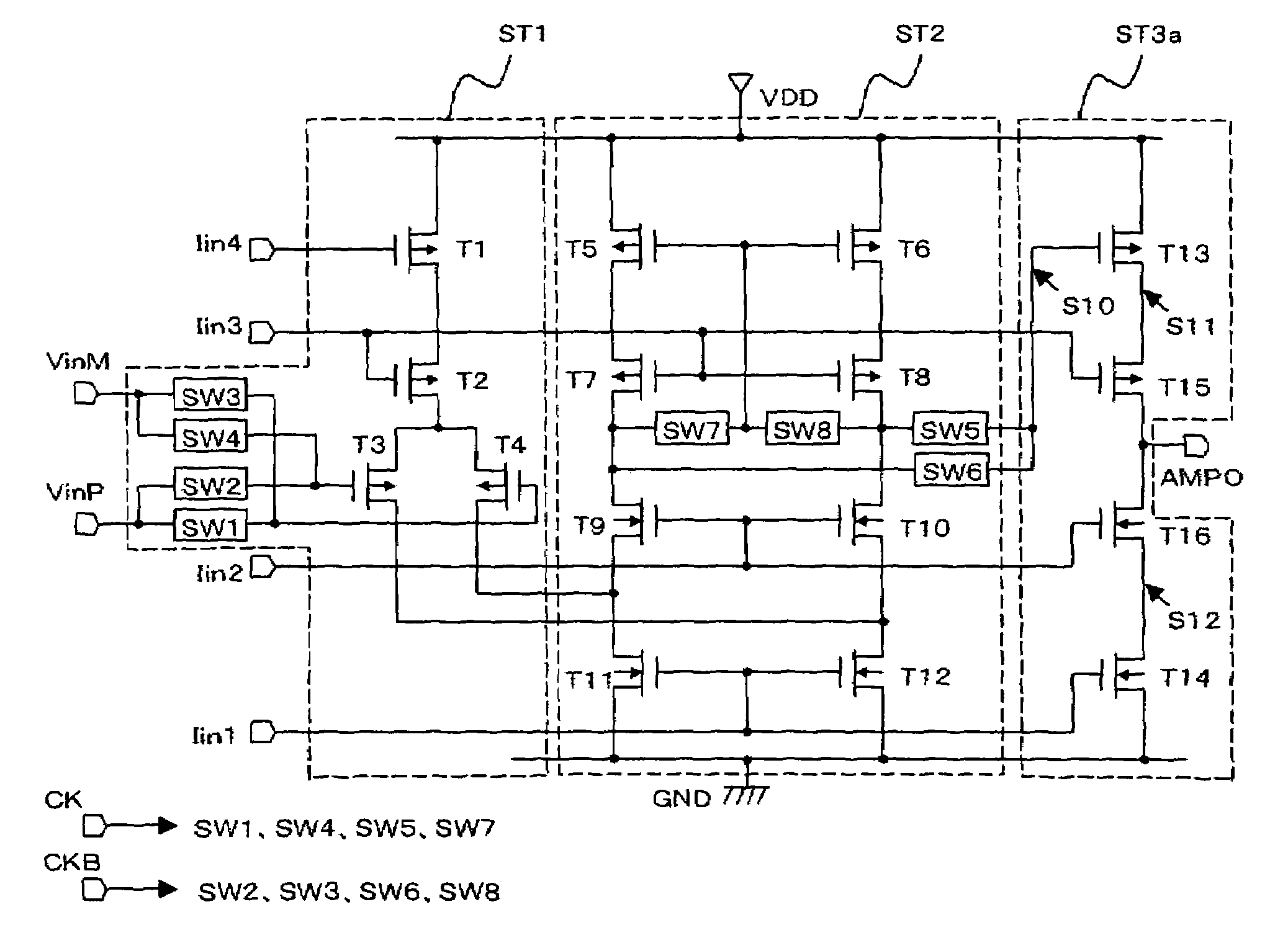

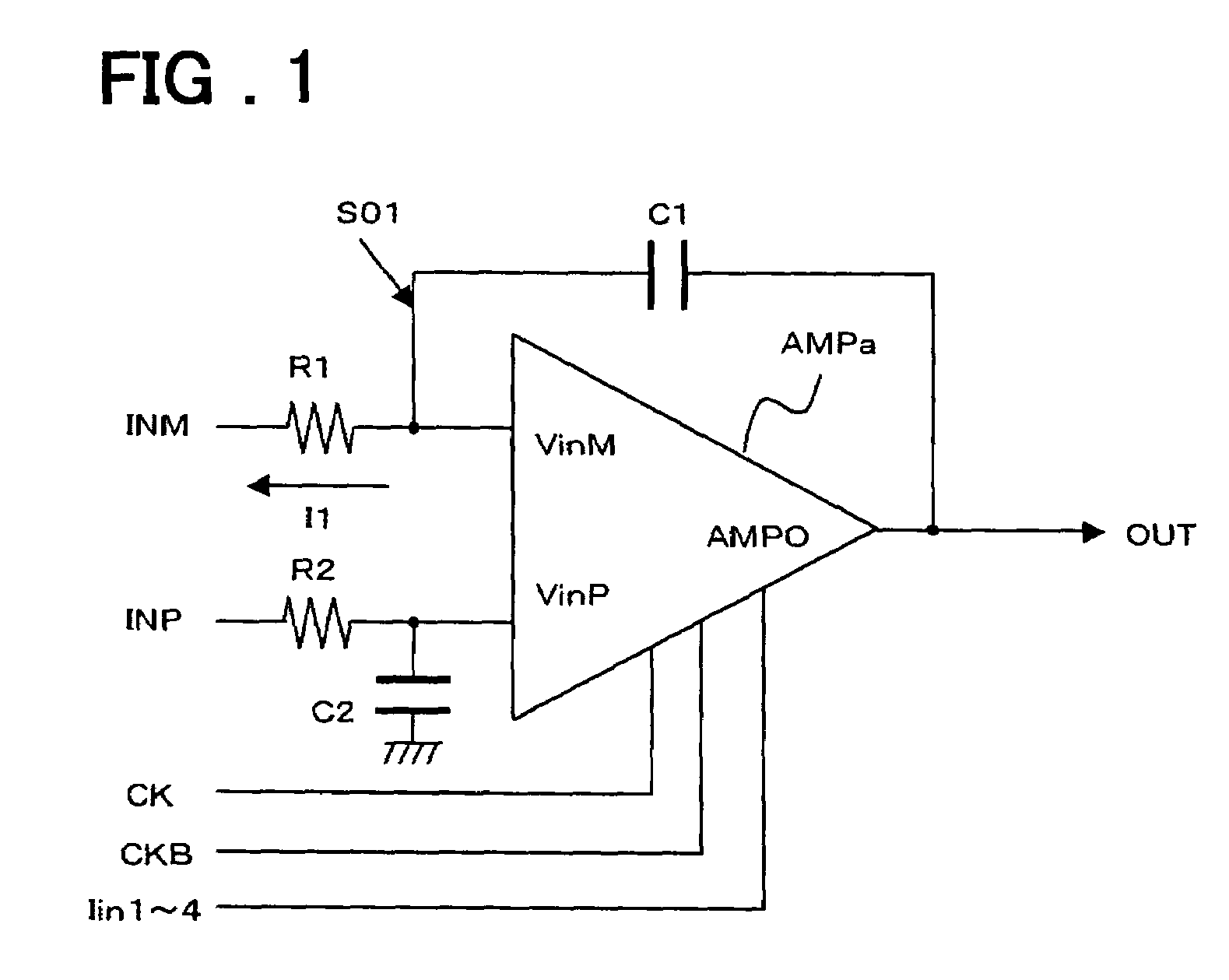

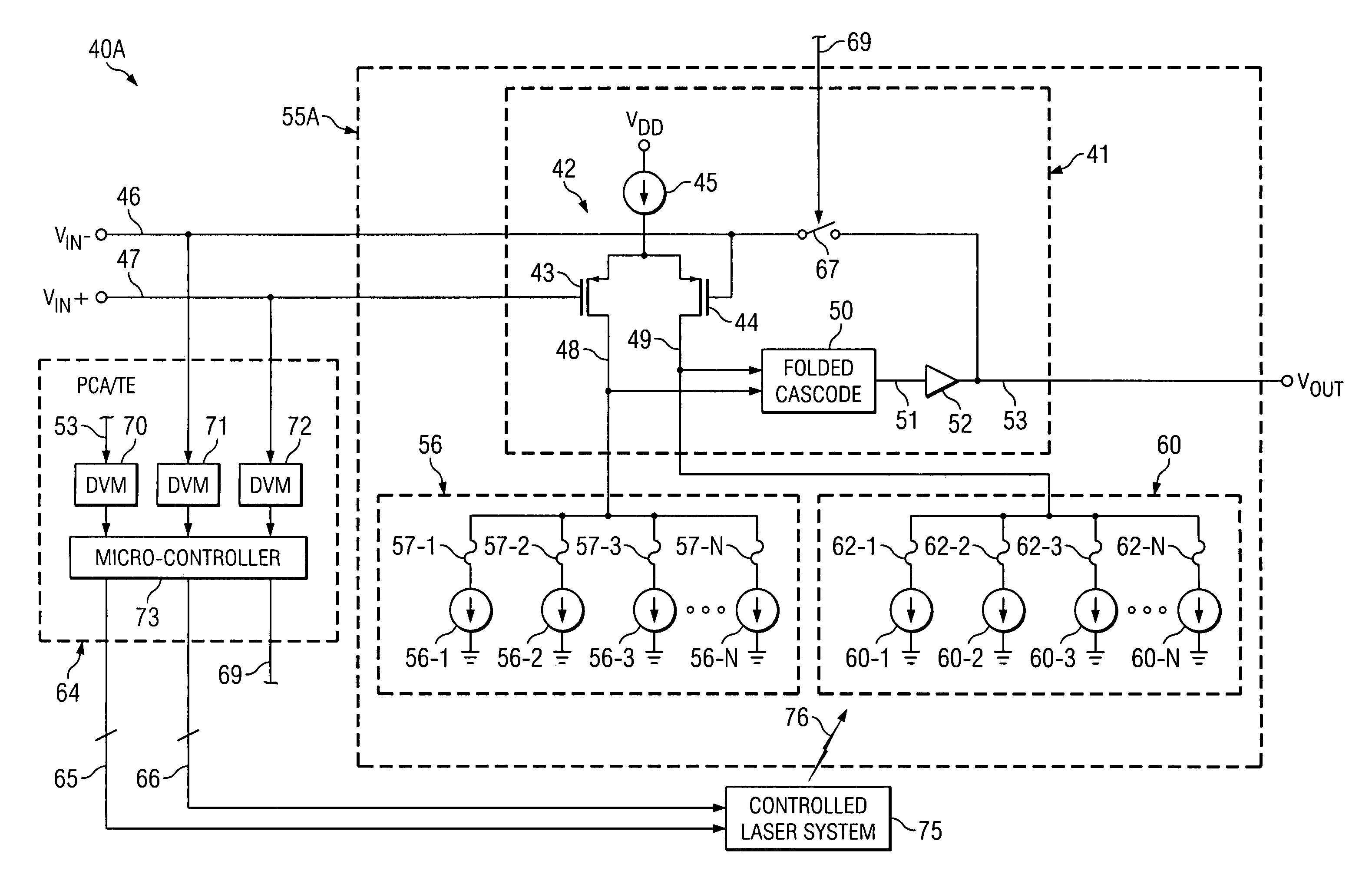

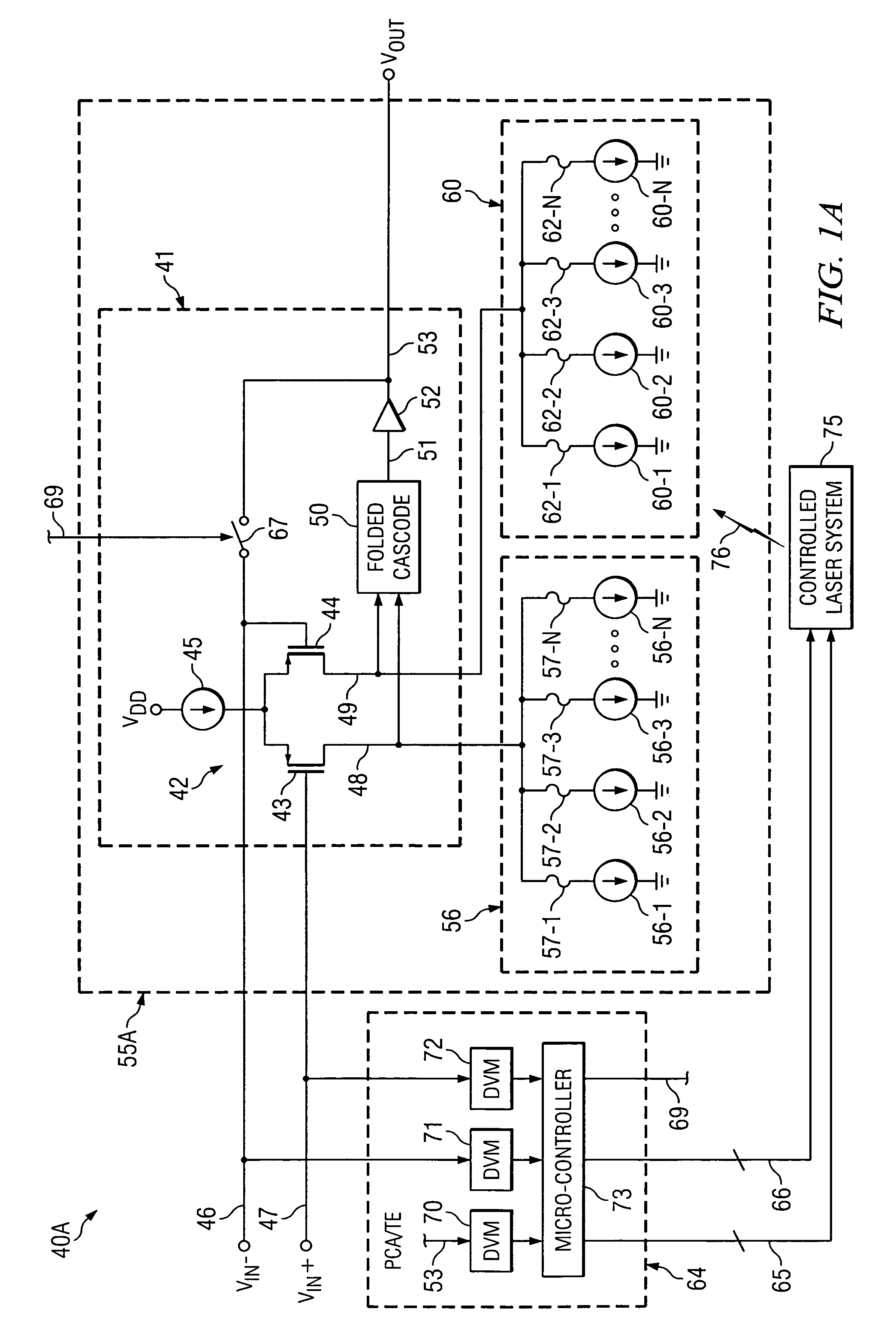

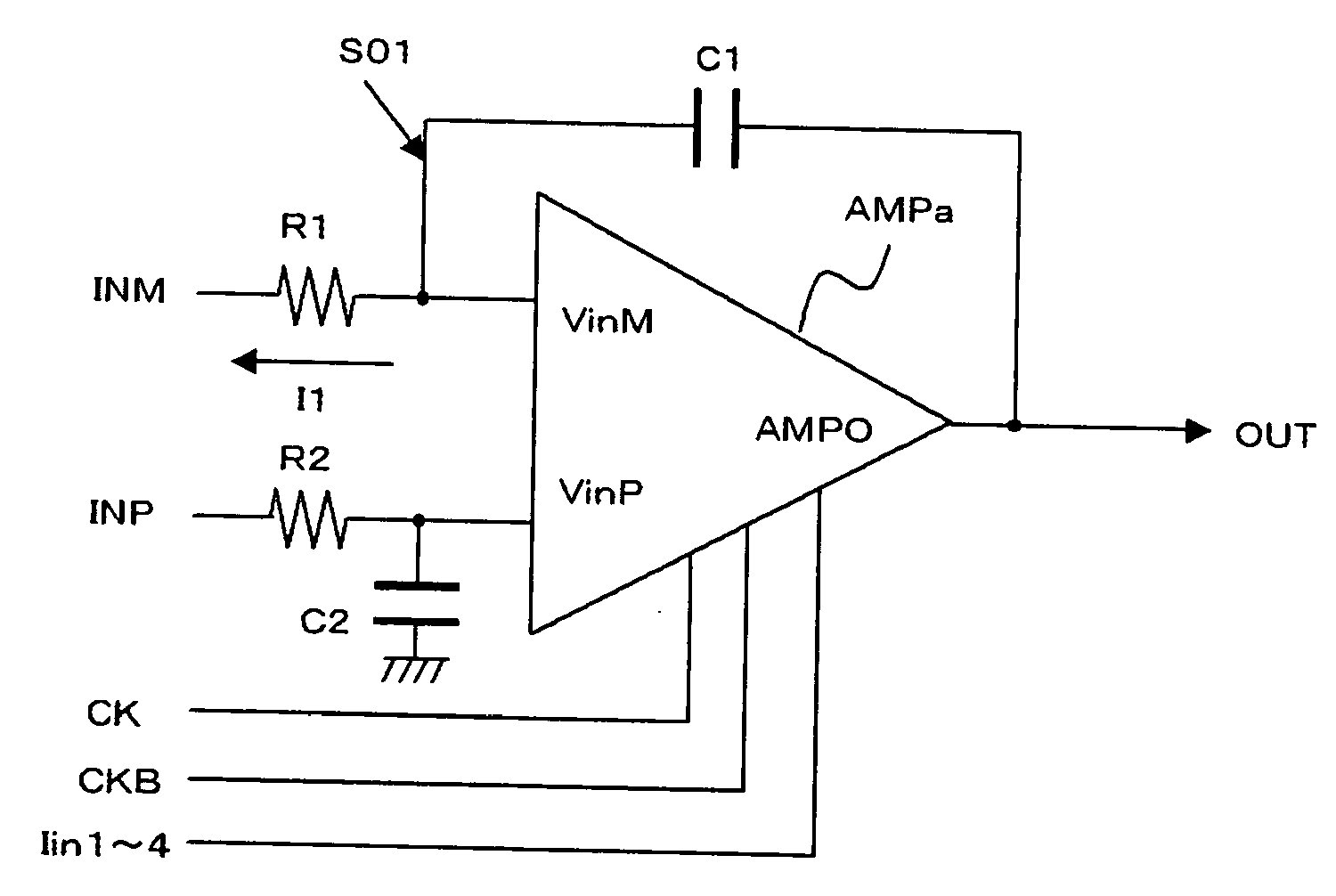

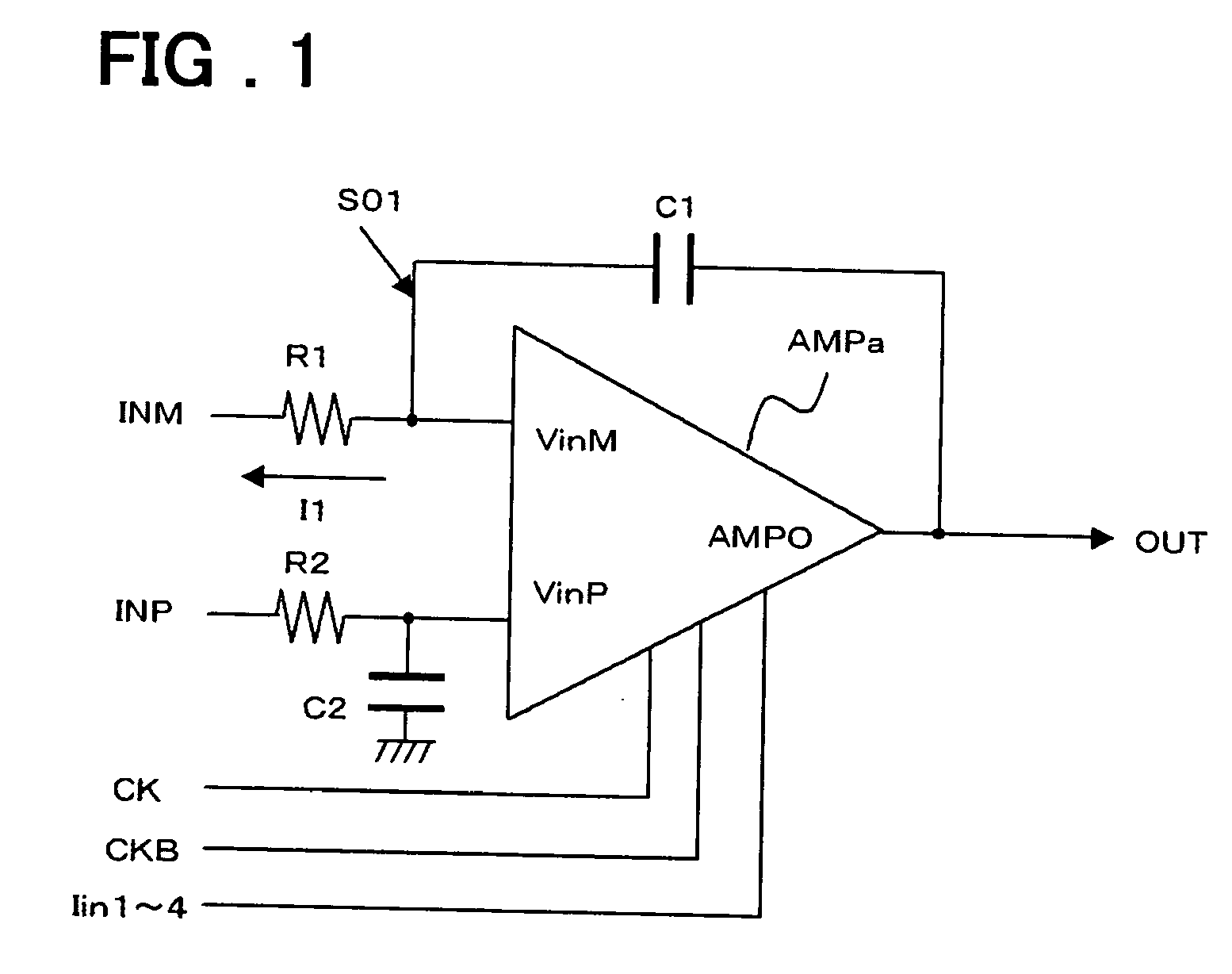

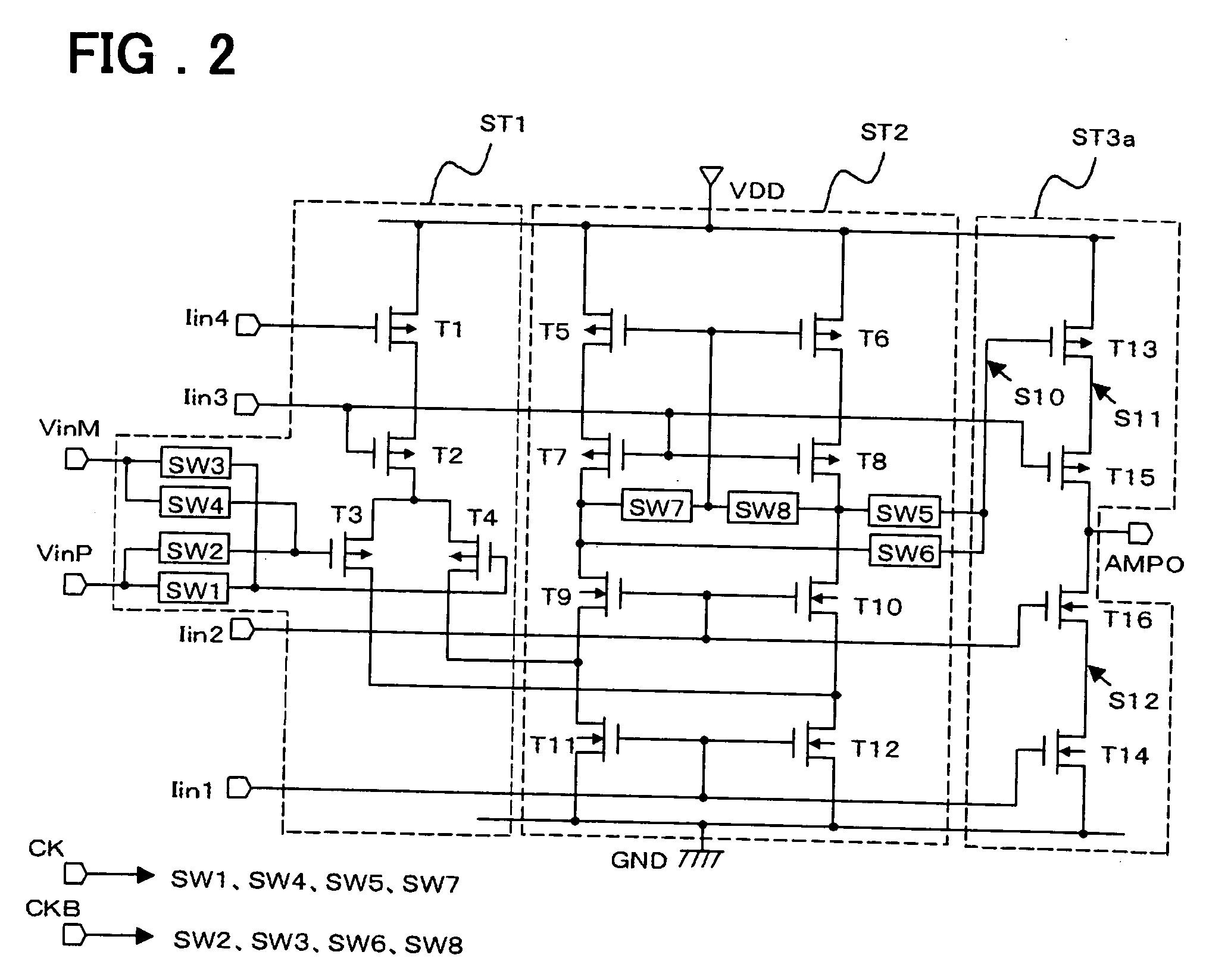

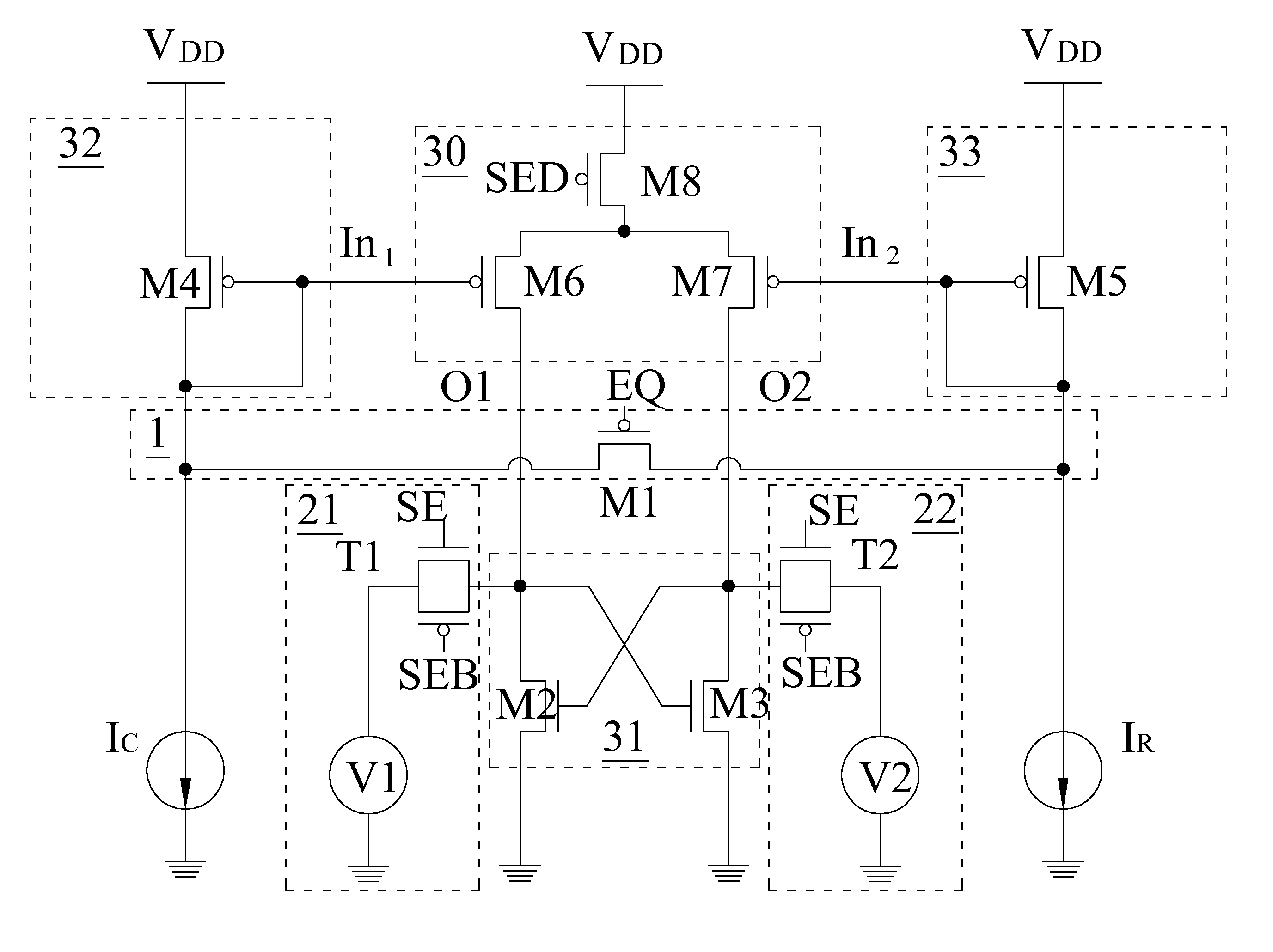

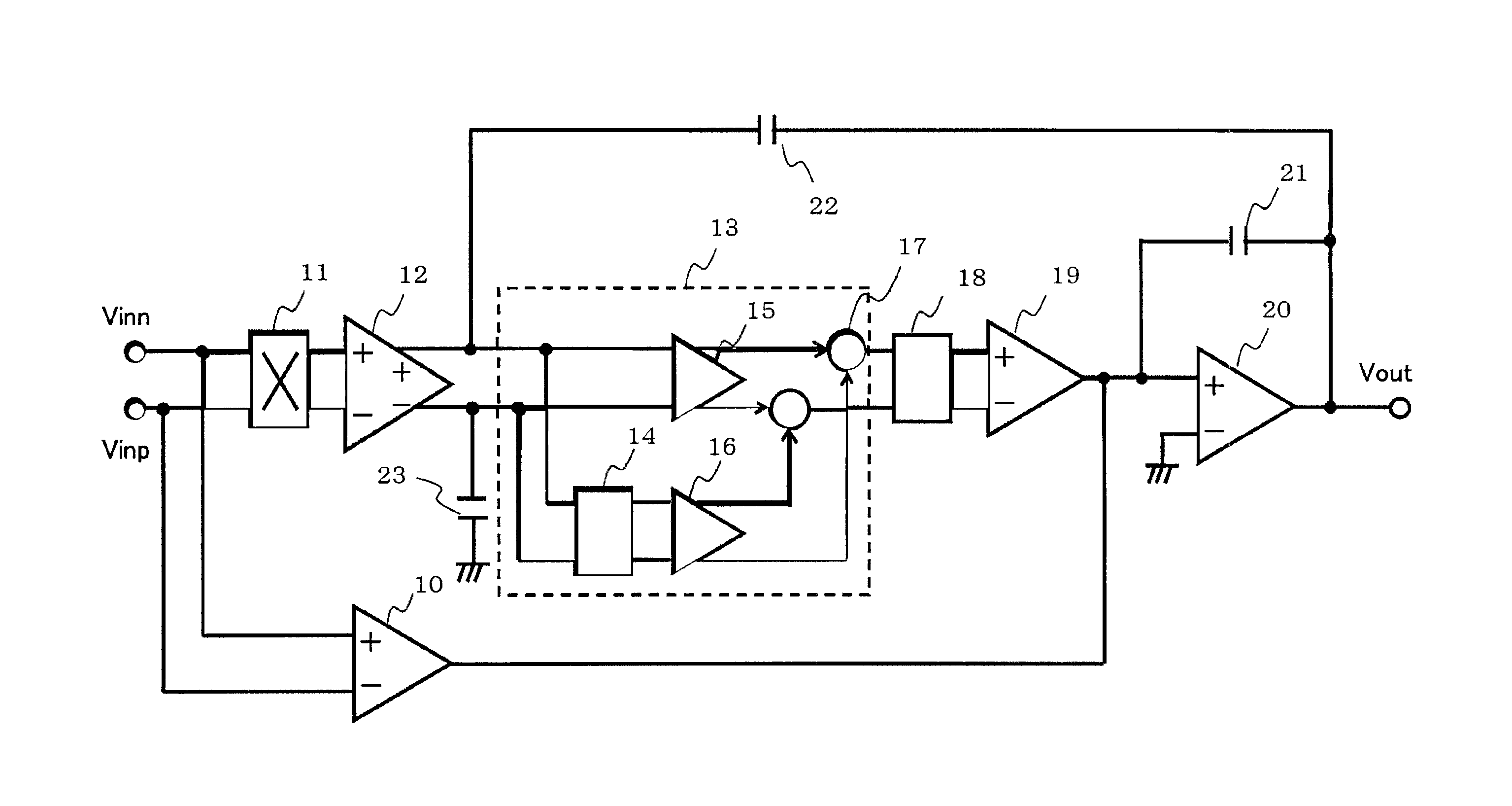

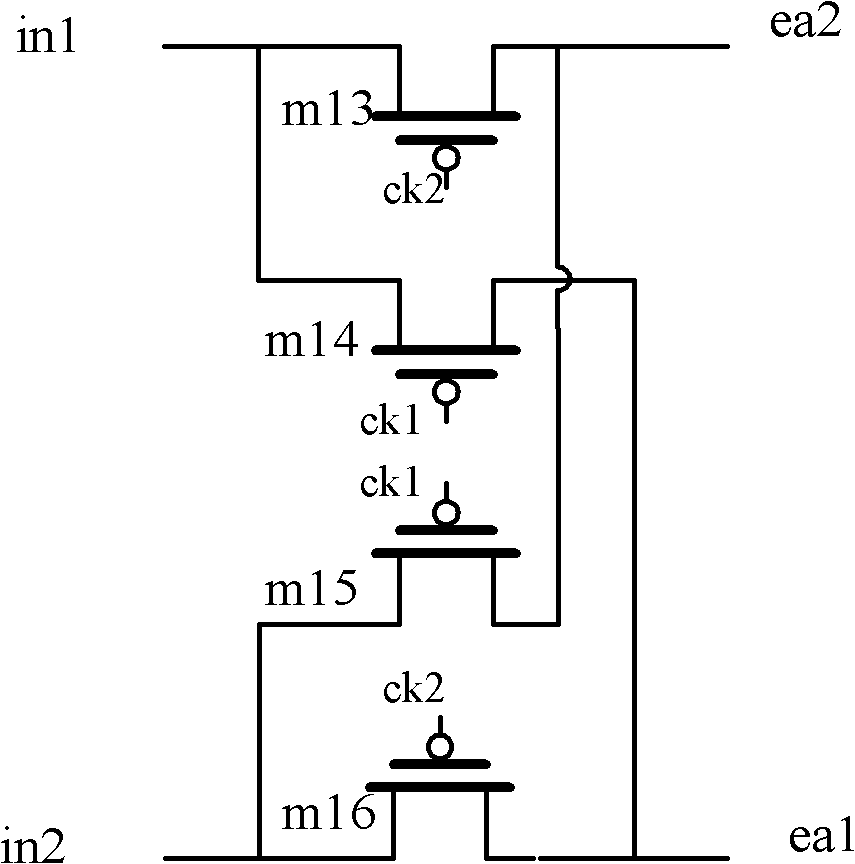

Differential amplifier circuit and semiconductor device

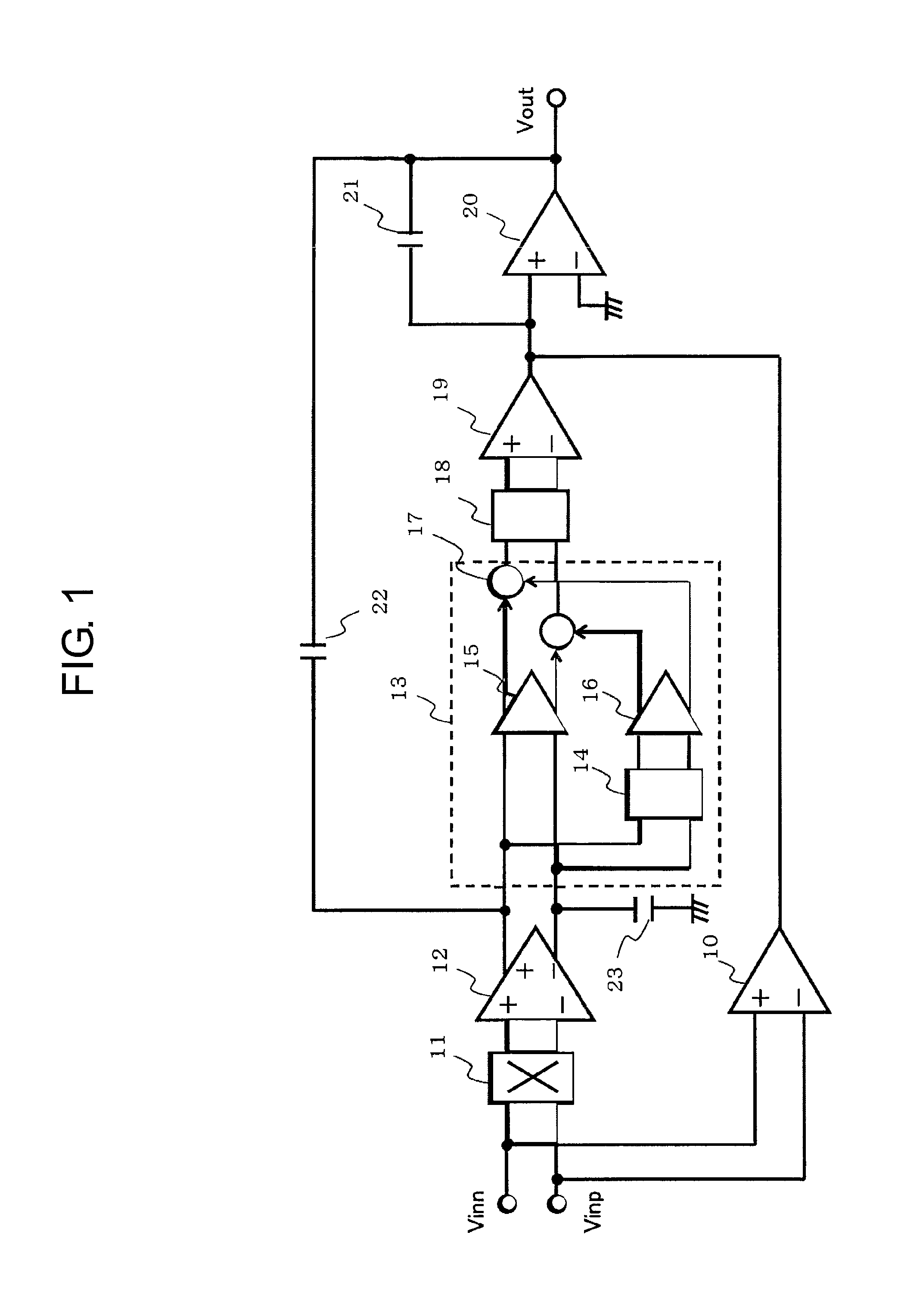

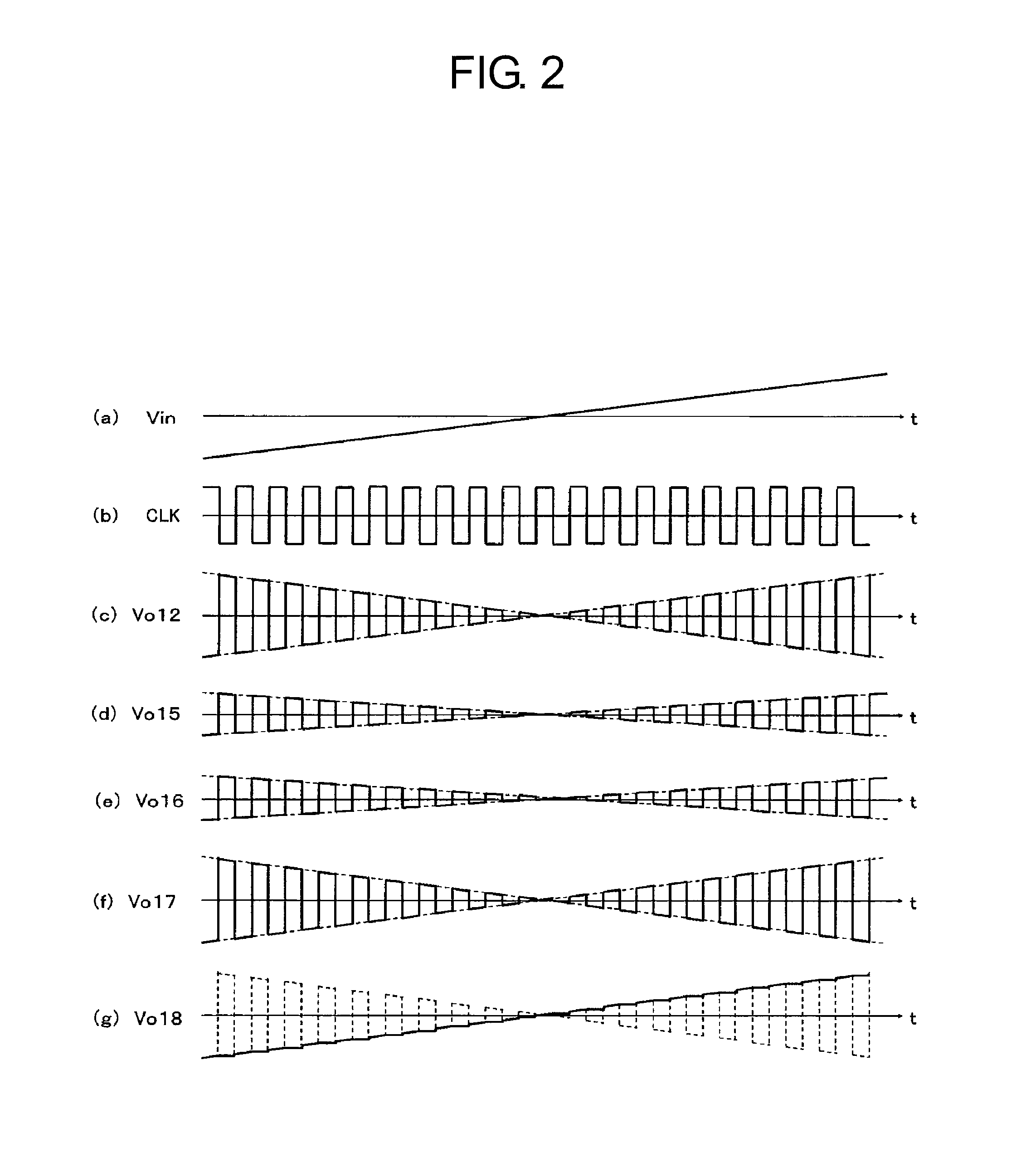

InactiveUS7504882B2High gainLower Input Offset VoltageAmplifier modifications to raise efficiencyDigital storageAudio power amplifierSignal on

A differential amplifier circuit in which an input offset voltage is very small. The differential amplifier circuit includes an input-stage differential amplifier section and a cascode-connected single-ended output section connected to the input-stage differential amplifier section. The input-stage differential amplifier section has a folded-cascode-connection. An inverted signal and non-inverted signal on the input side and output side, respectively, of the input-stage differential amplifier section are switched alternatingly in time-shared fashion by switches that are operated by two chopping clock signals of opposite phase.

Owner:RENESAS ELECTRONICS CORP

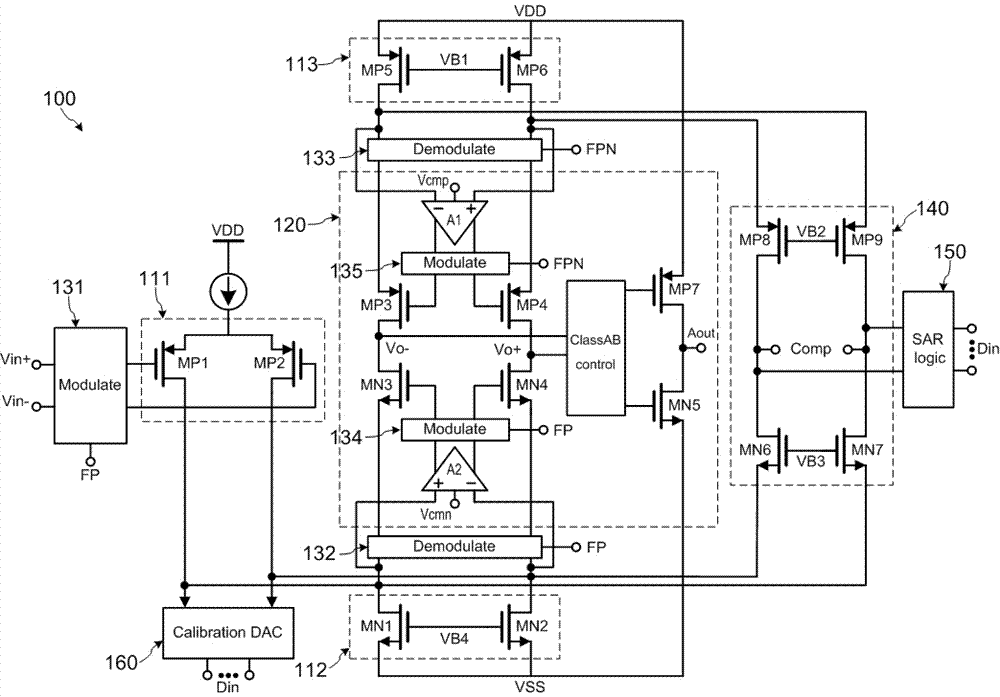

Digital self-calibration chopper precision amplifier and implementation method

PendingCN107241067ALower Input Offset VoltageSmall output rippleAmplifier modifications to reduce noise influenceAmplifier modifications to reduce temperature/voltage variationDigital analog converterSoftware engineering

The invention provides a high-performance digital self-calibration chopper precision amplifier which is low in cost and easy to implement and an implementation method. The amplifier mainly comprises a digital self-calibration loop and a chopper circuit. After the amplifier is energized, the amplifier is configured as a digital self-calibration state within a period of time, and the chopper circuit and an amplifier output circuit are switched off. The calibrated digital quantity is stored in a register, and input offset voltage of the amplifier is calibrated through a digital analog converter. After the digital self-calibration state is finished, a comparison output circuit is switched off, the amplifier is configured as a chopper magnifying state, and the chopper circuit and the amplifier output circuit work, so that the input offset voltage of the amplifier, temperature drift of the offset voltage and flicker noise are lowered.

Owner:LINEARIN TECH CORP

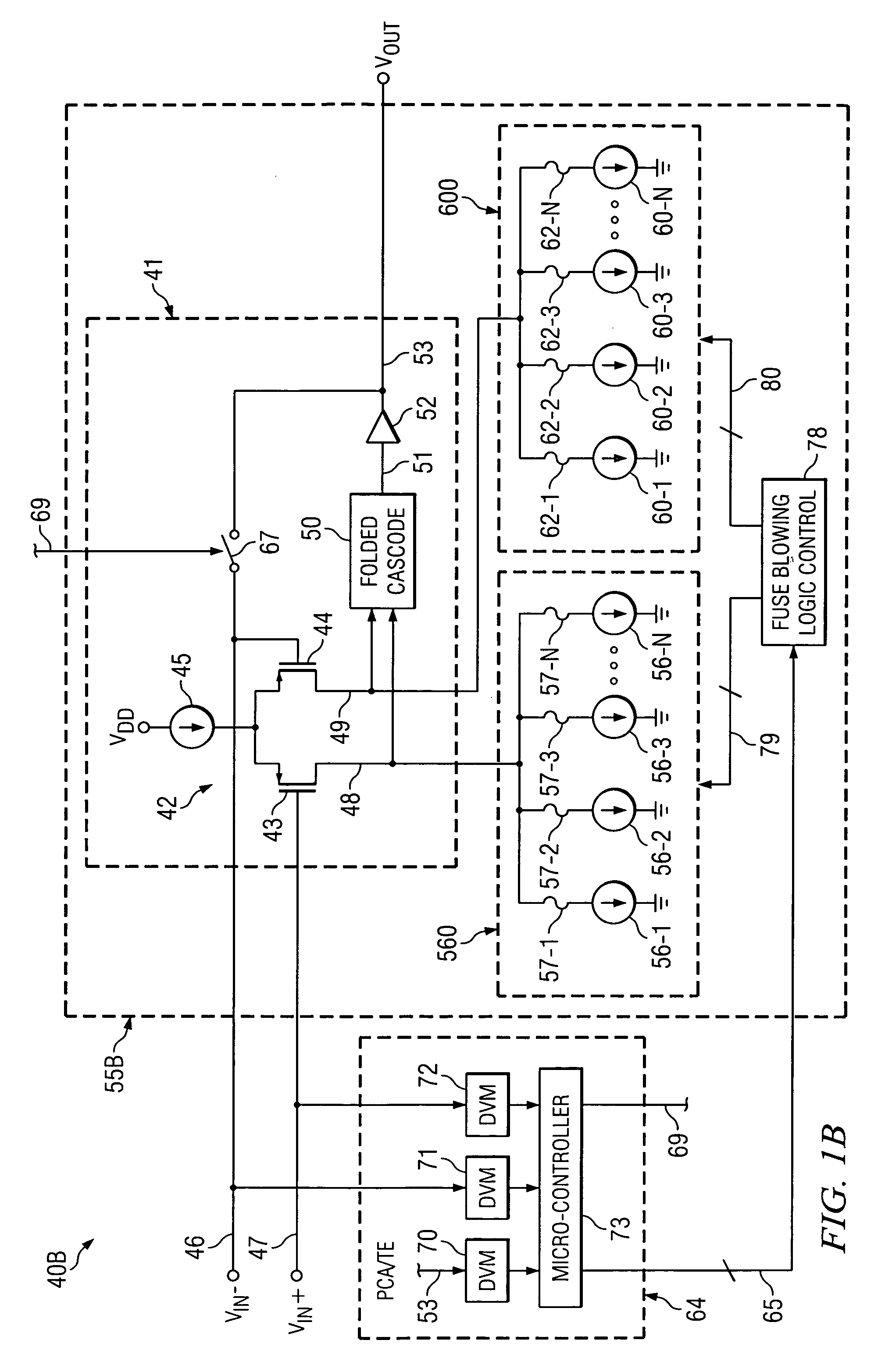

Fuse link trim algorithm for minimum residual

ActiveUS7049986B1Lower Input Offset VoltageReduce noiseElectric signal transmission systemsRead-only memoriesBit numberingIntegrated circuit

A parameter of an integrated circuit including a first trim array and a second trim array is trimmed by measuring an initial value of the parameter, determining whether the parameter exceeds a reference value, and as long as the parameter exceeds the reference value, repetitively blowing fuses associated with binarily weighted trim elements of the first trim array to eliminate trim contributions thereof to thereby decrease the parameter by weighted amounts corresponding to a present trim array bit number value until either all fuses of the first trim array have been blown or enough have been blown to cause the parameter to be less than a −LSB / 2 weight. If the parameter then is less than the −LSB / 2 weight, a fuse of the second trim array corresponding to a present bit number is blown to increase the parameter to greater than a +LSB / 2 weight. The procedure is repeated until all fuses in one trim array have been blown, to thereby minimize the number of residual trim elements.

Owner:TEXAS INSTR INC

Differential amplifier circuit and semiconductor device

InactiveUS20070058438A1Good effectNarrow downAmplifier modifications to raise efficiencyRead-only memoriesAudio power amplifierSignal on

A differential amplifier circuit in which an input offset voltage is very small. The differential amplifier circuit includes an input-stage differential amplifier section and a cascode-connected single-ended output section connected to the input-stage differential amplifier section. The input-stage differential amplifier section has a folded-cascode-connection. An inverted signal and non-inverted signal on the input side and output side, respectively, of the input-stage differential amplifier section are switched alternatingly in time-shared fashion by switches that are operated by two chopping clock signals of opposite phase.

Owner:RENESAS ELECTRONICS CORP

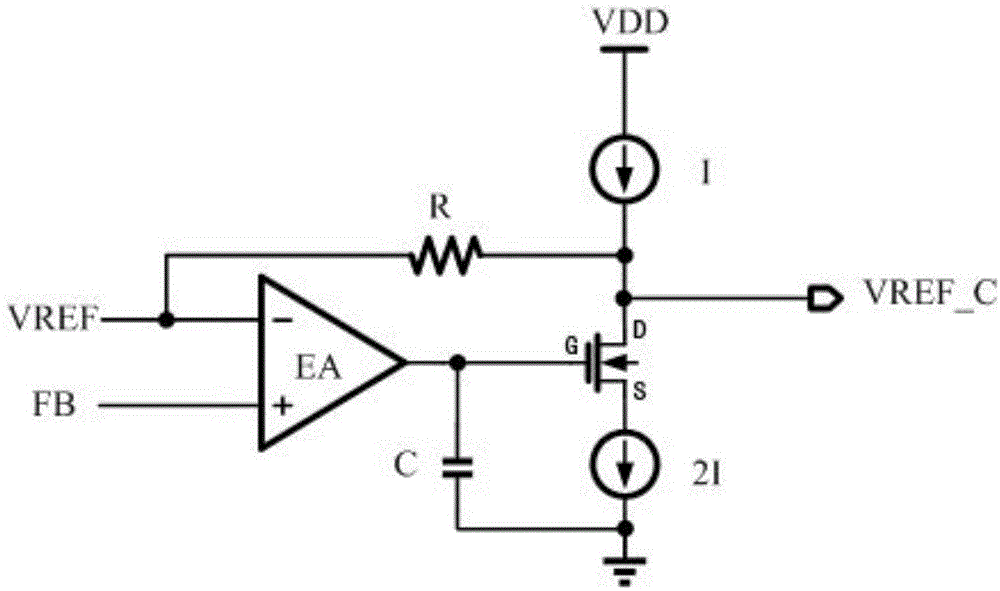

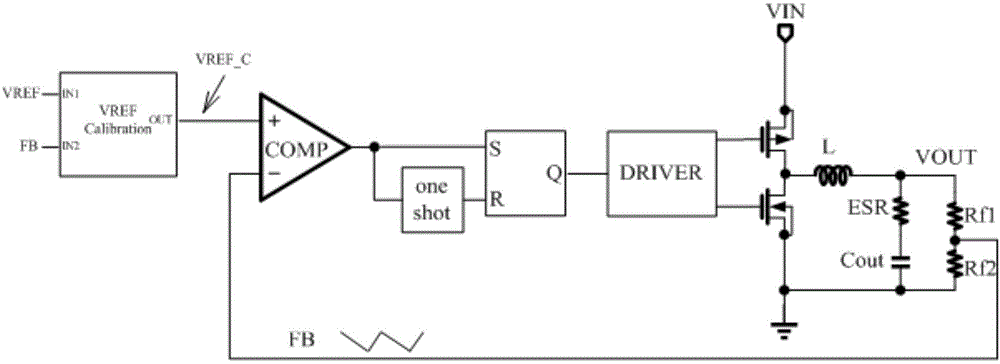

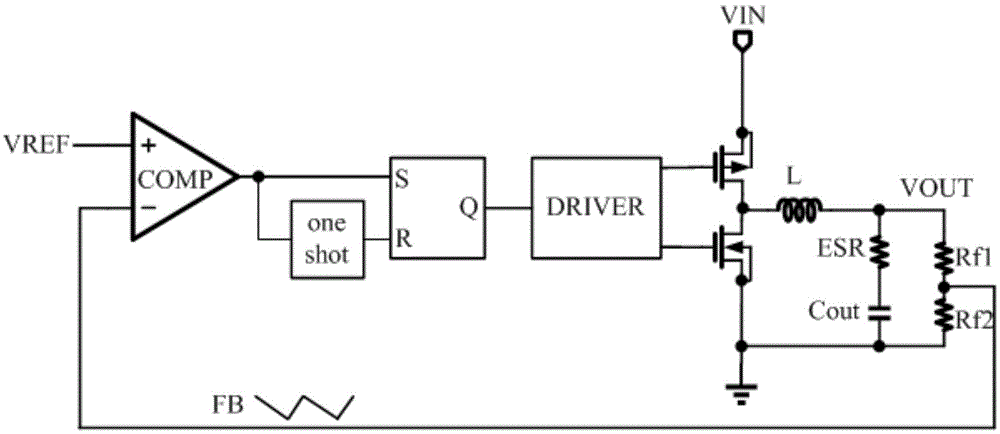

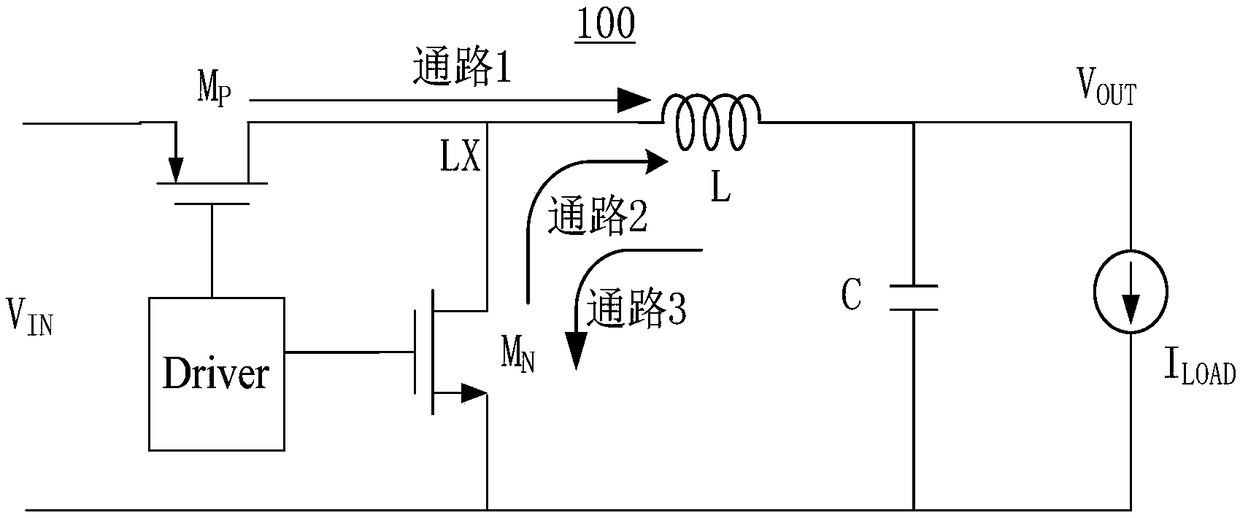

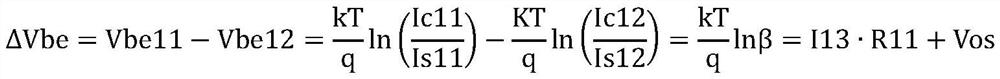

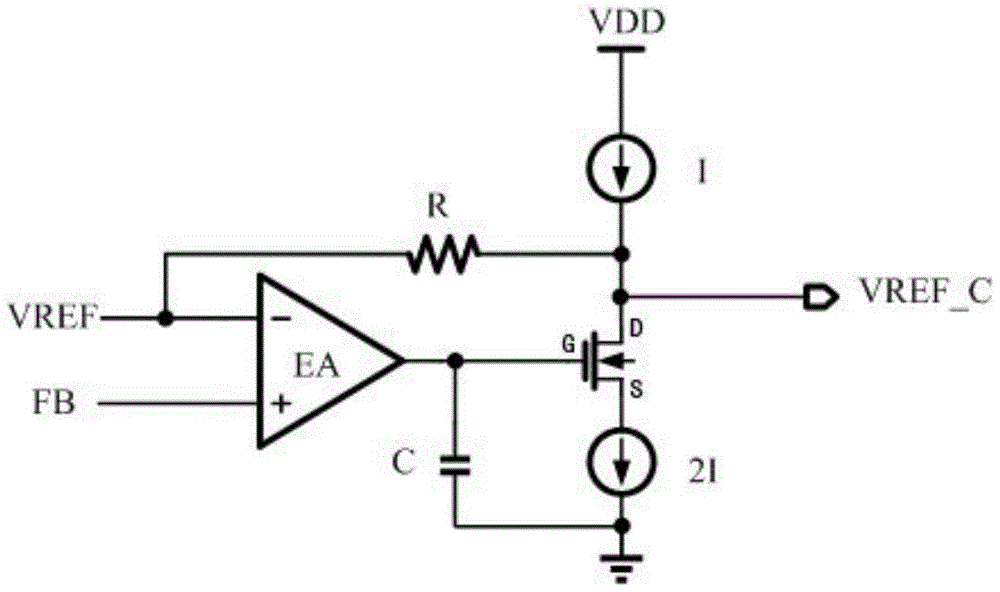

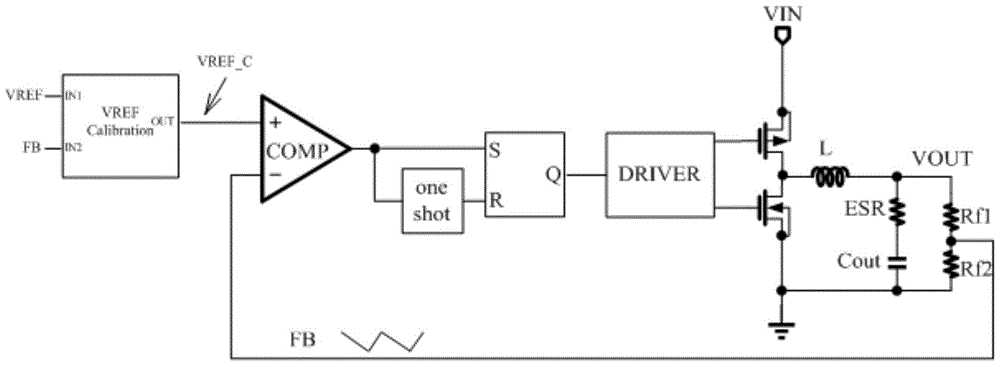

Method and application of reference voltage correcting circuit for controlling buck converter

The invention relates to the technical field of power sources and correcting circuits, in particular to a method and application of a reference voltage correcting circuit for controlling a buck converter. According to the circuit, the output end of a comparator EA is connected with one end of a capacitor C and a grid electrode G of a field-effect tube, a source electrode S of the field-effect tube is connected with a constant current source 2I input signal line, one end of a constant current source 2I output signal line is connected with the other end of the capacitor C, a tapping line of the constant current source 2I output signal line is connected to the ground, a drain electrode D of the field-effect tube is the VREF output voltage point C of a comparator and is connected with one end of a resistor R and one end of a constant current source I output signal line, the other end of a constant current source I input signal line is connected with a power source VDD, the other end of the resistor R is connected with the reverse input end of the comparator EA, a voltage VREF is arranged at the reverse input end of the comparator EA, a voltage FB is arranged at the same-phase input end of the comparator EA, and the circuit output voltage point C is controlled by the voltage VREF and the voltage FB. Compared with the prior art, input offset voltages are small, the output voltage errors caused by a COT structure can be removed, and the output voltage precision is improved.

Owner:南京泰艾微电子有限公司

Non-switched capacitor offset voltage compensation in operational amplifiers

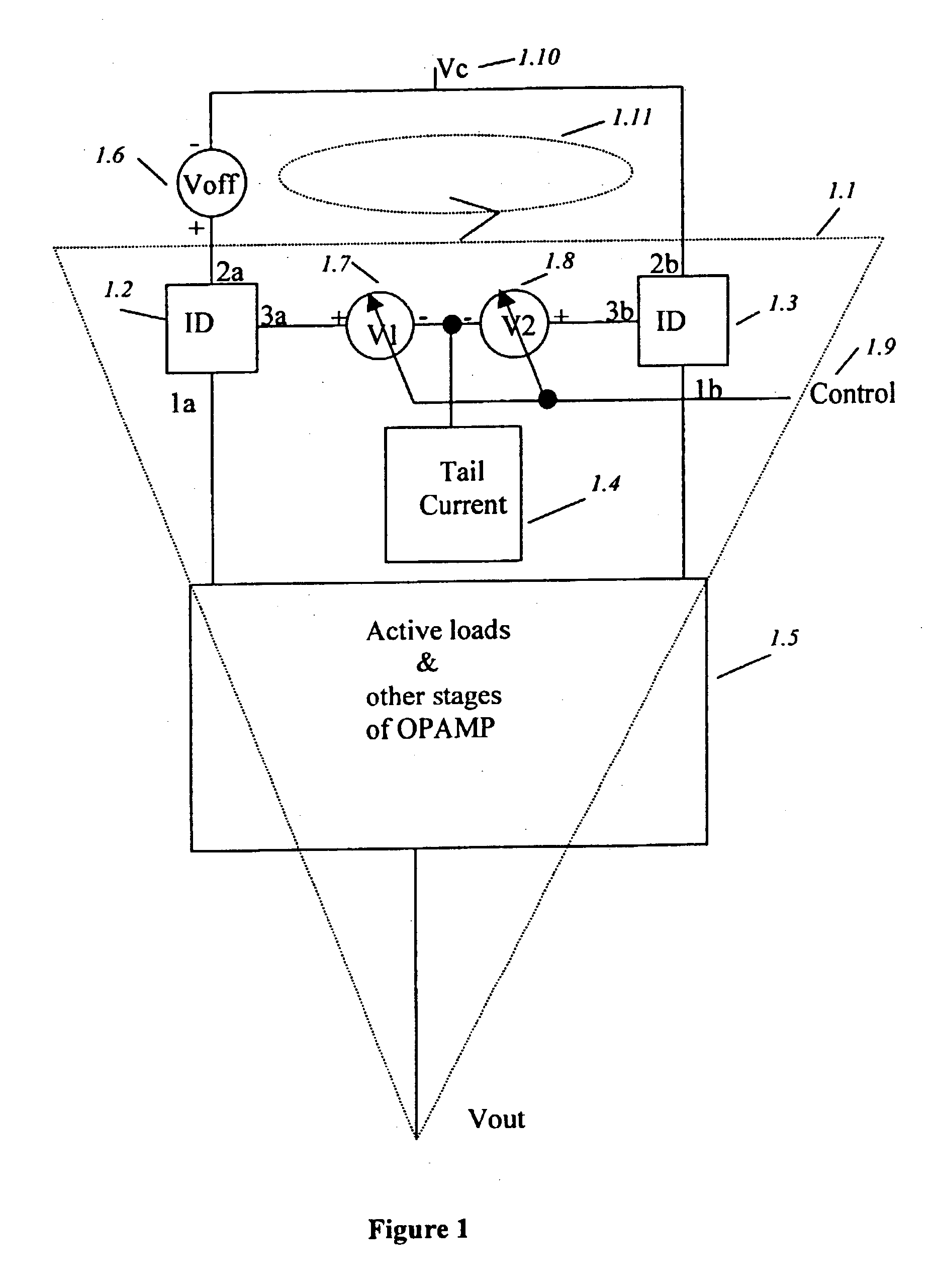

InactiveUS6859095B2Delay minimizationMinimize inaccuracyAmplifier modifications to raise efficiencyElectronic switchingAudio power amplifierDifferential amplifier

A method for reducing offset voltage in an operational amplifier without the need for switched-capacitors, includes introducing a tapped resistor chain between the common connected terminals of the transistors of the input differential pair of the operational amplifier and connecting the tail current source / sink of the differential amplifier to a selected tap of the resistor chain. The invention further provides an improved operational amplifier in accordance with the above method.

Owner:STMICROELECTRONICS PVT LTD

Current-sense amplifier with low-offset adjustment and method of low-offset adjustment thereof

ActiveUS8320211B1Slow memory data read speedReduce detection accuracyCurrent/voltage measurementRead-only memoriesElectricityAudio power amplifier

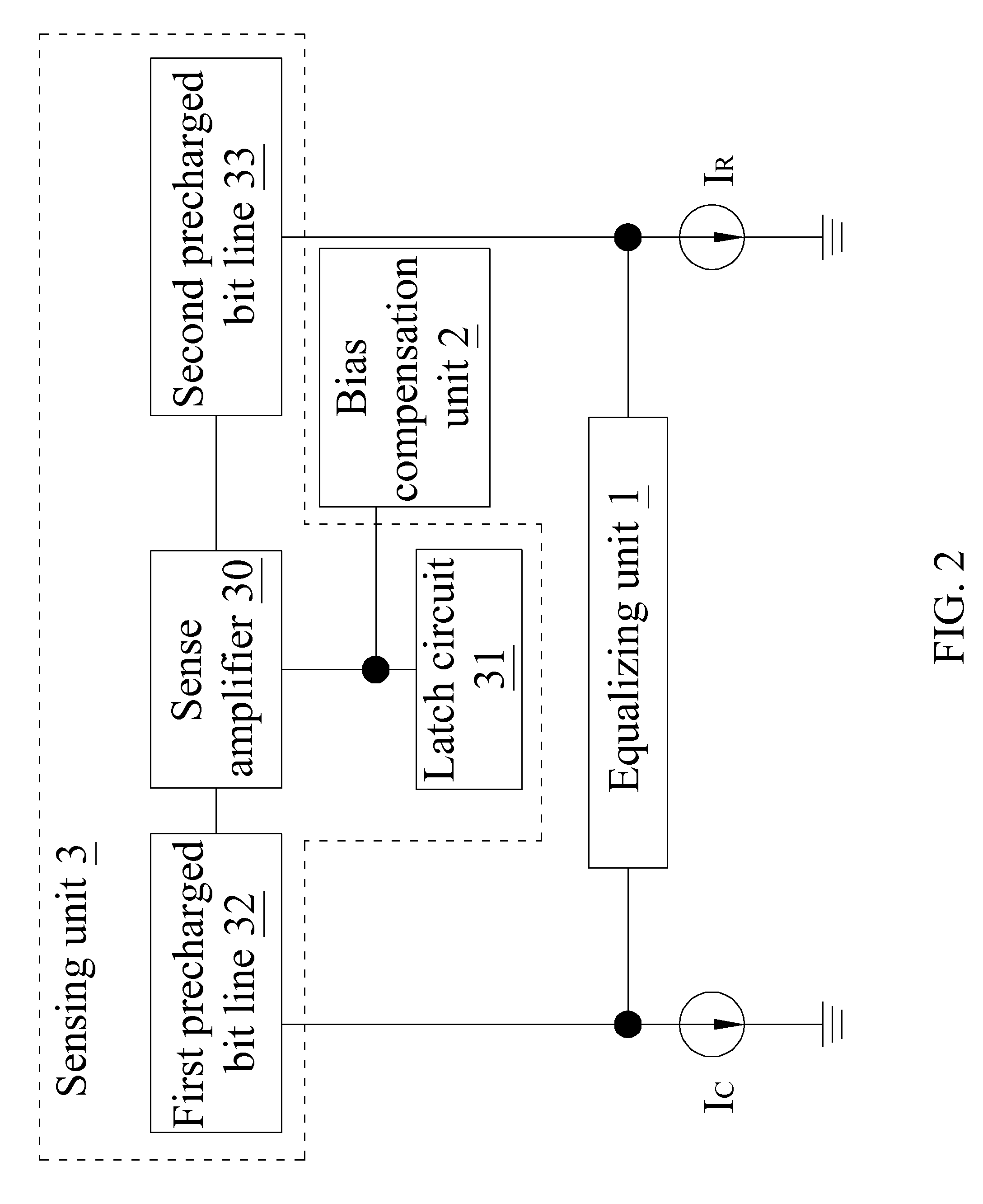

A current-sense amplifier with low-offset adjustment and a low-offset adjustment method thereof are disclosed. The current-sense amplifier includes a sensing unit, an equalizing unit and a bias compensation unit. The sensing unit includes a sense amplifier, a latch circuit, a first precharged bit line, and a second precharged bit line. The equalizing unit is electrically connected to the first and the second precharged bit line for regulating a voltage of the first precharged bit line and a voltage of the second precharged bit line to the same electric potential. The bias compensation unit is electrically connected to the sense amplifier for compensating an input offset voltage of the current-sense amplifier.

Owner:NATIONAL TSING HUA UNIVERSITY

Driving circuit of voice coil motor

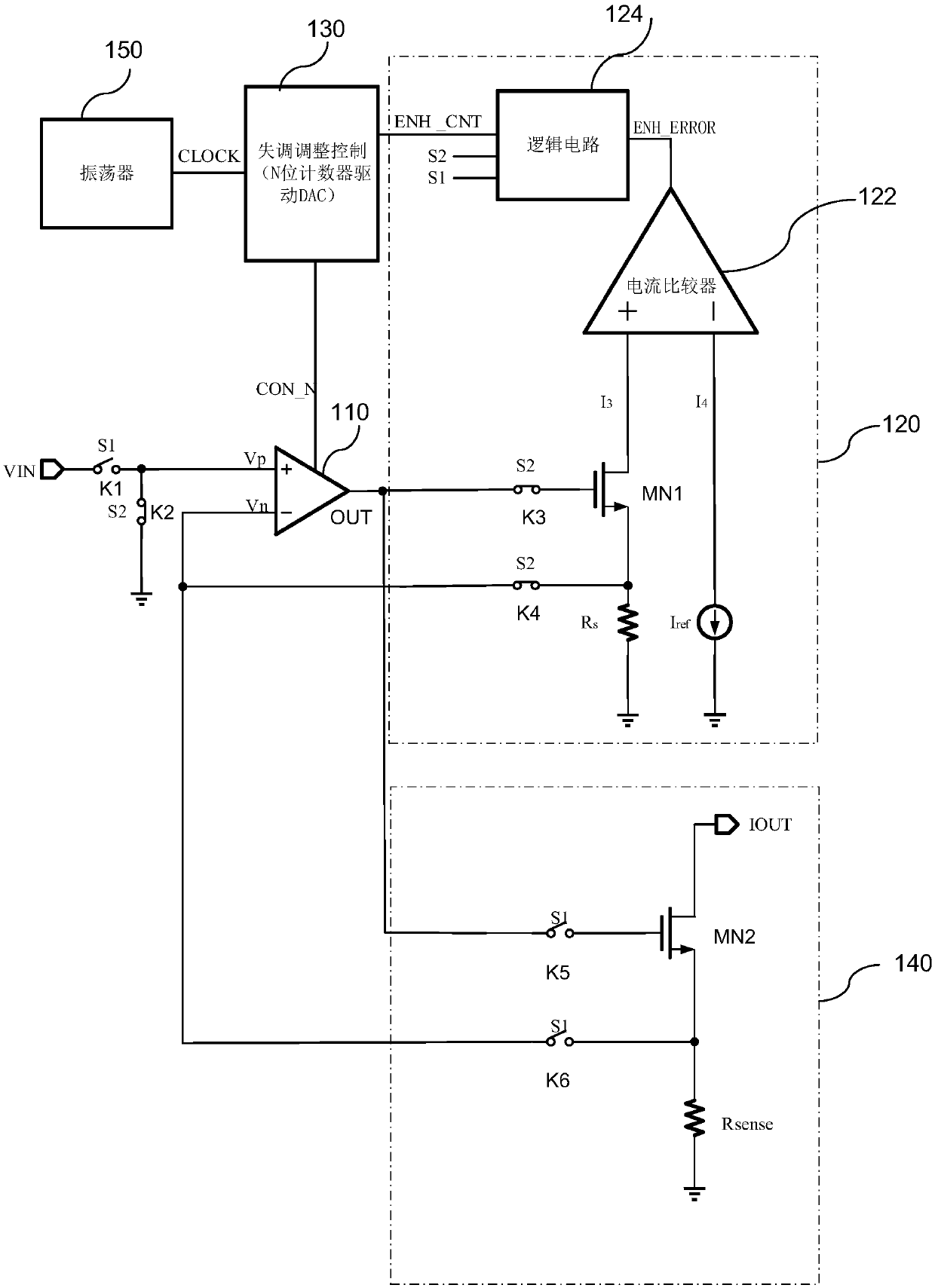

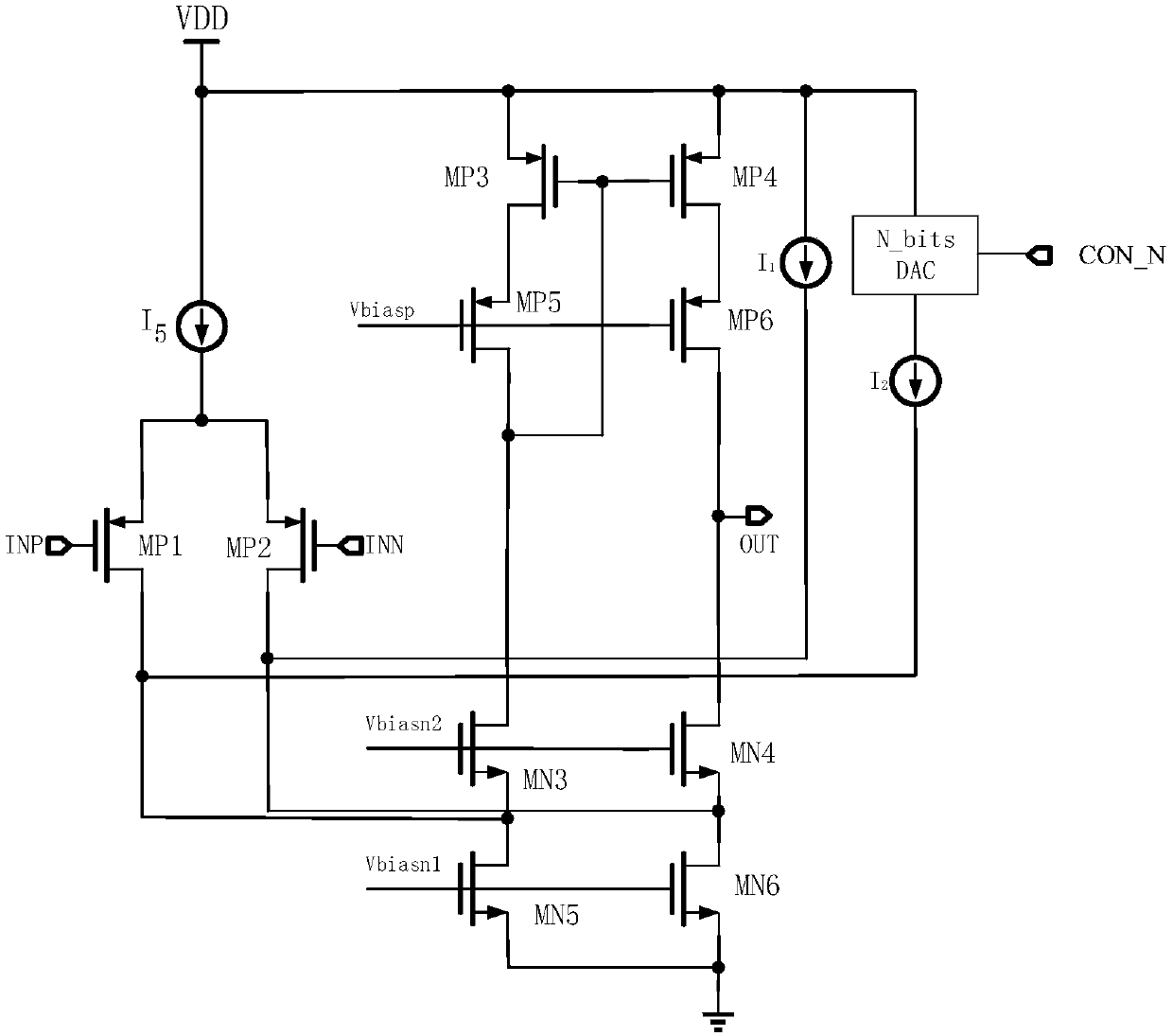

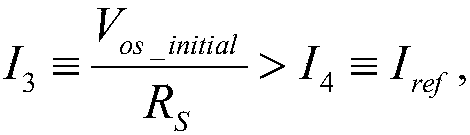

ActiveCN107666264ALower Input Offset VoltageAdaptive Input Offset VoltageDC motor speed/torque controlAC motor controlConstant current sourceEngineering

The invention provides a driving circuit of a voice coil motor. The driving circuit comprises a driving stage operational amplifier, a switch K1, a switch K2, an imbalance detection and control circuit and an imbalance adjustment control circuit. The first input end of the driving stage operational amplifier is connected with an input voltage through the switch K1, and is grounded through the switch K2. The imbalance detection and control circuit comprises a switch K3, a switch K4, an MOS tube MN1, a resistor Rs, a reference constant-current source, a current comparator and a logic circuit. The MN1 and the resistor Rs are sequentially connected between the first input end and the grounding end of the current comparator. The control end of the MN1 is connected with the output end of the driving stage operational amplifier through the switch K3. The switch K4 is connected between the second input end of the driving stage operational amplifier and the second connecting end of the MN1. Thereference constant-current source is connected between the second input end and the grounding end of the current comparator. The logic circuit outputs a calibration control signal based on a comparison result output by the current comparator. The imbalance adjustment control circuit outputs a current control signal based on the calibration control signal so as to perform the imbalance calibrationon the driving operational amplifier.

Owner:WUXI ETEK MICROELECTRONICS

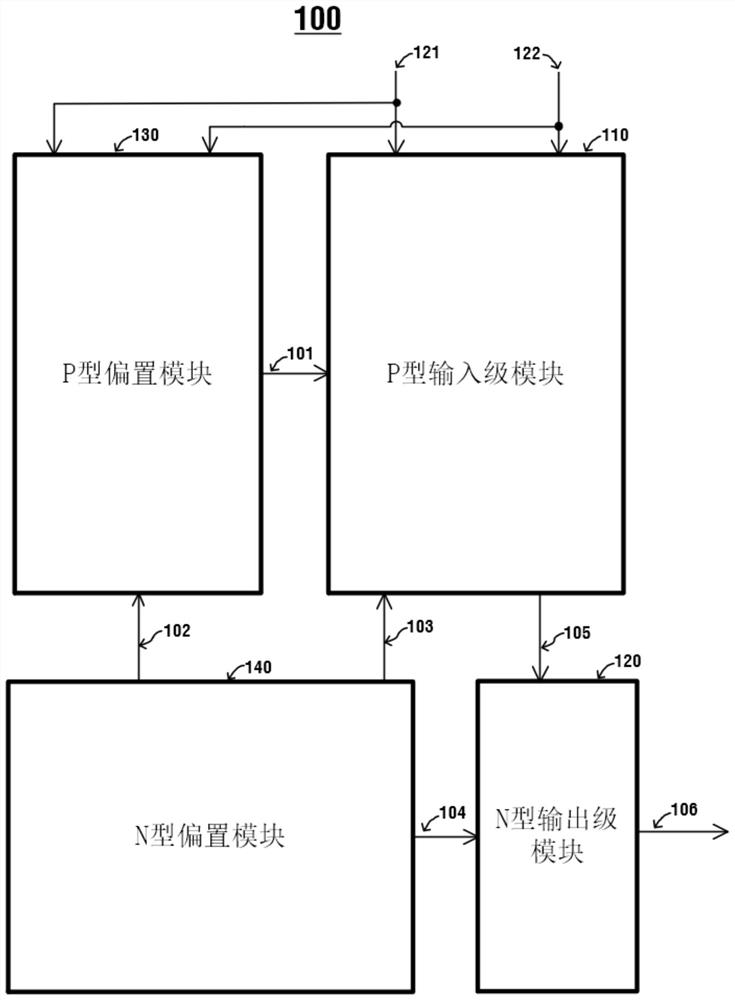

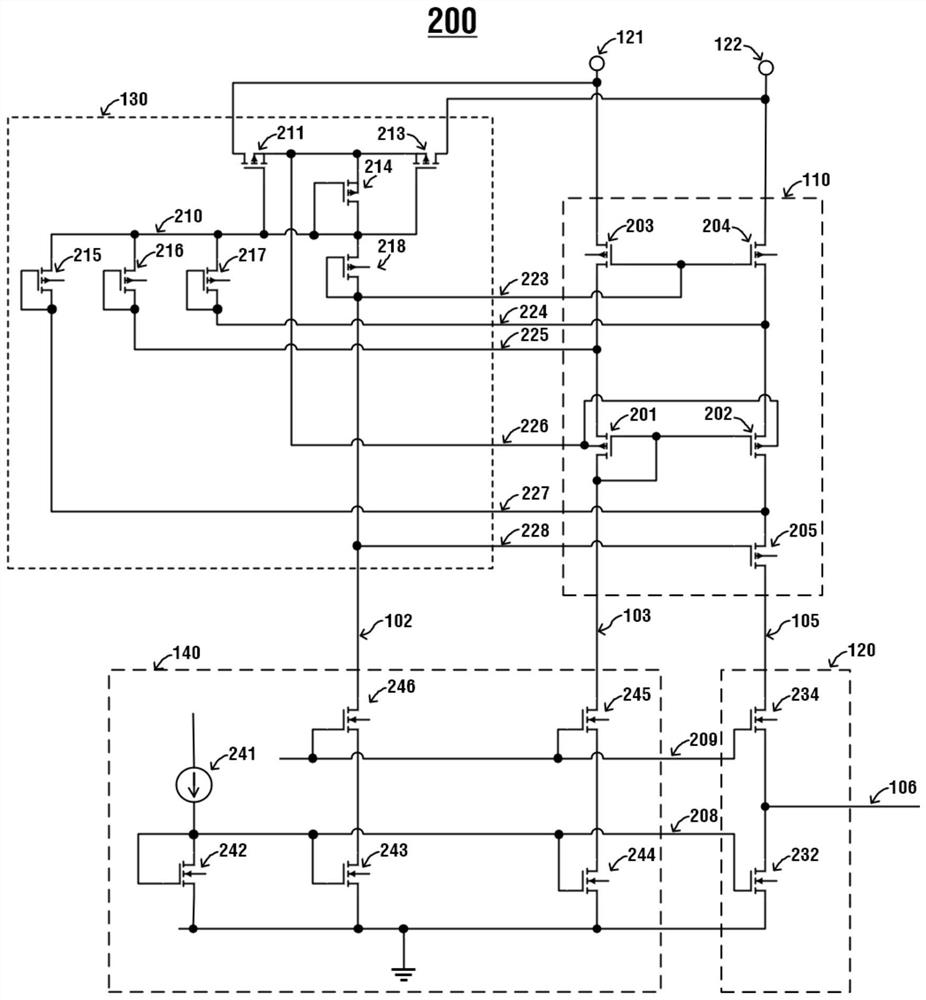

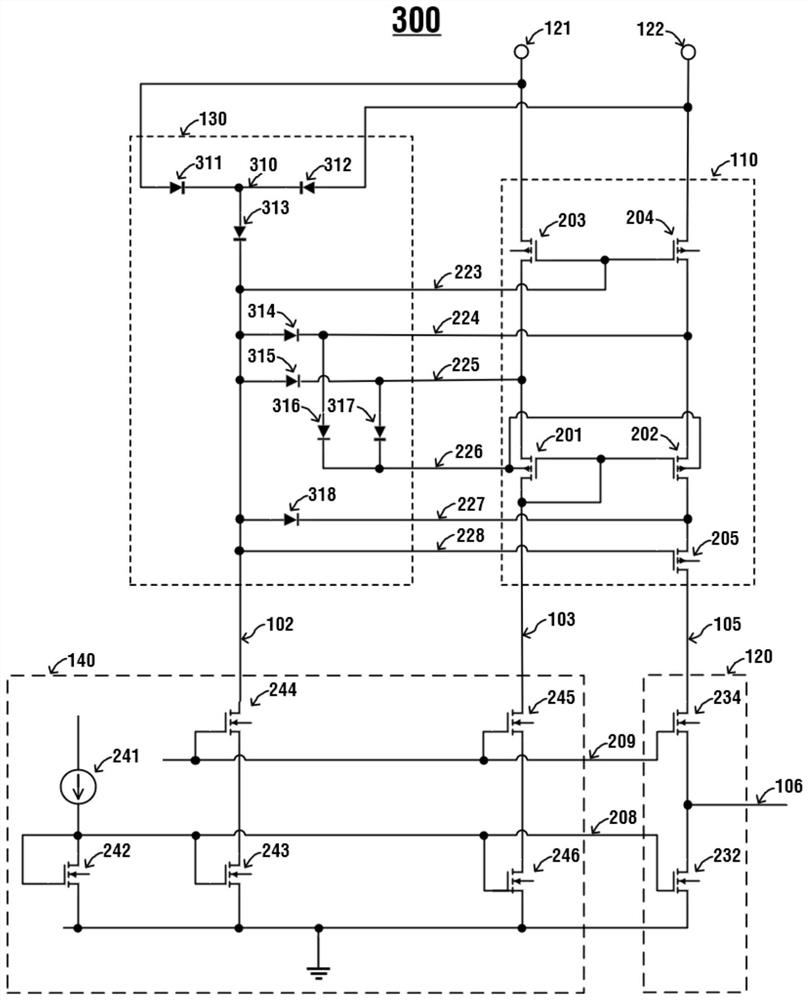

Differential voltage detection circuit with wide voltage input range

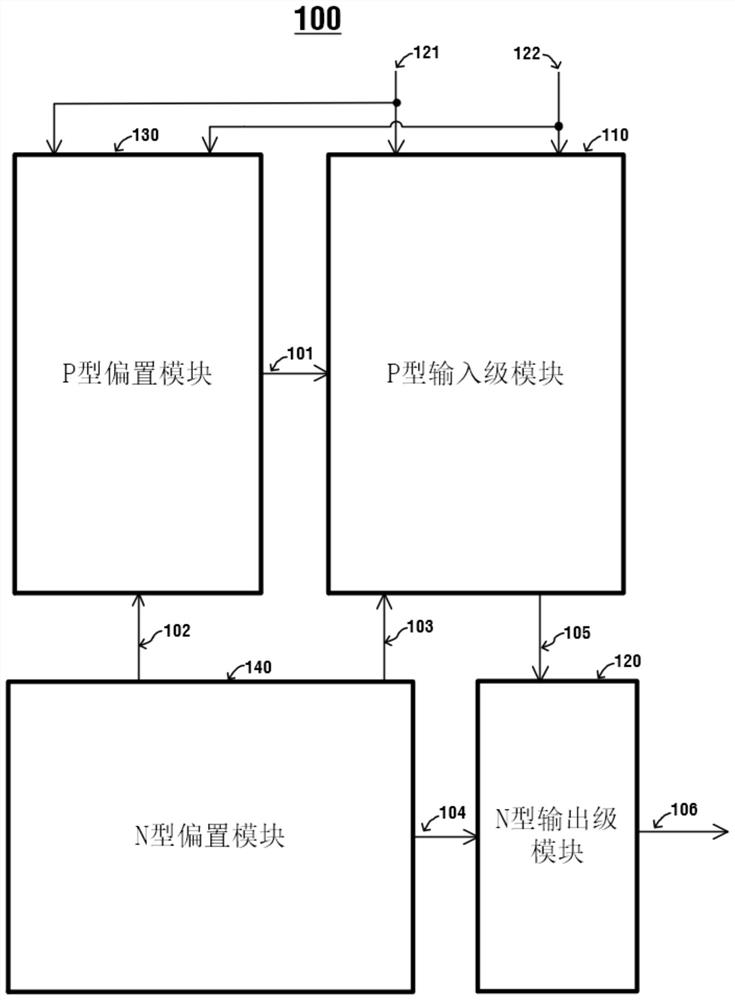

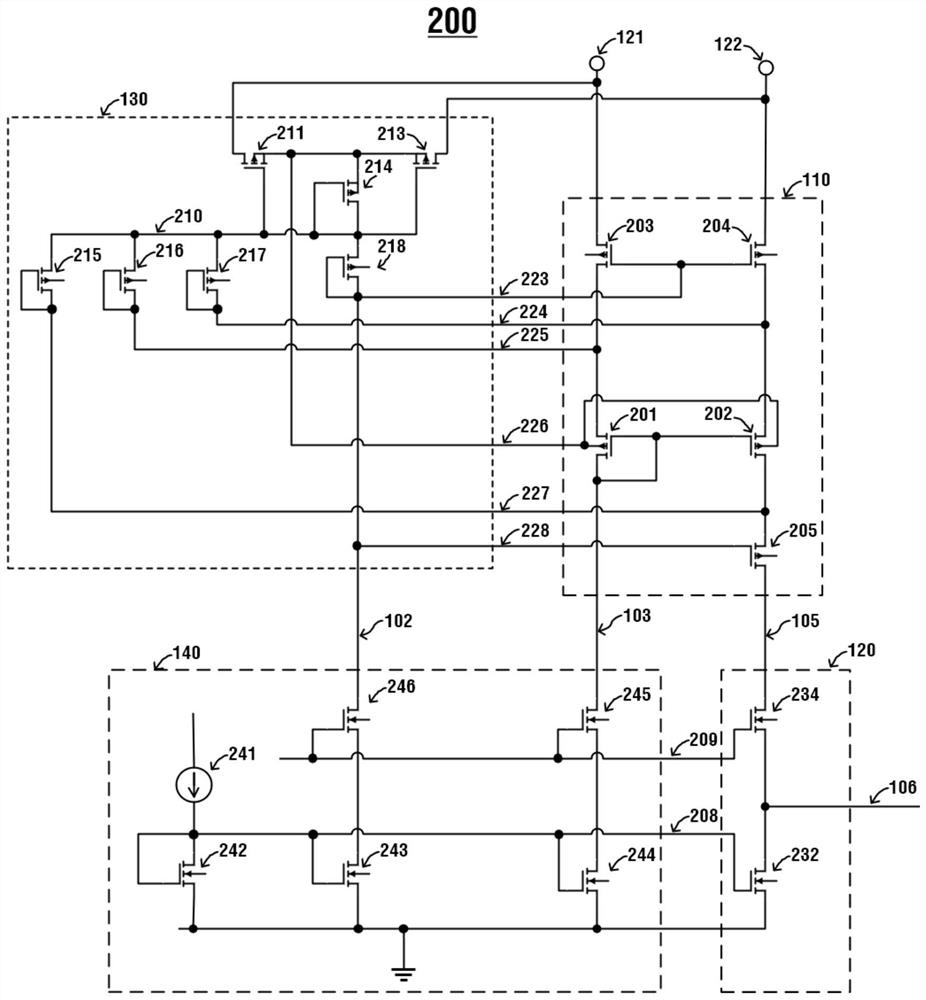

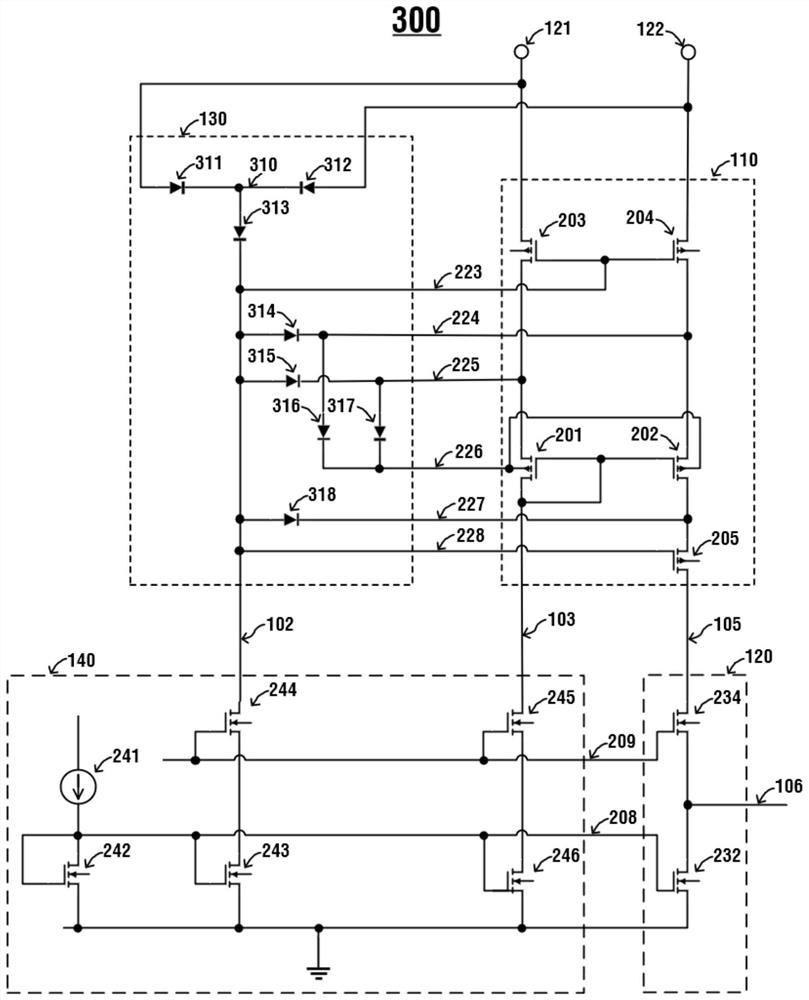

ActiveCN113341212AWide input voltage rangeLower Input Offset VoltageMeasurement using digital techniquesReference currentHemt circuits

The invention discloses a differential voltage detection circuit with a wide voltage input range. The circuit comprises a P-type input stage module which is used for receiving a voltage differential input signal and converting the voltage differential input signal into a single-ended output current, a P-type bias module which is used for providing bias voltage and voltage clamping protection for a transistor in the P-type input stage module, an N-type bias module which is used for providing bias current for the P-type bias module and the P-type input stage module and an N-type output stage module. The N-type bias module provides bias voltage or bias current for the N-type output stage module, and the N-type output stage module outputs a signal representing the relative voltage level of the differential input signal according to the difference value of the single-end output current and the bias reference current. Two differential input voltage signals can be detected and output, a wide input voltage range can be realized, the input offset voltage of the circuit can be effectively reduced, and the circuit can be used as a high-voltage comparator and a high-voltage operational amplifier and is high in practicability.

Owner:晶通微电子(南京)有限公司

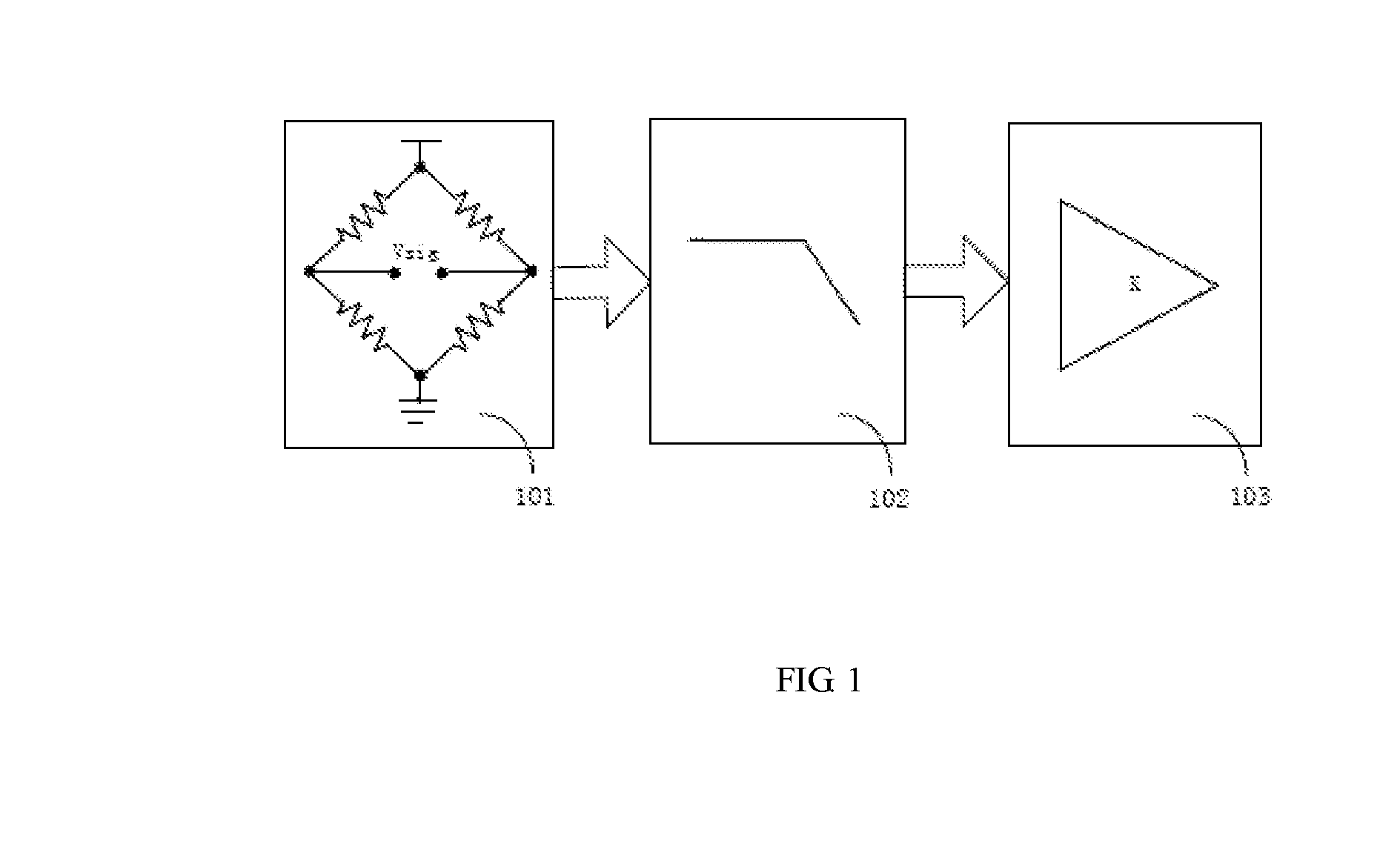

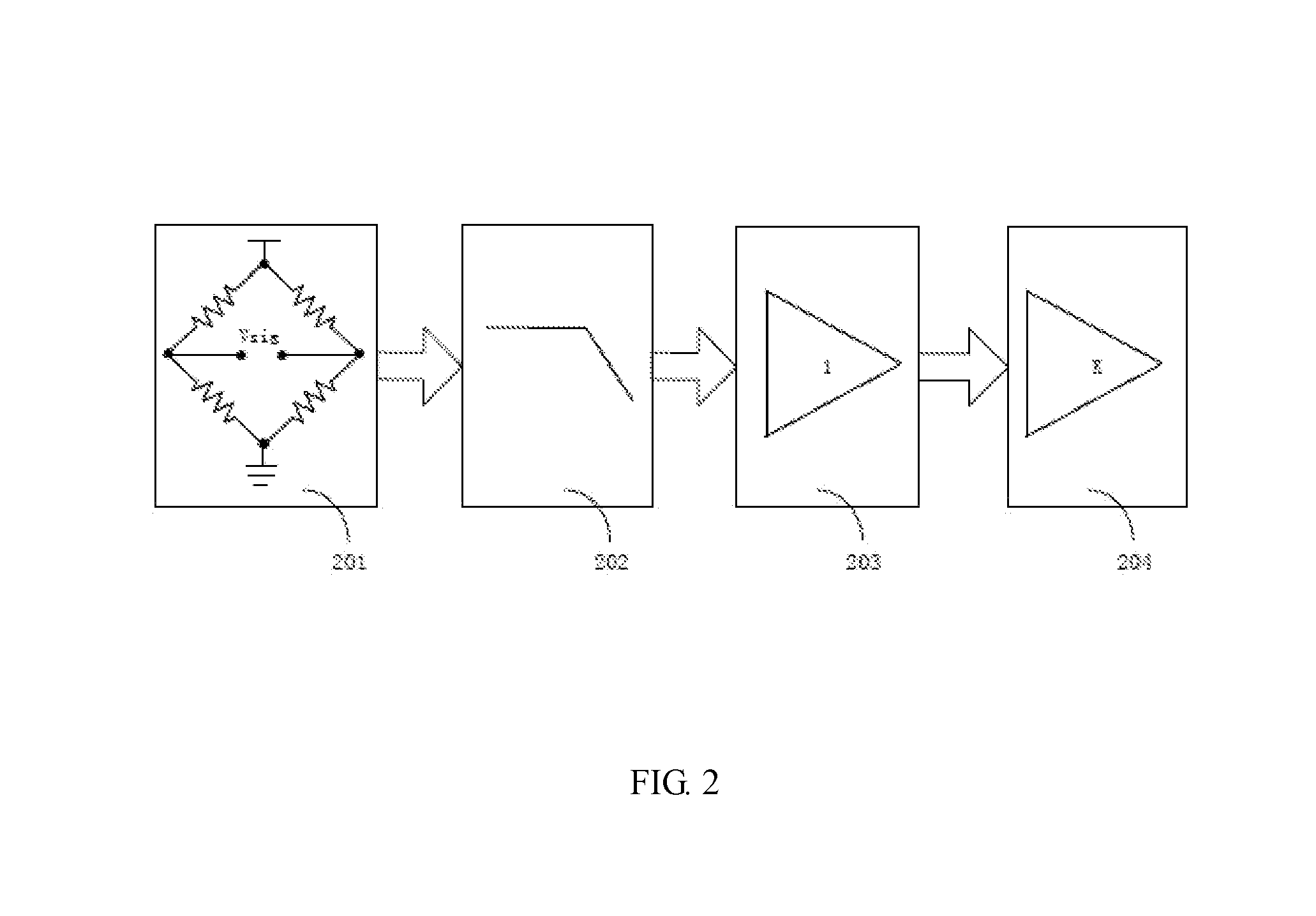

Sensor control circuit and electronic apparatus

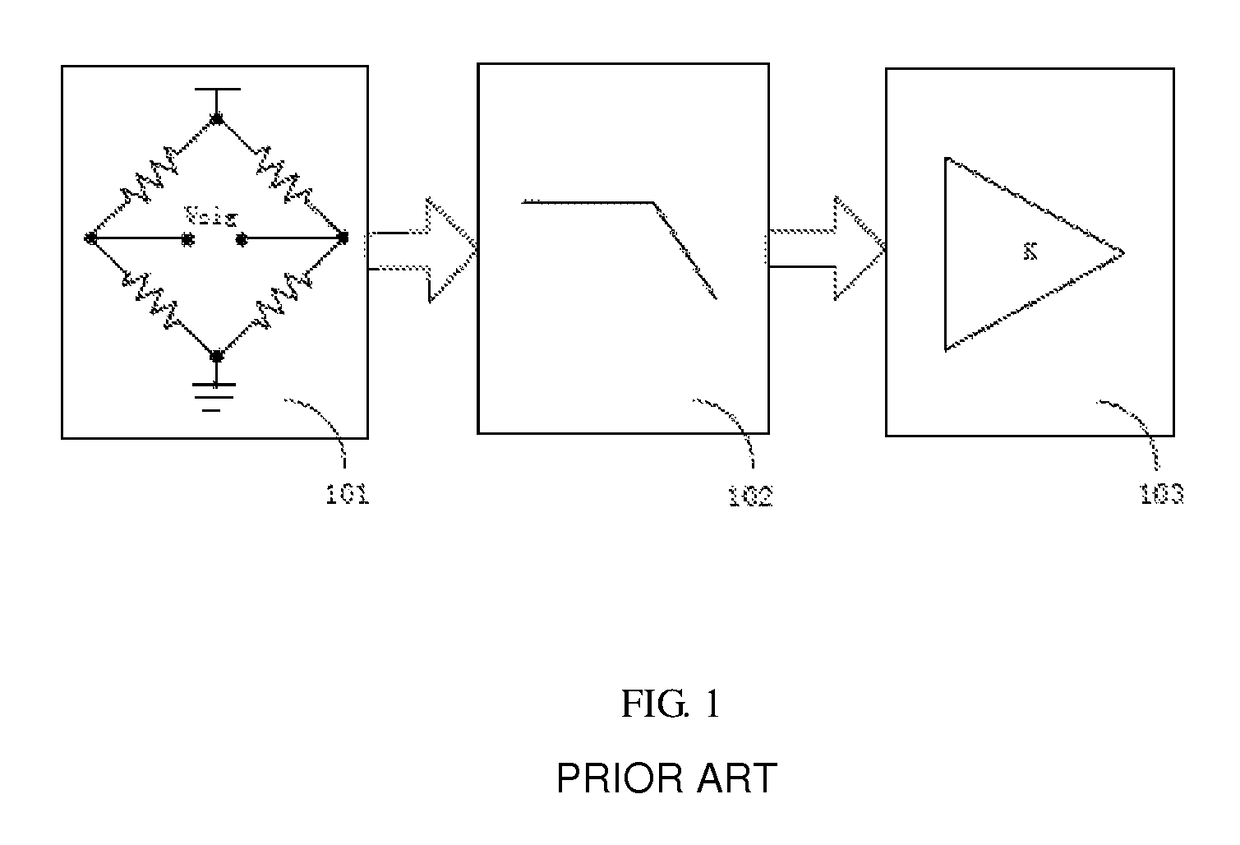

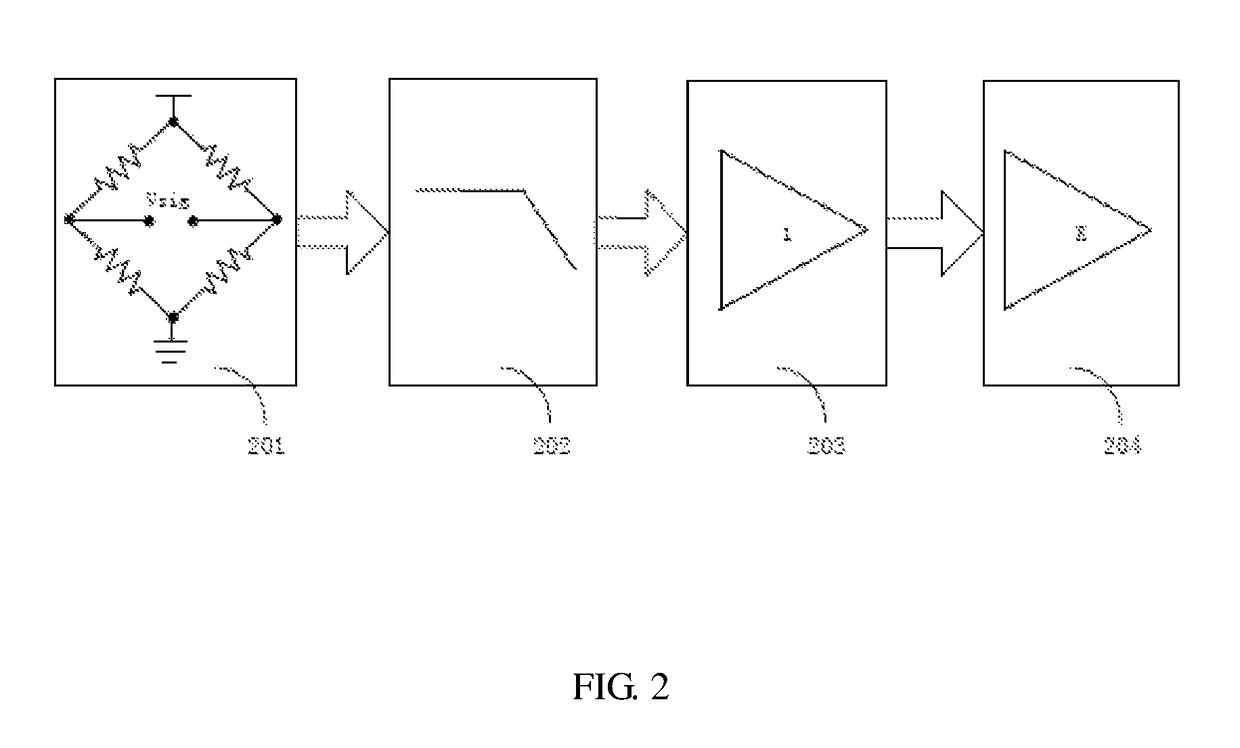

ActiveUS20160233840A1Lower Input Offset VoltageImprove rendering capabilitiesMultiple-port networksAcceleration measurement using interia forcesEngineeringControl circuit

A sensor control circuit comprises a sensor (201), a filtering circuit (202), a buffering circuit (203), and an amplifying circuit (204). An output end of the sensor (201) is connected to an input end of the filtering circuit (202), an output end of the filtering circuit (202) is connected to an input end of the buffering circuit (203), and an output end of the buffering circuit (203) is connected to an input end of the amplifying circuit (204). Because the buffering circuit (203) is disposed between the filtering circuit (202) and the amplifying circuit (204), the sensor circuit has an advantage of full sampling. Further provided is an electronic apparatus using the sensor control circuit.

Owner:CSMC TECH FAB2 CO LTD

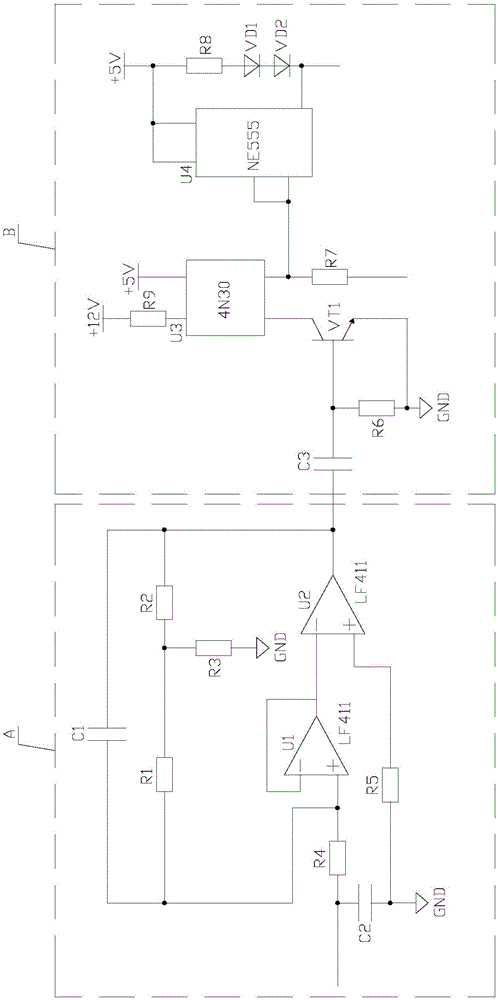

Detecting circuit for heart sound pulse detection

InactiveCN106725373AImprove long-term stabilityImprove reliabilityCatheterCapacitanceAudio power amplifier

The invention relates to a detecting circuit for heart sound pulse detection. The detecting circuit comprises a pre-amplification circuit and an isolated output circuit, the pre-amplification circuit comprises a first operational amplifier, a second operational amplifier, a first resistor, a second resistor, a third resistor, a fourth resistor, a fifth resistor, a first capacitor and a second capacitor, and the isolated output circuit comprises a first integrated circuit, a second integrated circuit, a sixth resistor, a seventh resistor, an eighth resistor and a ninth resistor. According to the detecting circuit for heart sound and pulse detection, a double operation-amplification compensation form is adopted for the pre-amplification circuit, a compensation function is achieved for temperature drift of an operational amplifier, therefore, the long-term stability of the circuit can be enhanced, and the detecting reliability of the circuit is improved well. According to the isolated output circuit, detected signals and an internal detecting circuit can be isolated through the isolating function of the first integrated circuit, therefore, the reliability of the isolated output circuit is improved, and heart sound pulses are reliably detected.

Owner:吉安市井开区吉军科技有限公司

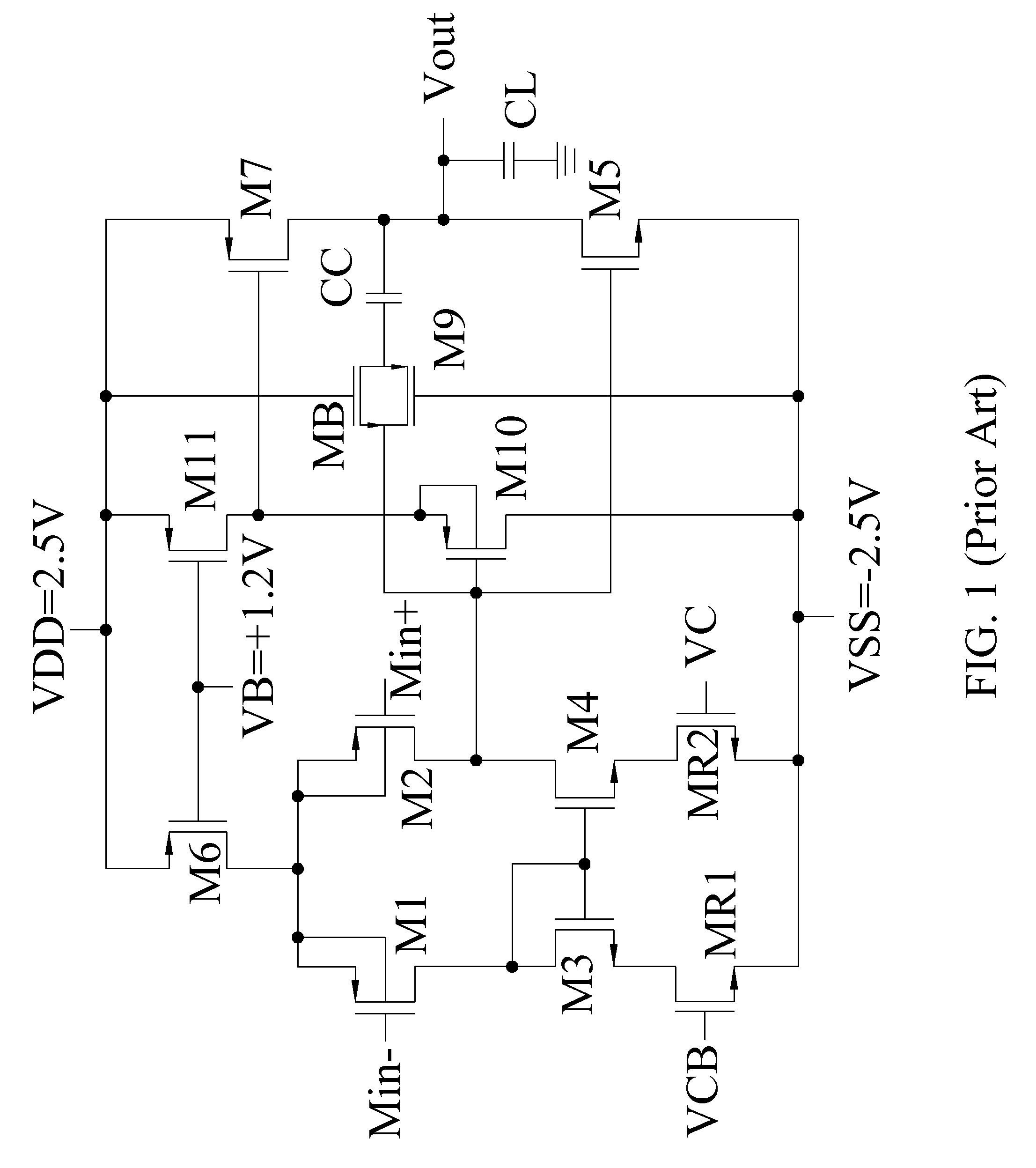

Operational amplifier circuit

ActiveUS9219451B2Reduce inputLower Input Offset VoltageAmplifier modifications to raise efficiencyDifferential amplifiersAudio power amplifierCurrent consumption

Owner:ABLIC INC

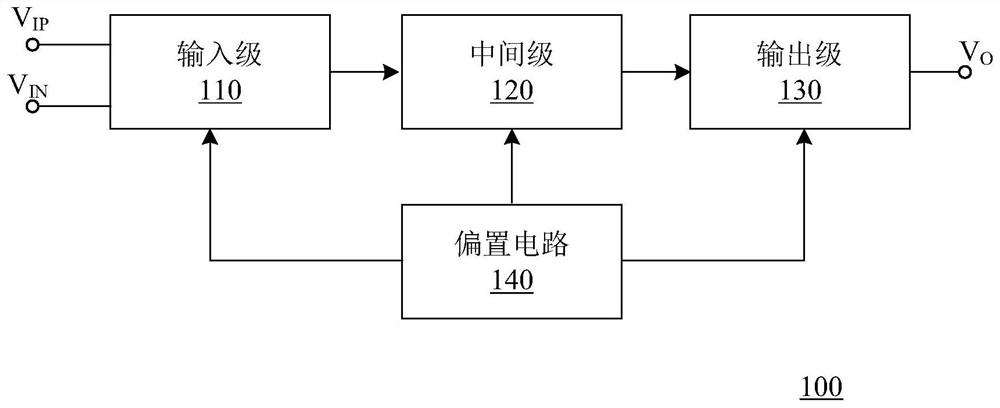

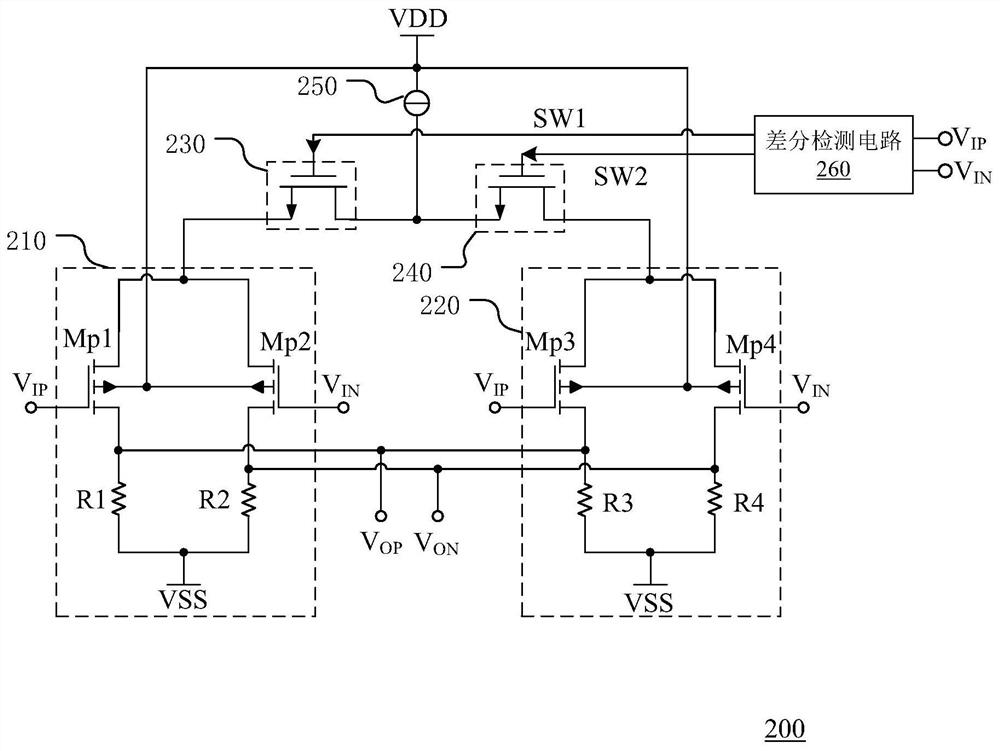

Differential input circuit, control method thereof and differential amplifier

ActiveCN112242823AReduce precisionAvoid Increased Input Offset VoltageDifferential amplifiersDc-amplifiers with dc-coupled stagesHemt circuitsNegative power

The invention discloses a differential input circuit, a control method of the differential input circuit, and a differential amplifier. The differential input circuit comprises: a first differential input stage connected in series with a first switch between a positive power supply terminal and a negative power supply terminal; a second differential input stage, wherein the second differential input stage and the second switch are connected in series between the positive power supply end and the negative power supply end; a differential detection circuit which is used for conducting one of thefirst switch and the second switch according to a first input signal and a second input signal, wherein the positive input ends of the first differential input stage and the second differential inputstage receive the first input signal, the negative input ends of the first differential input stage and the second differential input stage receive the second input signal, the size of the differential transistor pair in the first differential input stage is different from the size of the differential transistor pair in the second differential input stage, so that increase of input offset voltagecaused by asymmetry of the transistor pair of the single input stage under long-time large differential signal work can be prevented, and the precision of the amplifier is further prevented from being influenced.

Owner:江阴圣邦微电子制造有限公司

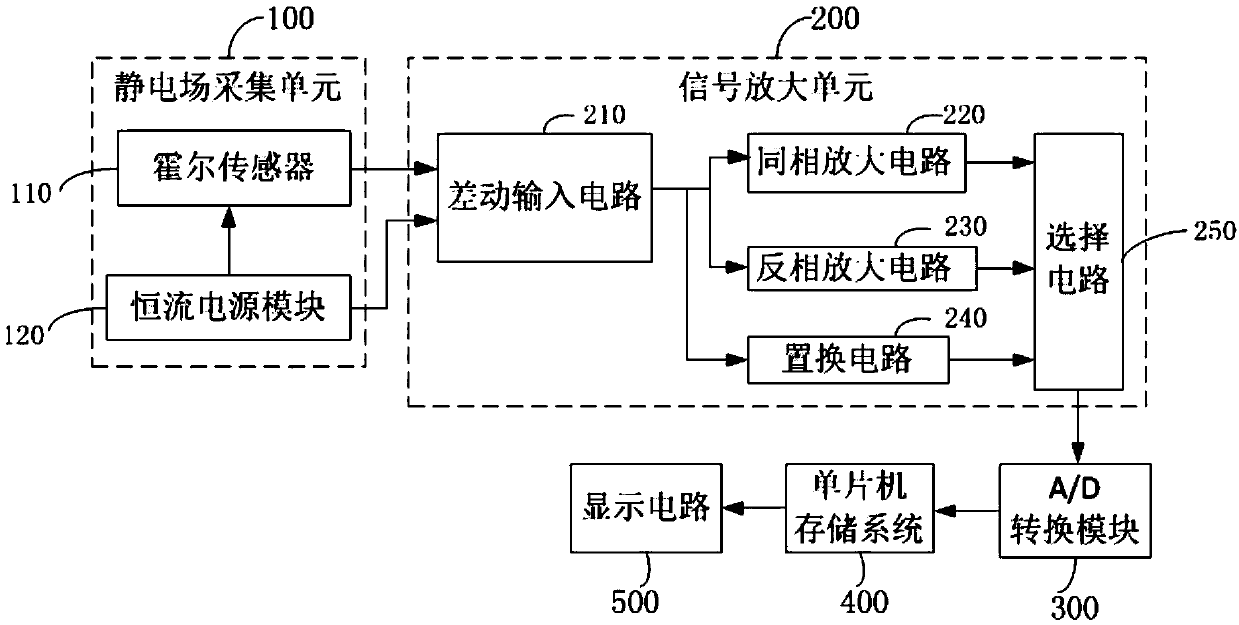

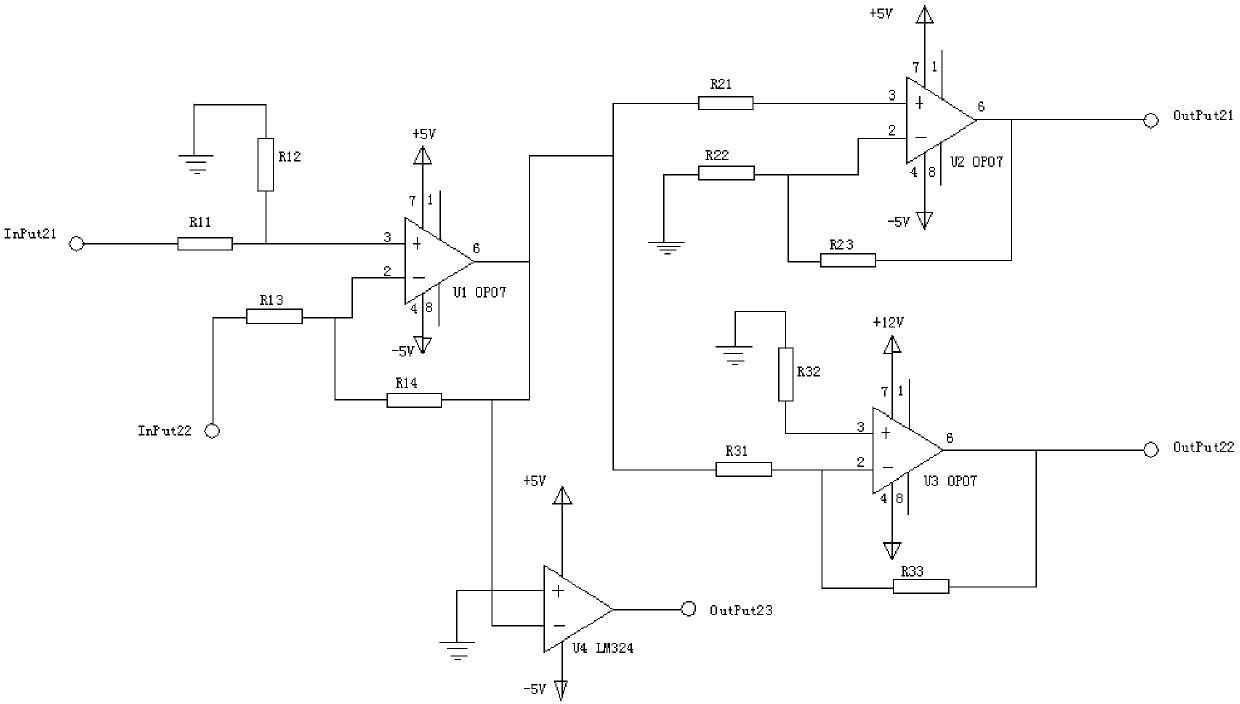

An Electrostatic Field Tester Based on Hall Sensor

ActiveCN106680602BLow costLower Input Offset VoltageElectrostatic field measurementsMicrocomputerSignal amplification

The invention discloses a hall-sensor-based electrostatic field tester, comprising an electrostatic field acquisition unit, a signal amplifying unit, an A / D (analog / digital) conversion module, a single-chip microcomputer storage system and a display unit; the electrostatic field acquisition unit comprises a hall sensor and a constant-current power module providing stable operating voltage for the hall sensor; the signal amplifying unit comprises a differential input circuit, an in-phase amplifying circuit, an inverse phase amplifying circuit, a displacement circuit and a selector circuit, selection is made by the selector circuit, and a forward electric field or a reverse electric field is output. The hall-sensor-based electrostatic field tester is low in cost, small in size and high in sensitivity, has wide adaptive frequency and temperature ranges, and is suitable for measuring both constant electric fields and alternating electric fields.

Owner:昆山兢美电子科技有限公司

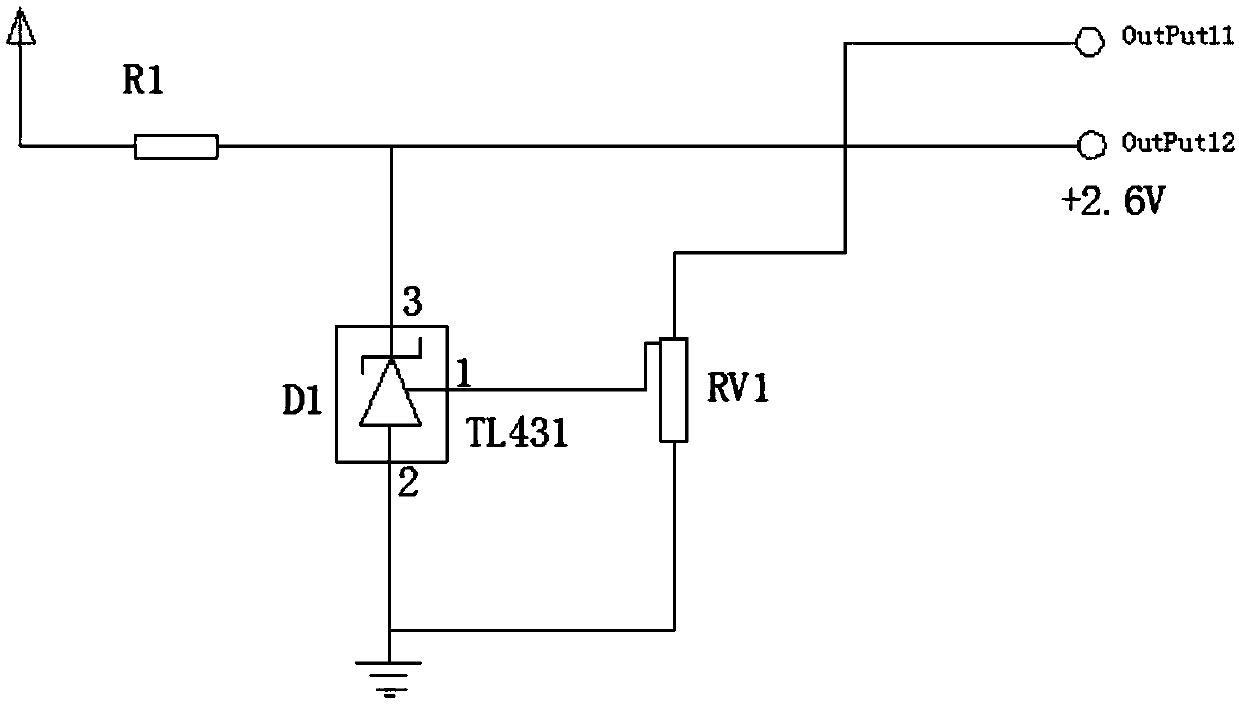

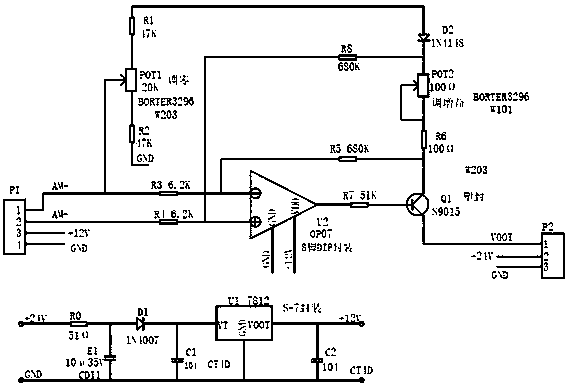

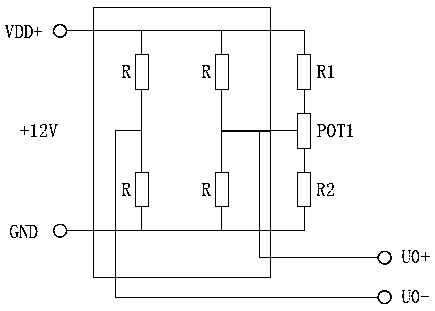

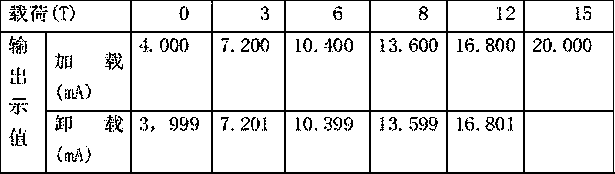

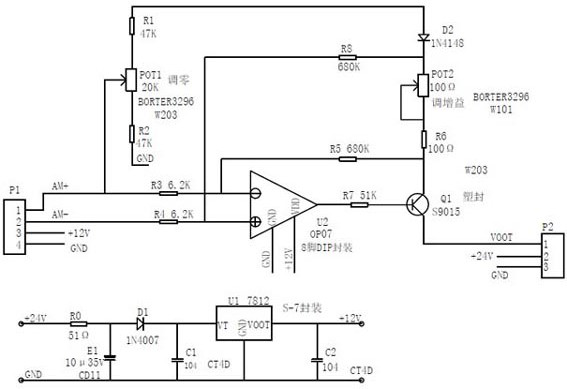

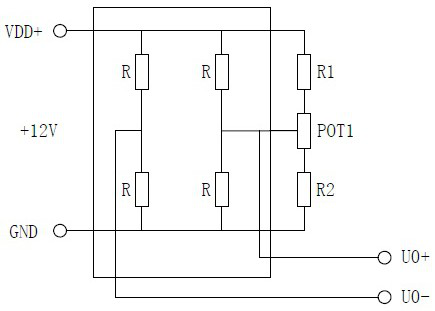

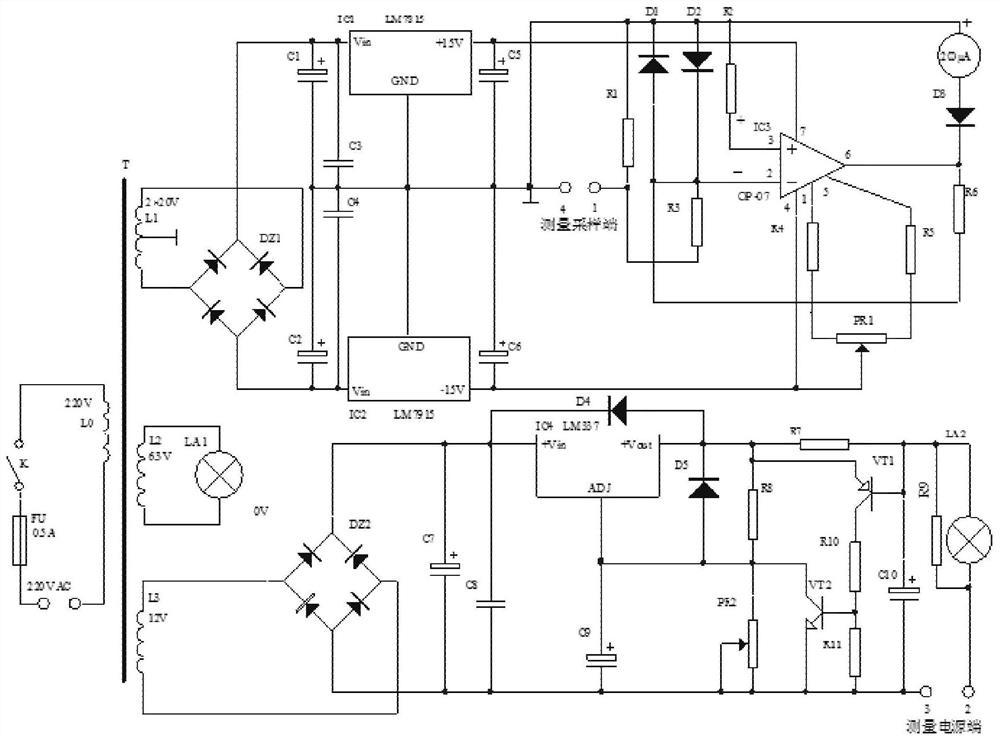

Load sensor signal transmitting device

InactiveCN111585532AEliminate distractionsImprove stabilityDifferential amplifiersDc-amplifiers with dc-coupled stagesCapacitanceSignal on

The invention discloses a load sensor signal transmitting device in the technical field of sensors. The load sensor signal transmitting device comprises an AC filter circuit, a zero setting circuit, adifferential voltage amplification circuit and a sampling circuit. The zero setting circuit is connected to the AC filter circuit. The differential voltage amplification circuit is connected to the AC filter circuit and the zero setting circuit. The sampling circuit is connected to the zero setting circuit and the differential voltage amplification circuit. The AC filter circuit comprises a resistor R0, an electromotive force E1, a diode D1, a capacitor C1, a three-terminal regulator U1 and a capacitor C2. One end of the resistor R0 is connected to a + 24V power supply, and one end of the diode D1 is connected with the other end of the resistor R0. According to the invention, the interference of noise on a voltage signal on a transmission line can be effectively eliminated, and the signalloss is reduced.

Owner:徐州电子技术研究所水电自动化工程处

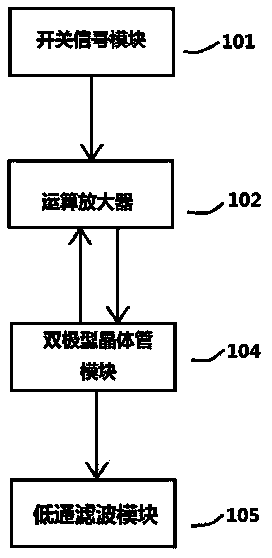

Switch control band-gap reference circuit with low offset voltage

InactiveCN104111684ALower Input Offset VoltageHigh precisionElectric variable regulationLow offsetBand gap

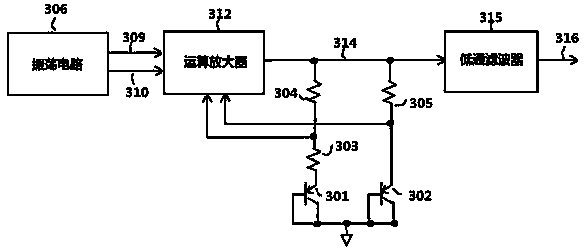

The invention provides a switch control band-gap reference circuit with the low offset voltage. The switch control band-gap reference circuit comprises a switching signal module, an operational amplifier, a bipolar transistor module and a low-pass filtering module. The output end of the witching signal module is connected with the input end of the operational amplifier, the output end of the operational amplifier is connected with the bipolar transistor module, and the bipolar transistor module is connected with the low-pass filtering module. The switching signal module comprises a first switching signal output end and a second switching signal output end, the first switching signal output end is connected with the in-phase input end of the operational amplifier, and the second switching signal output end is connected with the inverted input end of the operational amplifier. The switch control band-gap reference circuit has the advantages that the input offset voltage of the operational amplifier is lowered, and the accuracy of band-gap reference voltage signals is improved.

Owner:SHENZHEN KECHUANGDA MICRO ELECTRONICS CO LTD

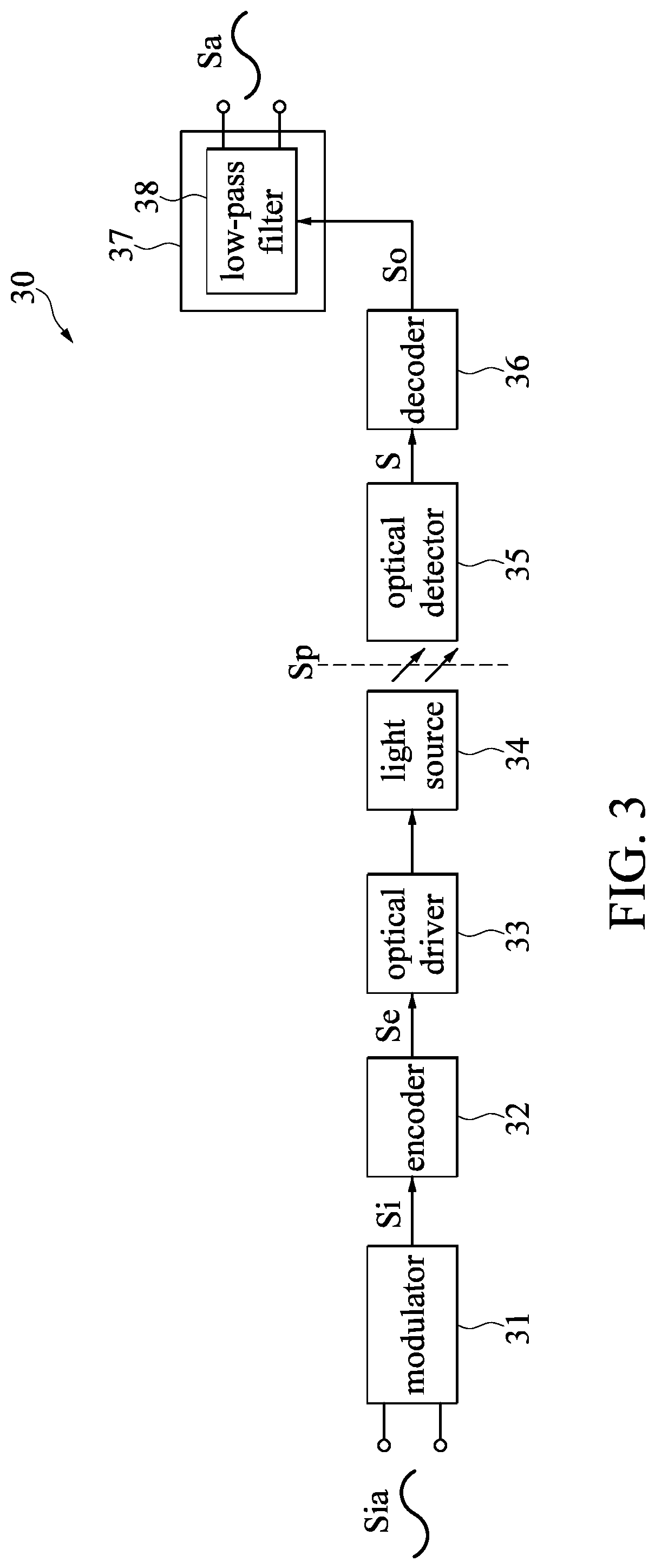

Encoding and decoding method for optical isolation amplifier employing sigma-delta modulation technology

ActiveUS11025268B1Restore accuratelyImprove linearityElectric signal transmission systemsAnalogue conversionDecoding methodsSoftware engineering

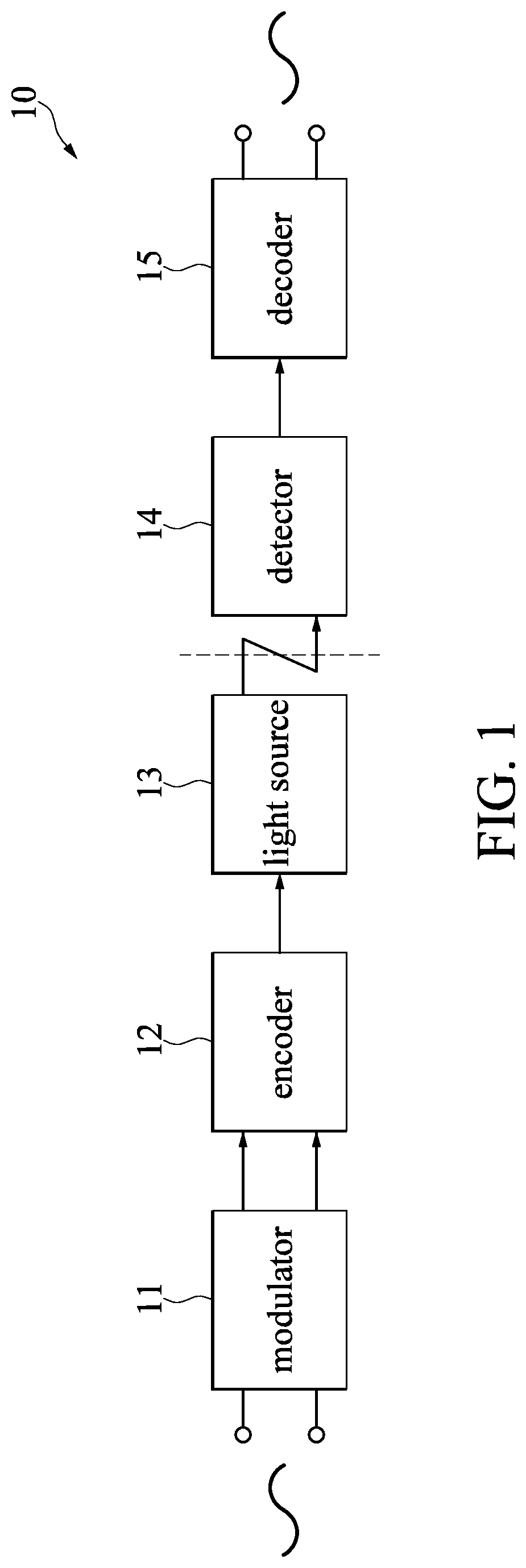

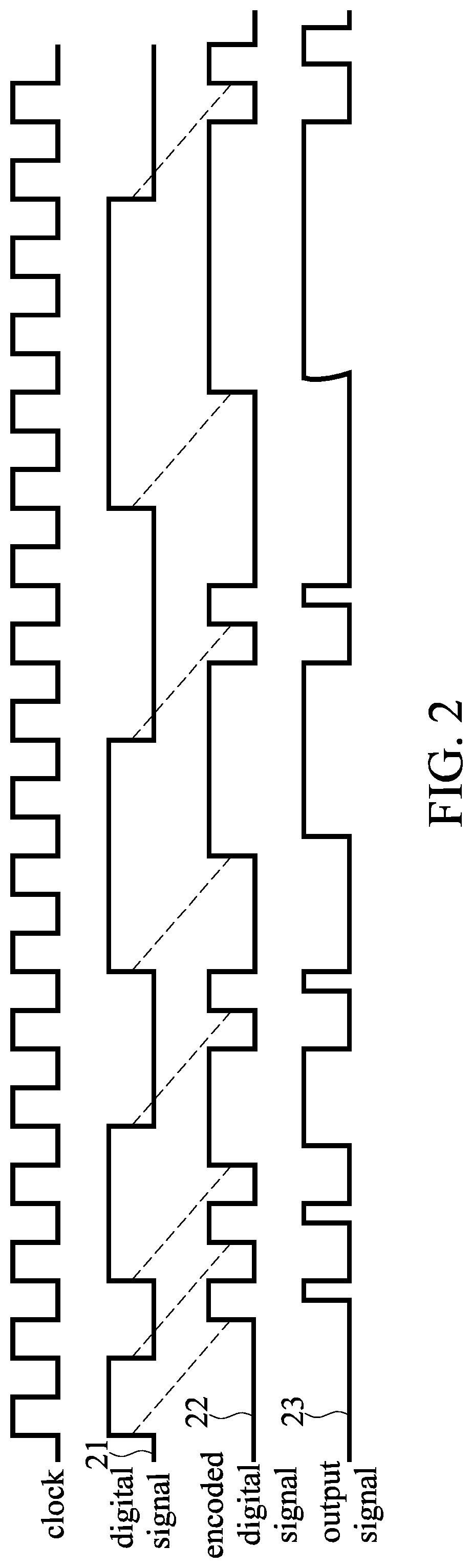

An encoding and decoding method for an optical isolation amplifier including an encoder, an optical driver, a light source, an optical detector, and a decoder, and employing sigma-delta modulation technology is provided. The method includes: generating a plurality of first pulses, each having a predetermined pulse width, through the encoder when an input digital signal experiences an input pulse rising or falling edge; outputting an encoded signal having the plurality of first pulses to the optical driver; driving the light source through the optical driver, according to the plurality of first pulses, so as to output an encoded optical signal; generating a detected signal through the optical detector detecting the encoded optical signal, and the detected signal has a plurality of second pulses; and duplicating the input digital signal of the encoder through the decoder, according to the detected signal having the plurality of second pulses.

Owner:LITE ON SINGAPORE PTE LTD

Circuit structure for reducing input offset voltage of two-stage operational amplifier

ActiveCN102130659BLower Input Offset VoltageLower Offset VoltageDifferential amplifiersDc-amplifiers with dc-coupled stagesCMOSAudio power amplifier

The invention provides a circuit structure for reducing input offset voltage of a two-stage operational amplifier, which comprises a switching control circuit, a first-stage differential amplification circuit, a second-stage common-source amplification circuit and a compensation network, wherein the output end of the switching control circuit is connected with the input end of the first-stage differential amplification circuit, the output end of the first-stage differential amplification circuit is connected with the input end of the second-stage common-source amplification circuit, and the compensation network is further connected between the input end and the output end of the second-stage common-source amplification circuit. The circuit structure has the benefits that the offset of the operational amplifier is reduced by adopting an MOS (metal oxide semiconductor) switching tube to control and exchange signals at the positive and the negative input ends and the signals at the output end of the operational amplifier; as only the MOS switching tube is increased in the circuit, the circuit structure only needs very small area and very low power consumption; and the circuit does not affect the gain of the operational amplifier, the phase margin, the power supply voltage rejection ratio, the common-mode input range and other performance indexes while reducing the input offset voltage of the operational amplifier, and can be applied in mainstream CMOS (complementary metal oxide semiconductor) circuit systems.

Owner:XIAN JIEHANG ELECTRONICS SCI & TECH CO LTD

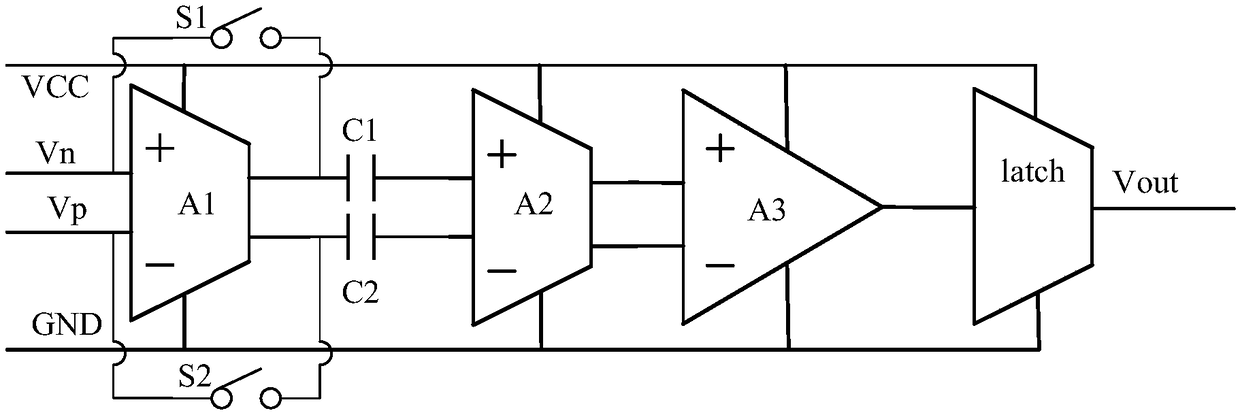

Comparator Circuits for Analog-to-Digital Converters

ActiveCN104283566BHigh precisionReduce power consumptionAnalogue/digital conversionElectric signal transmission systemsAudio power amplifierAnalog-to-digital converter

The invention provides a comparison circuit for an analog-digital converter. The comparison circuit comprises a first operational amplifier, a first detuning calibration capacitor, a second detuning calibration capacitor, a second operational amplifier, a comparator and a regeneration latch. According to the comparison circuit, higher precision and low power consumption can be acquired on the premise that the performance requirement for an original comparator is met, the input detuning voltage of the comparator is effectively reduced, and the comparison circuit can be applied to circuits of SAR type ADC converters and other analog-digital converters.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

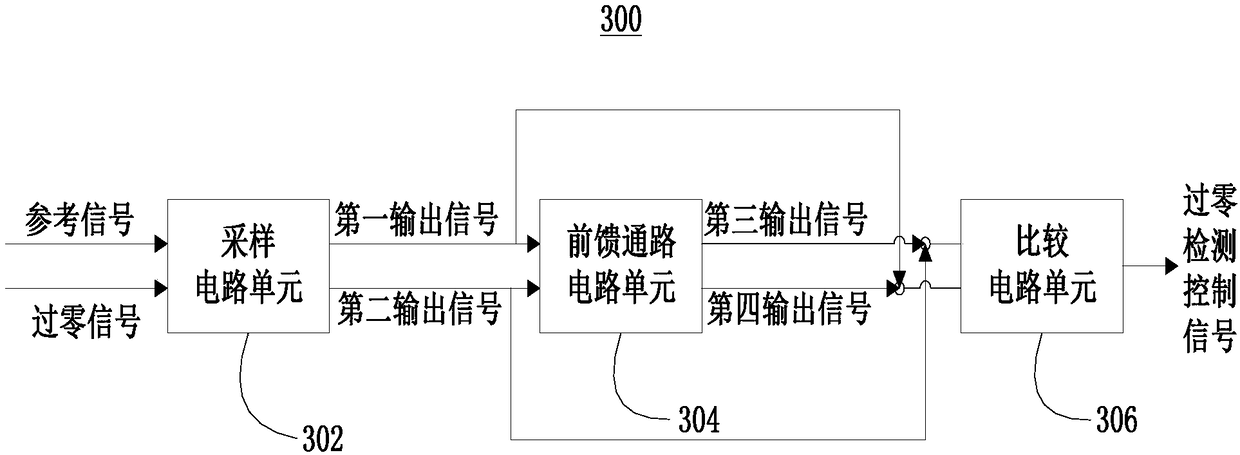

Zero-crossing detection circuit and switching power supply including the circuit

ActiveCN105807125BImprove transconductanceImprove transient responseCurrent/voltage measurementControl signalTransconductance

The invention relates to a zero-crossing detection circuit.The zero-crossing detection circuit comprises a sampling circuit unit, a feedforward access circuit unit and a comparison circuit unit.The sampling circuit unit receives a reference signal and a zero-crossing signal, outputs a first output signal according to the reference signal and outputs a second output signal according to the zero-crossing signal; the feedforward access circuit unit receives the first output signal and the second output signal, outputs a third output signal according to the first output signal and outputs a fourth output signal according to the second output signal; the comparison circuit unit outputs a first voltage signal according to the second output signal and the third output signal, outputs a second voltage signal according to the first output signal and the fourth output signal and outputs a zero-crossing detection control signal according to the first voltage signal and the second voltage signal.The first output signal and the second output signal are transmitted to the comparison circuit unit in a reverse superposition mode, an input of the comparison circuit unit is increased, and therefore transconductance of the comparison circuit unit is improved, and a transient response of the zero-crossing detection circuit is accelerated.

Owner:深圳芯智汇科技有限公司

Dynamic comparator

ActiveCN102647189BLower Input Offset VoltageMeet the needs of the designAnalogue/digital conversionElectric signal transmission systemsComparatorInput offset voltage

The invention provides a dynamic comparator. The dynamic comparator comprises a pre-amplification circuit, a dynamic latch circuit and an output-stage circuit which are connected in sequence, wherein the pre-amplification circuit comprises a first-stage amplification unit adopting an input detuning storage technology and a second-stage amplification unit adopting an output detuning storage technology; the dynamic latch circuit is used for amplifying the output signal of the pre-amplification circuit, and transforming the amplified signal into a digital logical output level; the output-stage circuit is used for outputting the digital logical output level at a latched phase, and outputting logic zero at a rest phase. The dynamic comparator provided by the invention adopts a detuning canceling technology and a structure isolating kickback noise in the pre-amplification circuit, thus effectively reducing the input detuning voltage, and greatly meeting the demands for design of high speed and high precision analog-digital convertors.

Owner:昆山启达微电子有限公司

A differential voltage detection circuit with wide voltage input range

ActiveCN113341212BWide input voltage rangeLower Input Offset VoltageMeasurement using digital techniquesReference currentHemt circuits

The invention discloses a differential voltage detection circuit with a wide voltage input range, comprising: a P-type input stage module for accepting voltage differential input signals and converting it into a single-ended output current; a P-type bias module for The transistors in the P-type input stage module provide bias voltage and voltage clamping protection; the N-type bias module is used to provide bias current for the P-type bias module and the P-type input stage module; the N-type output stage module, N The N-type bias module provides bias voltage or bias current for the N-type output stage module. The N-type output stage module outputs a signal representing the relative voltage level of the differential input signal according to the difference between the single-ended output current and the bias reference current. The present application can detect two differential input voltage signals and output signals, can achieve a wide input voltage range, can effectively reduce the input offset voltage of the circuit, can also be used as a high-voltage comparator and a high-voltage operational amplifier, and has strong practicability.

Owner:晶通微电子(南京)有限公司

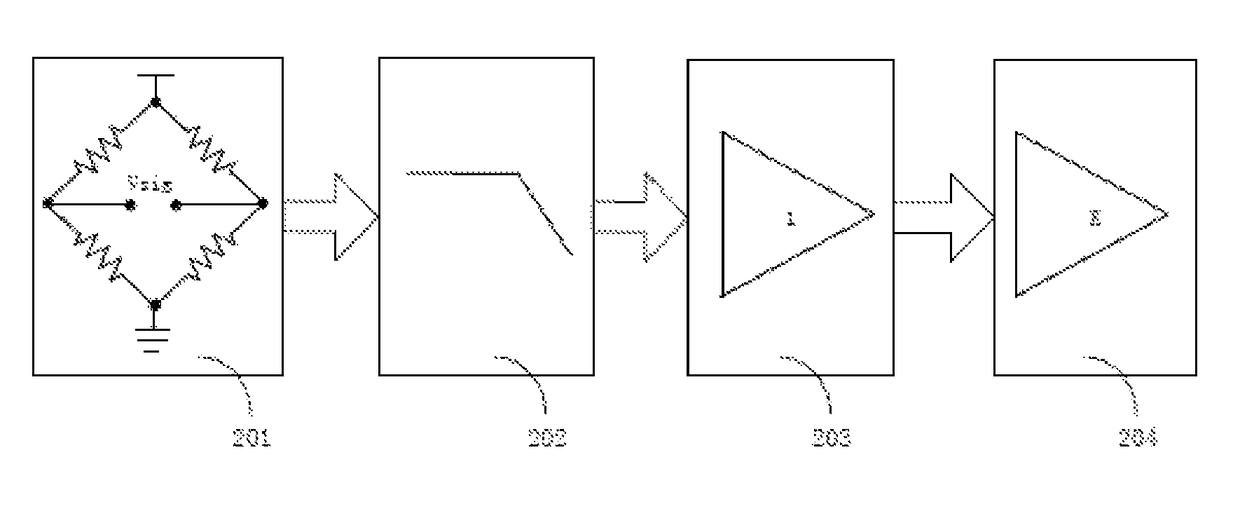

Sensor control circuit and electronic apparatus

ActiveUS10056867B2Lower Input Offset VoltageImprove rendering capabilitiesMultiple-port networksAcceleration measurement using interia forcesEngineeringControl circuit

A sensor control circuit comprises a sensor (201), a filtering circuit (202), a buffering circuit (203), and an amplifying circuit (204). An output end of the sensor (201) is connected to an input end of the filtering circuit (202), an output end of the filtering circuit (202) is connected to an input end of the buffering circuit (203), and an output end of the buffering circuit (203) is connected to an input end of the amplifying circuit (204). Because the buffering circuit (203) is disposed between the filtering circuit (202) and the amplifying circuit (204), the sensor circuit has an advantage of full sampling. Further provided is an electronic apparatus using the sensor control circuit.

Owner:CSMC TECH FAB2 CO LTD

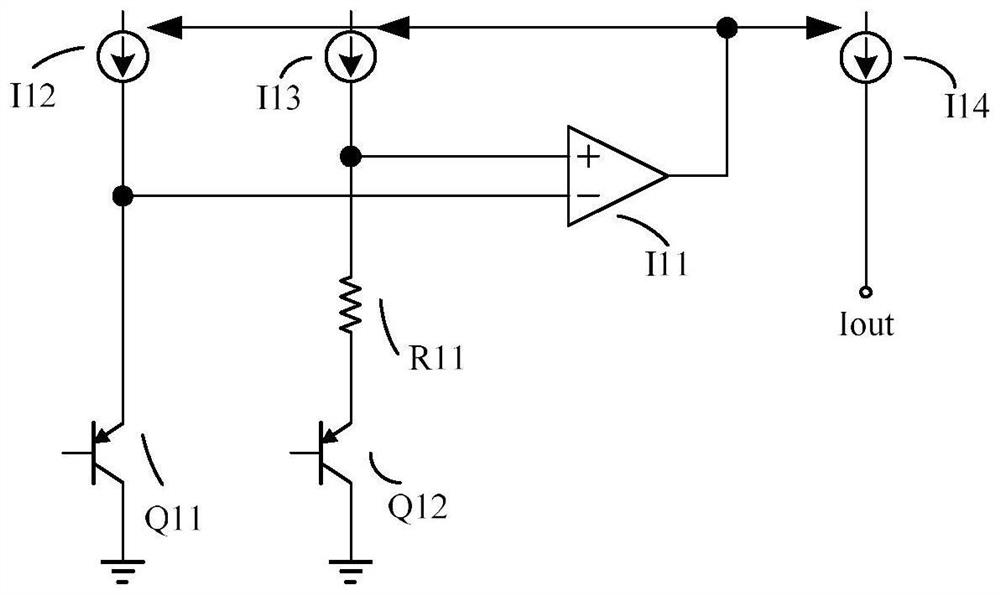

ptat current source circuit

ActiveCN110928353BImprove consistencyEnhanced inhibitory effectElectric variable regulationCurrent sourceResistor

The present invention provides a PTAT current source circuit, comprising: an error operational amplifier; a first transistor including a first PN junction, and a P-type region of the first PN junction is connected to a first current source and an inverter of the error operational amplifier a phase terminal; a second transistor, including a second PN junction, the P-type region of the second PN junction is connected to the second current source and the non-inverting terminal of the error operational amplifier through a series resistor; wherein, the error operational amplifier The output terminal is connected to the first current source, the second current source and the output current source, and is used to control the first current source, the second current source and the output current source, and the output current source has The output is the output of the PTAT current source circuit. The circuit of the invention is simple and effective, the layout area is small, the cost is low, the power consumption is small, and the offset voltage and area of the error operational amplifier are greatly reduced.

Owner:SHANGHAI SHENXILING MICROELECTRONICS TECH CO LTD

A Reference Voltage Correction Circuit for Controlling Buck Converter and Its Application

InactiveCN104460798BHigh precisionHigh DC gainElectric variable regulationĆuk converterTransistor circuits

Owner:南京泰艾微电子有限公司

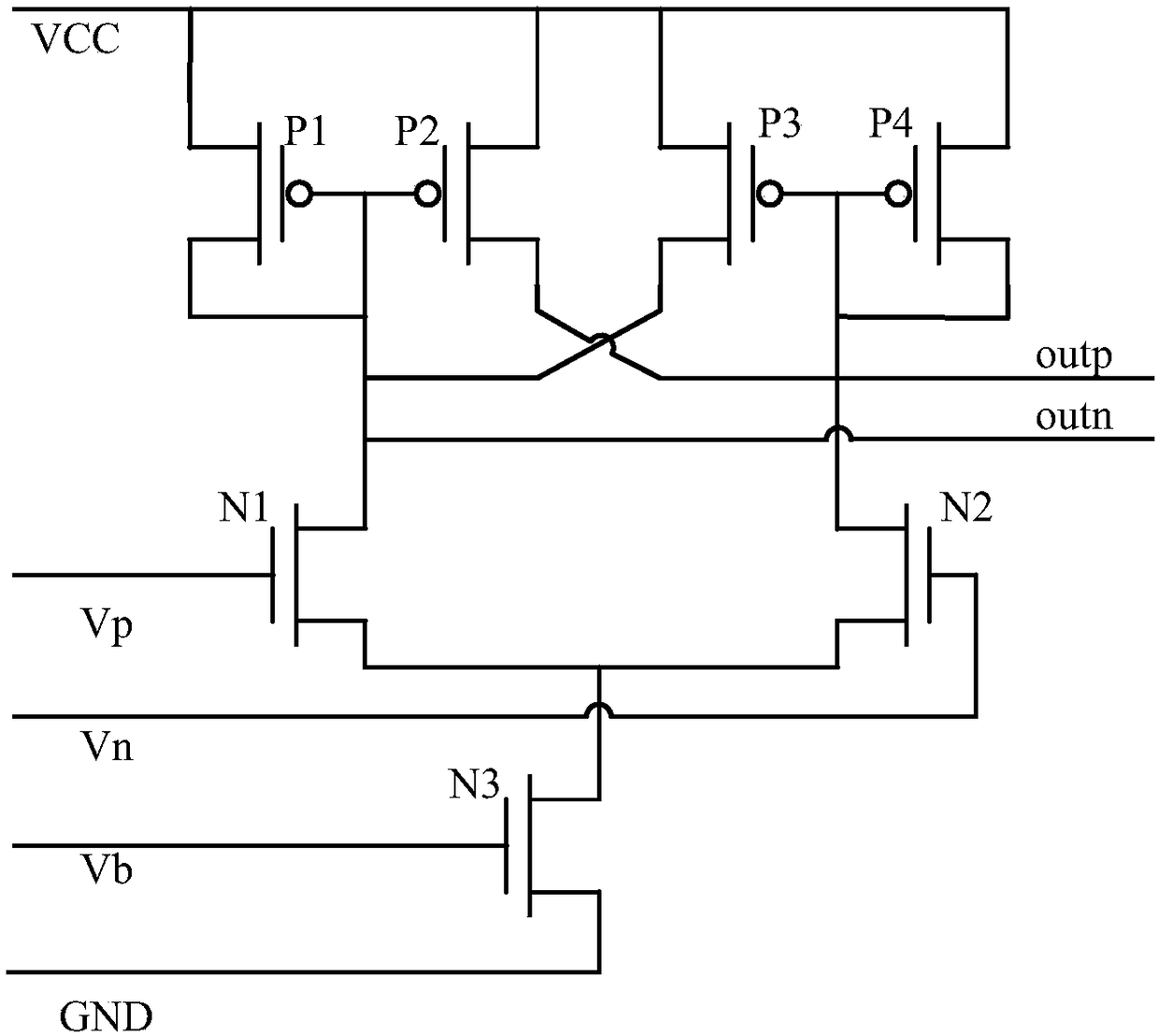

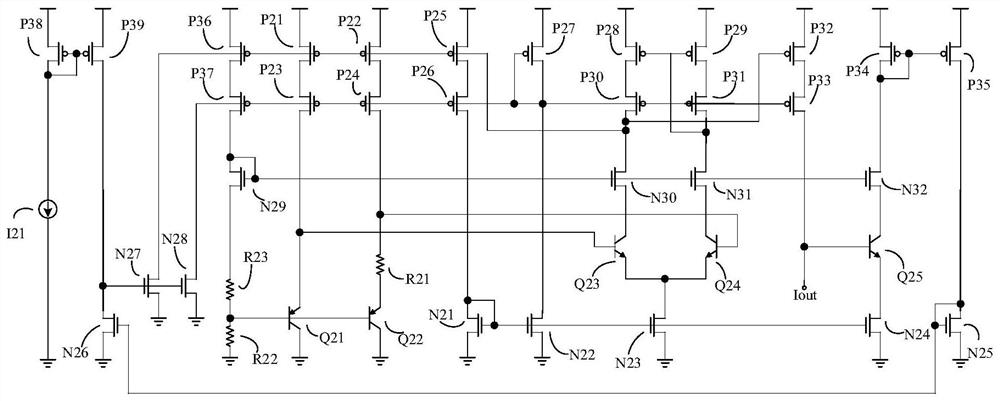

Ultrahigh-speed comparator with low offset

InactiveCN101562441BLower Input Offset VoltageHigh speedAnalogue/digital conversionMultiple input and output pulse circuitsLow offsetAnalog-to-digital converter

The invention provides an ultrahigh-speed comparator with low offset, and belongs to the technical field of composite signal integrated circuits. The comparator comprises a preamplification circuit, adynamic latch circuit and an output latch circuit which hare connected in sequence, wherein, the preamplification circuit comprises a fully differential input structure with a positive resistor and anegative resistor serially connected as load and is used for amplifying difference value between input signals and reference signals; the dynamic latch circuit is equipped with a bistable structure which is connected from head to tail by an inverter, and used for amplifying the output signals of the preamplification circuit and establishing preceding stage output to digital logic output level; and the output latch circuit is composed of two cross-coupled NMOS transistors and PMOS common source amplification input, and used for outputting preceding stage output in a latch time, and keeping output result of the dynamic latch circuit at high impedance state in a reset stage so as to reduce input offset voltage of the comparator, increase speed of the comparator and well meet requirements ofhigh-speed analog-to-digital converter design.

Owner:陕西光电子先导院科技有限公司

Load sensor signal transmitting device

PendingCN111726098AEliminate distractionsImprove stabilityDifferential amplifiersDc-amplifiers with dc-coupled stagesCapacitanceSignal on

The invention discloses a load sensor signal transmitting device in the technical field of sensors. The device comprises an AC filter circuit, a zero setting circuit, a differential voltage amplification circuit and a sampling circuit. The zero setting circuit is connected to the AC filter circuit; andthe differential voltage amplification circuit is connected to the AC filter circuit and the zerosetting circuit. The sampling circuit is connected to the zero setting circuit and the differential voltage amplification circuit. The AC filter circuit comprises a resistor R0, an electromotive force E1, a diode D1, a capacitor C1, a three-terminal regulator U1 and a capacitor C2,one end of the resistor R0 is connected to a +24V power supply, and one end of the diode D1 is connected with the other end of the resistor R0. According to the invention, the interference of noise on a voltage signal on a transmission line can be effectively eliminated, and the signal loss is reduced.

Owner:徐州电子技术研究所水电自动化工程处

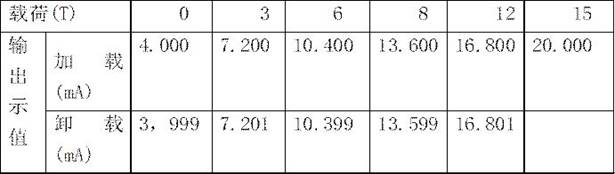

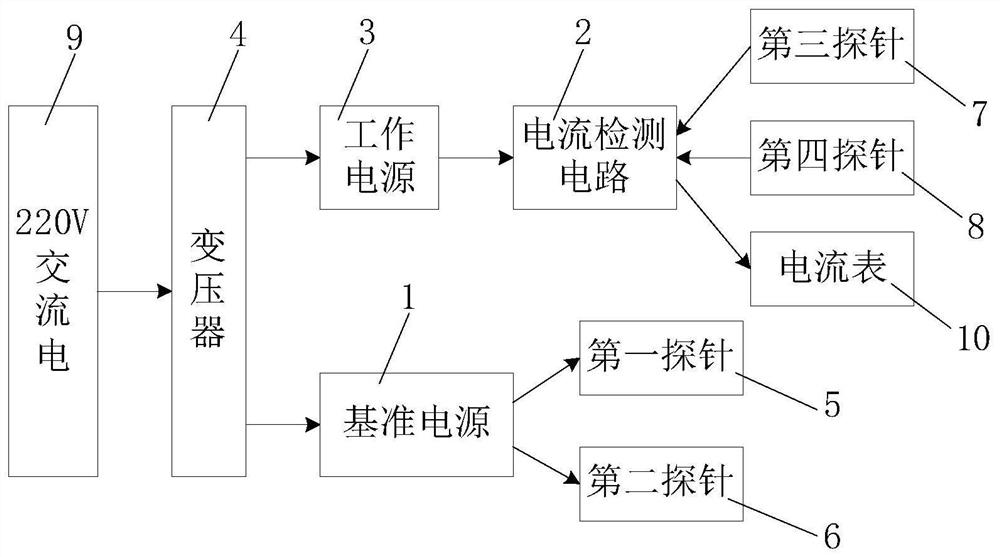

Flaw detection device and application thereof

PendingCN112179948ASimple structureReduce weightMaterial analysis by electric/magnetic meansHemt circuitsEngineering

The invention discloses a flaw detection device and application thereof. The flaw detection device comprises a reference power supply, a current detection circuit, a first probe connected with the positive electrode output end of the reference power supply and a second probe connected with the negative electrode output end of the reference power supply, two input ends of the current detection circuit are respectively connected with a third probe and a fourth probe, and an output end of the current detection circuit is connected with an ampere meter; wherein the reference power supply is used for loading reference voltage to an object to be detected, and the current detection circuit is used for detecting current change on the object to be detected. The device is simple in structure, smallin size, convenient to use and operate, free of missing detection, high in detection precision, wide in application range and high in popularization and application value.

Owner:AECC AVIATION POWER CO LTD