Circuit structure for reducing input offset voltage of two-stage operational amplifier

A technology of operational amplifiers and offset voltages, applied in differential amplifiers, DC-coupled DC amplifiers, etc., can solve the problems of increasing circuit area and circuit complexity, and achieve the goals of reducing input offset voltage, low power consumption, and reducing offsets Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

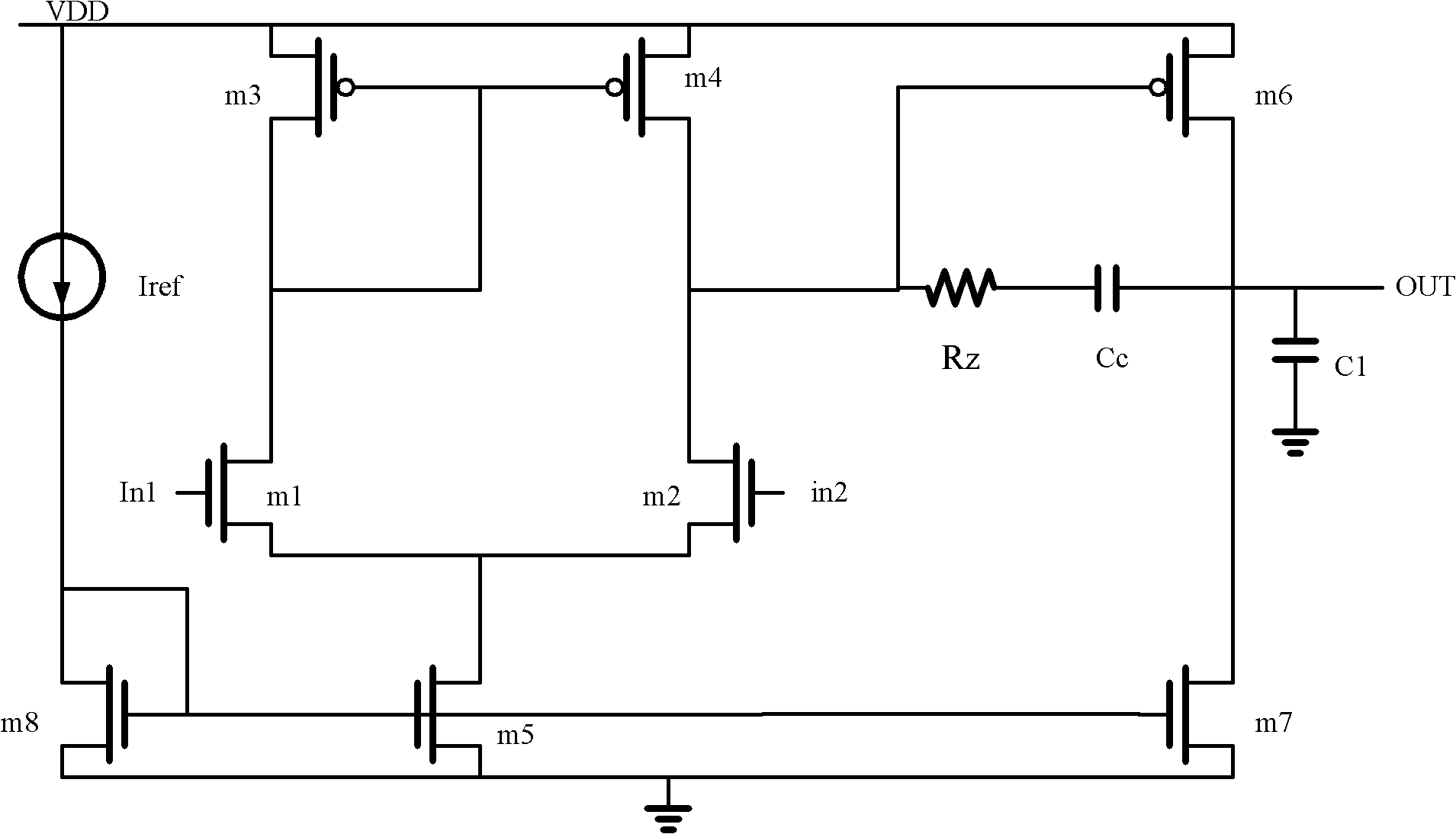

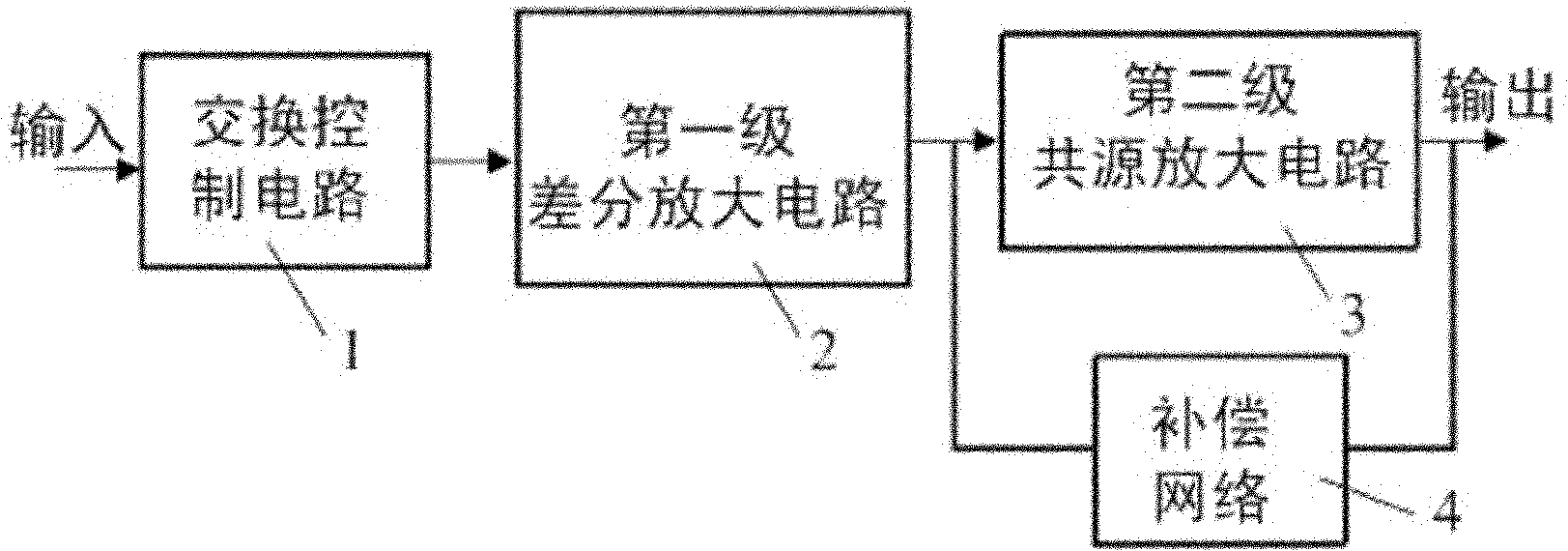

[0018] Such as figure 1 As shown, the traditional two-stage operational amplifier circuit includes a first-stage ordinary differential amplifier circuit, a second-stage common-source amplifier circuit and a compensation network; the first-stage ordinary differential amplifier circuit consists of a first NMOS transistor m1, a second NMOS transistor m2, The third NMOS transistor m5 is composed of the first PMOS transistor m3 and the second PMOS transistor m4. The second-stage common source amplifier circuit is composed of the fourth NMOS transistor m7 and the seventh PMOS transistor m6. The compensation network includes a series zero-suppressing resistor R z and compensation capacitor C c . In addition, the reference current source I ref and the fifth NMOS transistor m8 provide mirror currents for the third NMOS transistor m5 and the fourth ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More