CSP packaging structure of power device and manufacturing method thereof

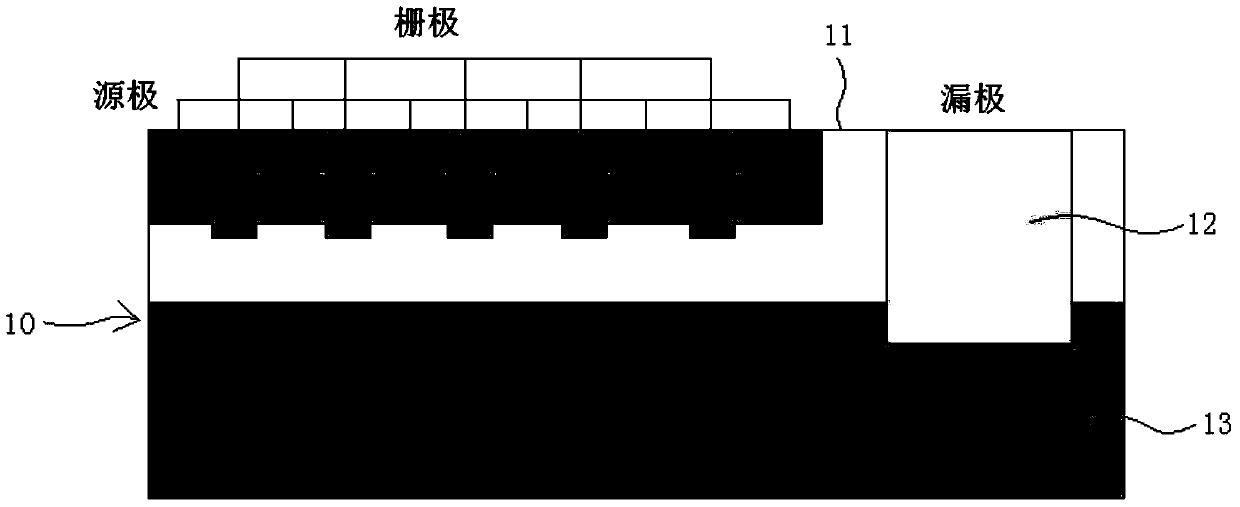

A packaging structure and power device technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of increasing the on-resistance of power devices and reducing the chip utilization area, and achieve the effect of reducing on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the technical means, creative features, objectives and effects achieved by the present invention easy to understand, the present invention will be further described below in conjunction with specific illustrations.

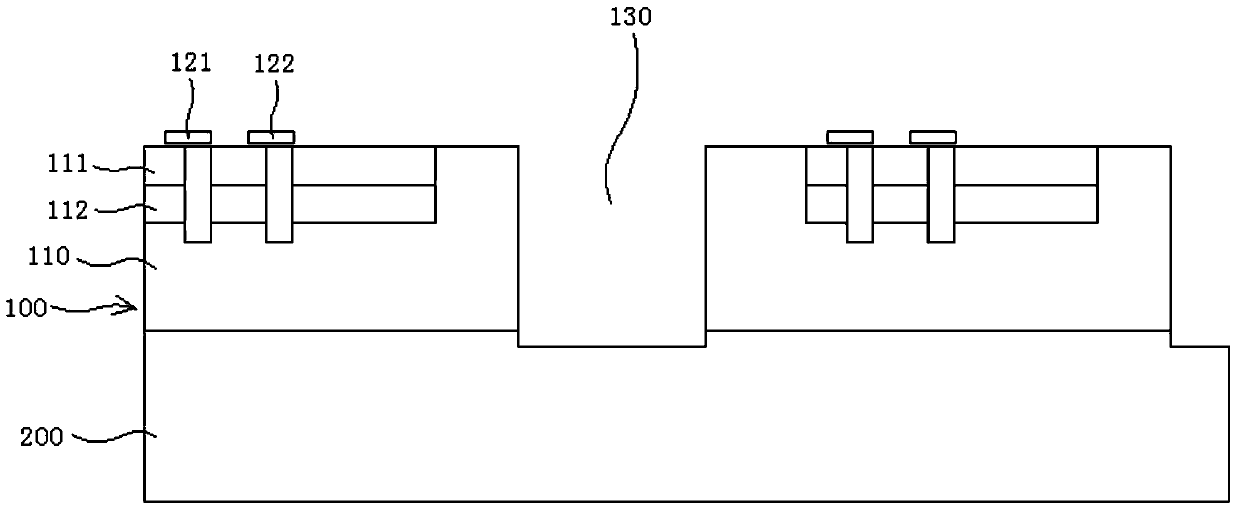

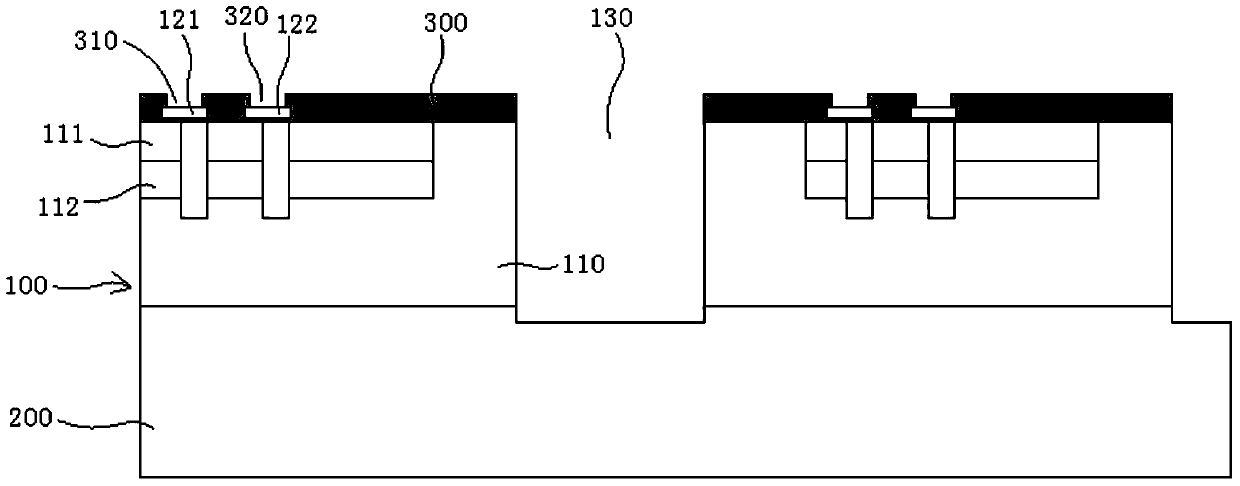

[0031] see Figure 7 , shown in the figure is the CSP packaging structure of the power device, including the chip 100 and the N+ substrate 200 as the drain of the power device arranged on the back of the chip 100, and a number of evenly distributed dies 110 are formed on the front of the chip 100 , each die 110 is provided with an N+ source layer 111 and a P-body layer 112 from top to bottom, and a front surface of each die 110 is provided with an N+ source layer 111 or a P-body layer 112 connected A source bump 121 and a gate bump 122 connected to polysilicon.

[0032] The chip 100 is located between the scribe lane 130 between two adjacent dies 110 and / or the area of the four corners of each die 110 is etched and etched or scribed to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com