Subthreshold level shifter having wide input voltage range

A level shifter and voltage range technology, applied in logic circuits, electrical components, logic circuit connection/interface layout, etc., can solve problems such as large power leakage, long delay time, narrow input level range, etc., and achieve power consumption Low, small power leakage, and the effect of reducing quiescent current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

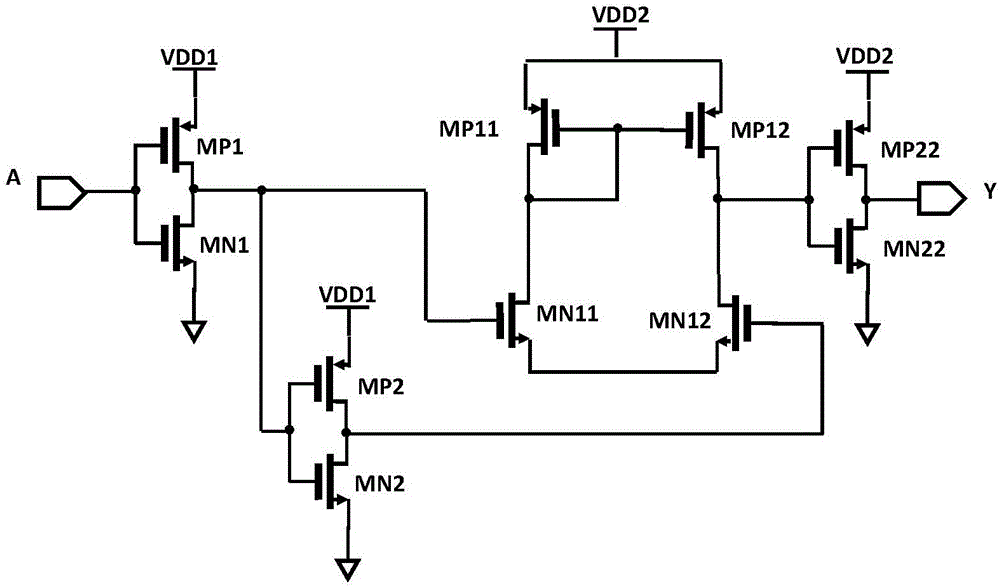

[0027] The structure of the sub-threshold level shifter in Embodiment 1 of the present invention is as follows Figure 4shown, including the Wilson current mirror and inverter. The Wilson current mirror includes three PMOS MP1, MP2, MP3 and two NMOS MN1, MN2. The sources of PMOS MP1 and PMOS MP2 are connected to a high power supply voltage VDDH. The drain of PMOS MP1 is connected to the source of PMOS MP3, the drain of PMOS MP3 is connected to the drain of NMOS MN1, and the source of NMOS MN1 is grounded. The drain of the PMOS MP2 is connected to the drain of the NMOS MN2, and the source of the NMOS MN2 is grounded. The gates of PMOS MP1 and PMOS MP2 are connected to the drain of PMOS MP1, and the gate of PMOS MP3 is connected to the drain of PMOS MP2.

[0028] The power input terminal of the inverter is connected to the low power supply voltage VDDL, the input terminal of the inverter is connected to the input level IN, and the output terminal of the inverter outputs the l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More