a snubber circuit

A buffer circuit and pulse circuit technology, which is applied in the direction of logic circuit, logic circuit connection/interface layout, pulse technology, etc., can solve the problems of slow loop response speed and small bandwidth of traditional buffer circuits, and improve the loop response speed , the effect of large bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

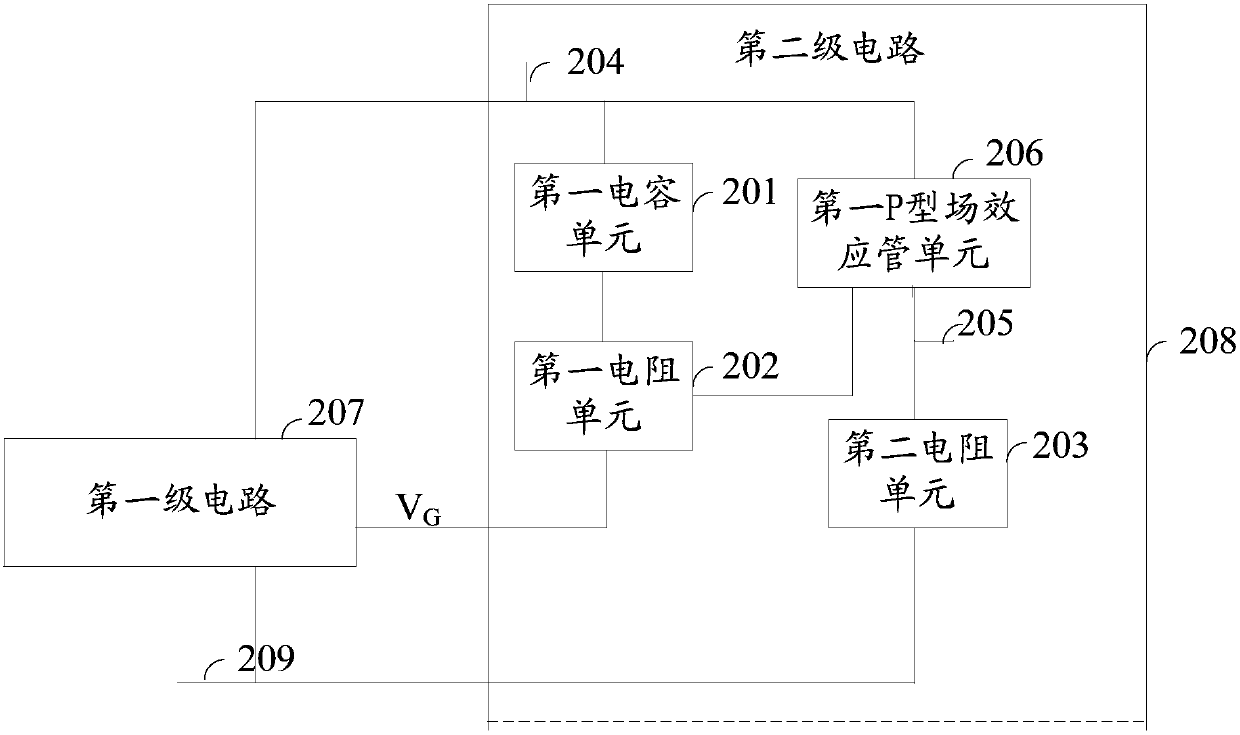

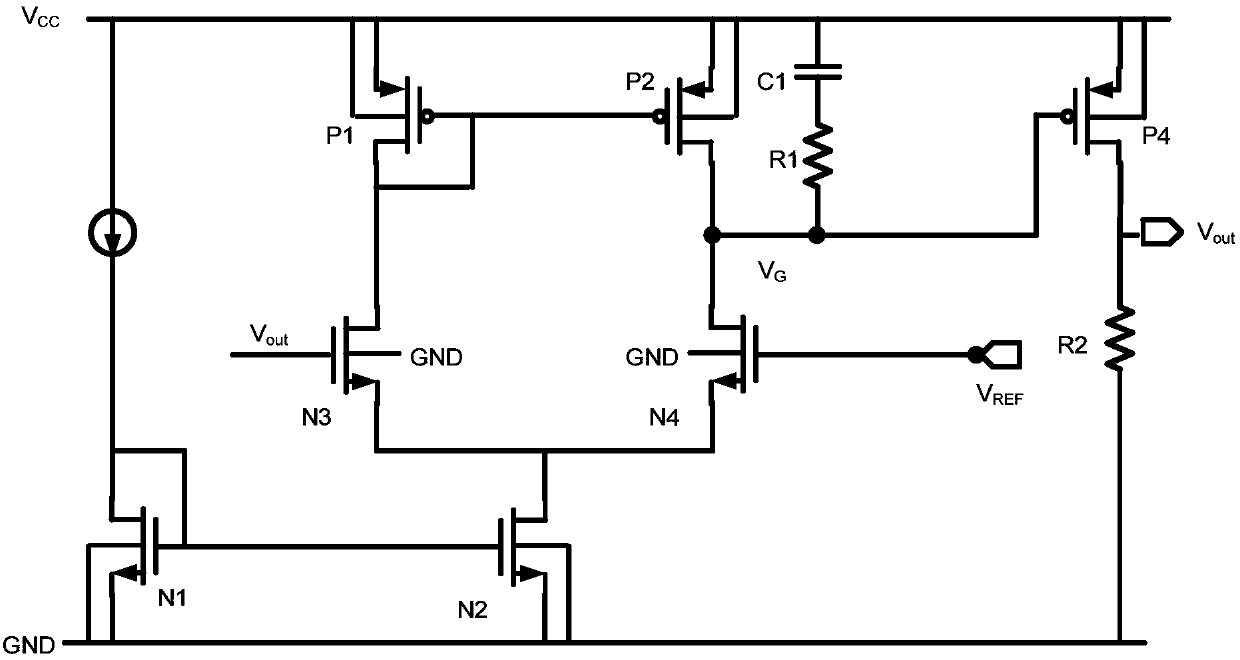

[0027] refer to figure 2 , shows a schematic structural diagram of Embodiment 1 of a buffer circuit of the present invention, the buffer circuit may specifically include a first-stage circuit 207 and a second-stage circuit 208; wherein, the second-stage circuit 208 may specifically include: A capacitance unit 201, a first resistance unit 202, a second resistance unit 203, an input terminal 204, an output signal terminal 205, and a first P-type field effect transistor unit 206; wherein, one end of the first capacitance unit 201 is connected to the Input terminal 204, the other end is connected to one end of the first resistance unit 202; the other end of the first resistance unit 202 is respectively connected to the output terminal V of the first stage circuit G , the gate of the first P-type field effect transistor unit 206; the source of the first P-type field effect transistor unit 206 is connected to the input terminal 204, and the drain is connected to the output signal t...

Embodiment 2

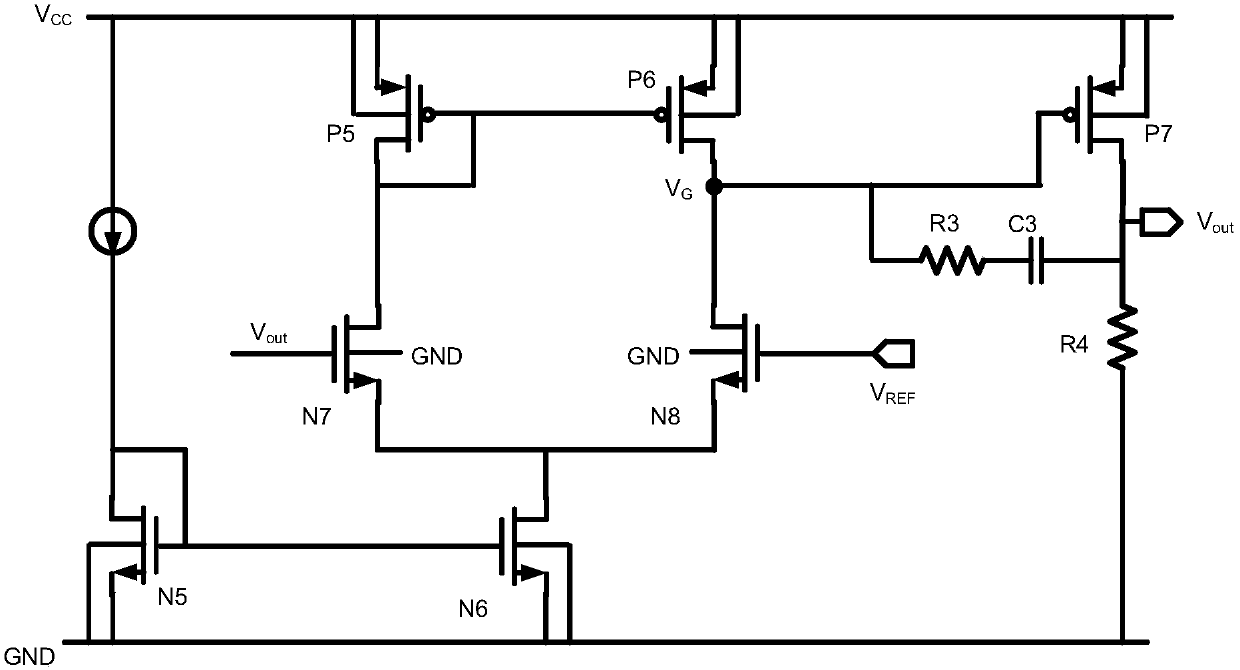

[0036] refer to Figure 4 , shows a schematic structural diagram of a buffer circuit embodiment 2 of the present invention, the buffer circuit may specifically include a first-stage circuit and a second-stage circuit; wherein, the second-stage circuit includes: a first capacitor unit 401 , the first resistance unit 402, the second resistance unit 403, the input terminal 404, the output signal terminal 405, the first P-type field effect tube unit 406, the pulse circuit unit 407, the second P-type field effect tube unit 408, and the second capacitance Unit 409, an input signal terminal 410; wherein, one end of the first capacitor unit 401 is connected to the input terminal 404, and the other end is connected to one end of the first resistance unit 402; the other ends of the first resistance unit 402 are respectively Connect the output terminal VG of the first stage circuit and the first P-type field effect transistor unit 406; the first P-type field effect transistor unit 406 is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More