Digital timer topological structure and control method thereof

A topology and timer technology, applied in instruments, analog-to-digital conversion, signal transmission systems, etc., can solve the problem of inability to meet the large-scale requirements of accelerometers, affecting the application field of I/F conversion circuits, and inability to design I/F circuits Need to adjust and other issues to achieve the effect of reducing power, improving loop response speed, and increasing range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

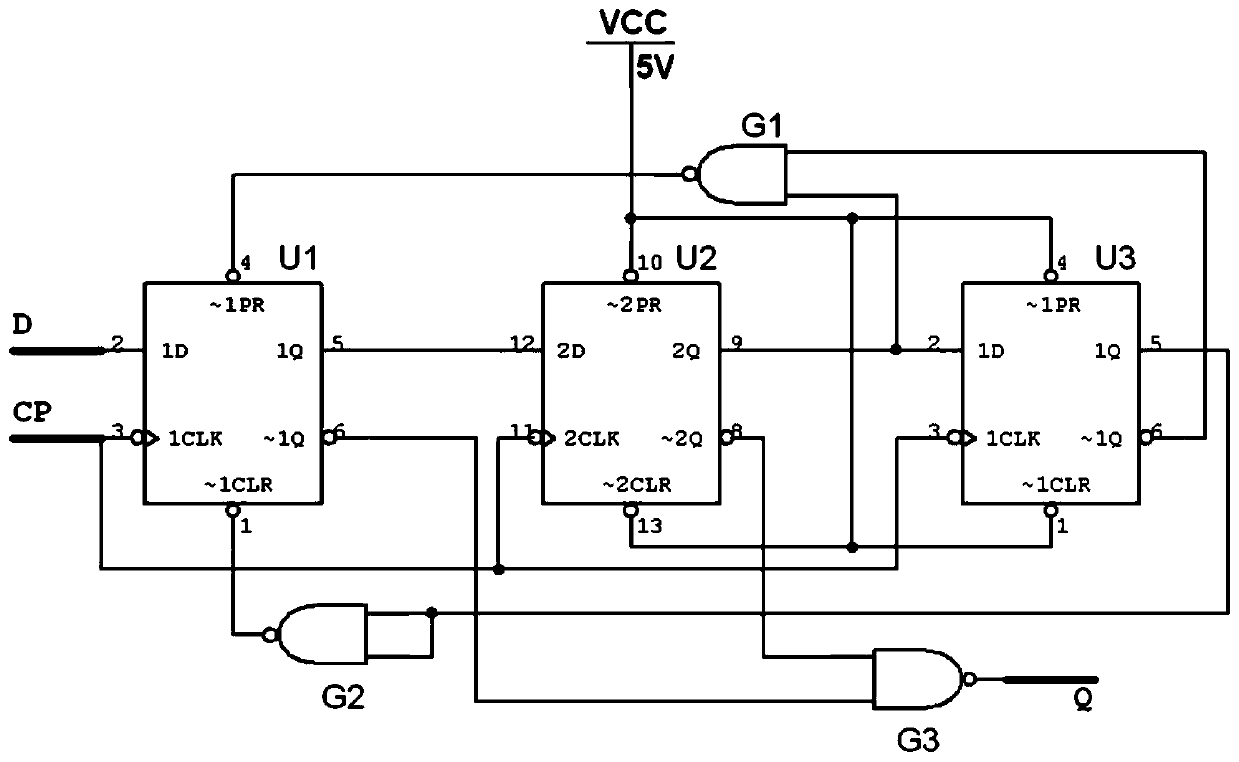

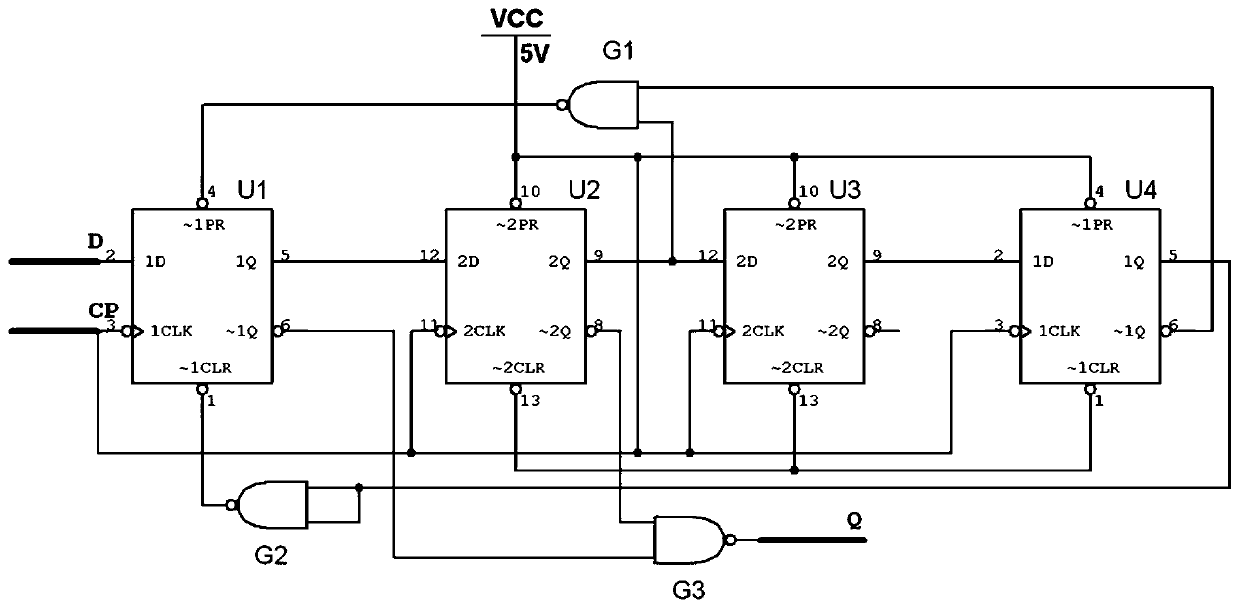

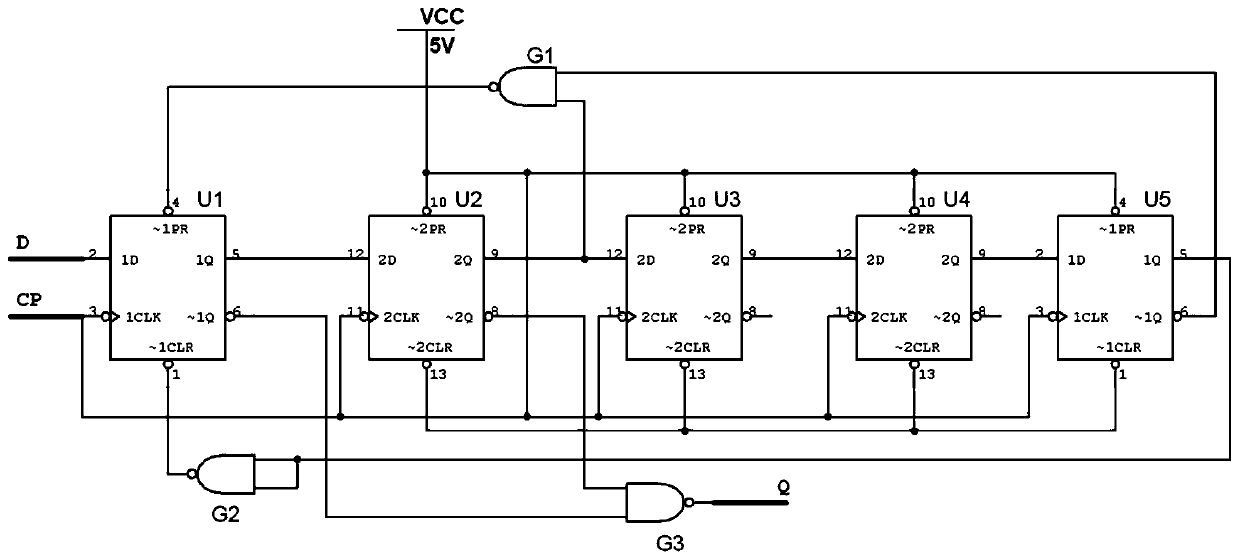

[0031] In order to more clearly illustrate the technical solutions in the embodiments of the present invention, the drawings that need to be used in the description of the embodiments will be briefly introduced below. Obviously, the drawings in the following description are only some embodiments of the present invention. For those skilled in the art, other drawings can also be obtained based on these drawings without creative effort.

[0032] In order to make the object, technical solution and advantages of the present invention more clear, the specific implementation of the present invention will be further described below in conjunction with the drawings and embodiments, which are explanations of the present invention rather than limitations.

[0033] Such as Figure 1 to Figure 5 As shown, a digital timer topology of the present invention includes a plurality of D flip-flops Un, NAND gate G1, NAND gate G2 and NAND gate G3;

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More