A reusable verification system for eda and fpga for passive tag chips

A verification system and passive tag technology, which is applied in the direction of instruments, error detection/correction, calculation, etc., can solve problems such as non-compliance with standard requirements, lagging behind in the development progress of label development, and difficulty in being found by verification engineers, so as to avoid large-scale risk effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] All features disclosed in this specification, or steps in all methods or processes disclosed, may be combined in any manner, except for mutually exclusive features and / or steps.

[0041] Any feature disclosed in this specification (including any appended claims, abstract and drawings), unless expressly stated otherwise, may be replaced by alternative features which are equivalent or serve a similar purpose. That is, unless expressly stated otherwise, each feature is one example only of a series of equivalent or similar features.

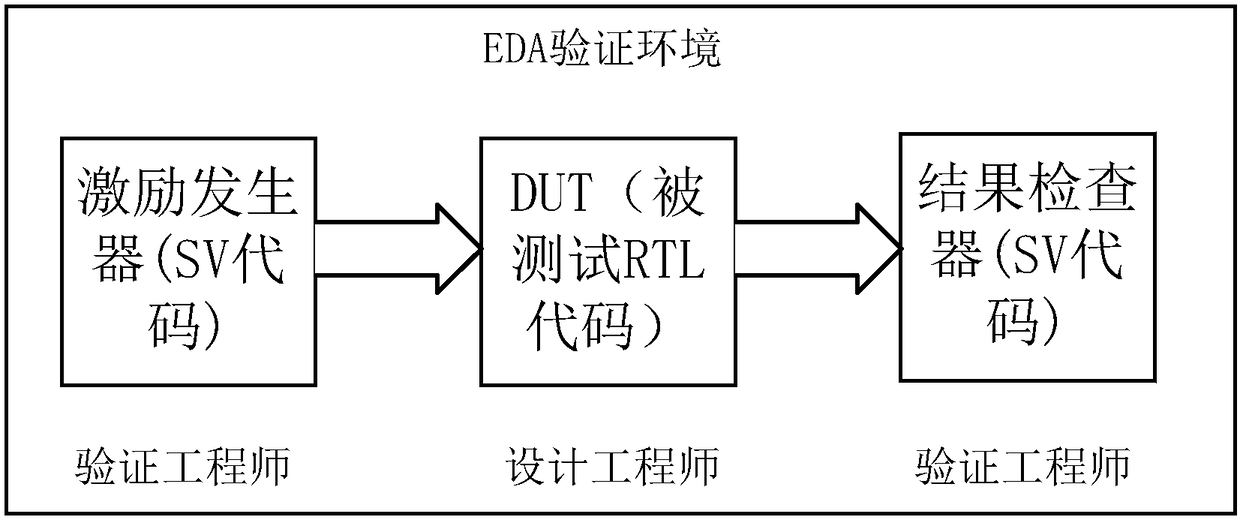

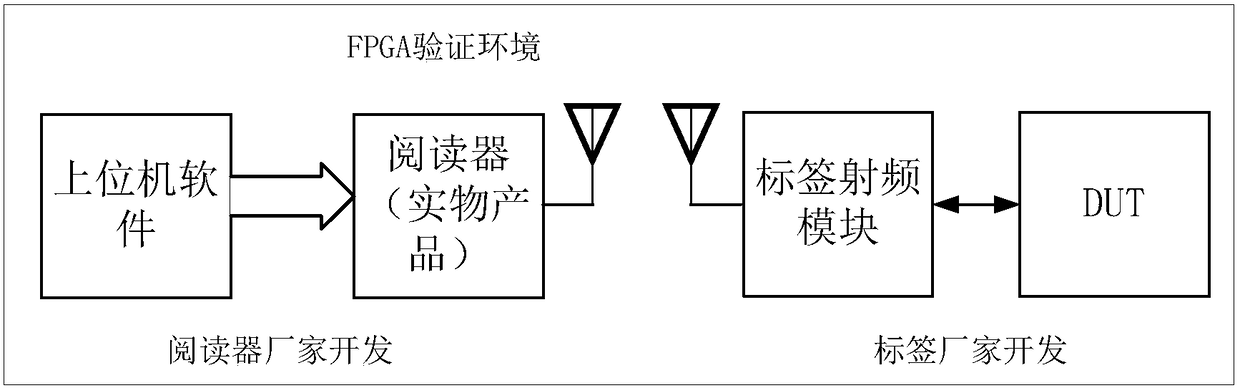

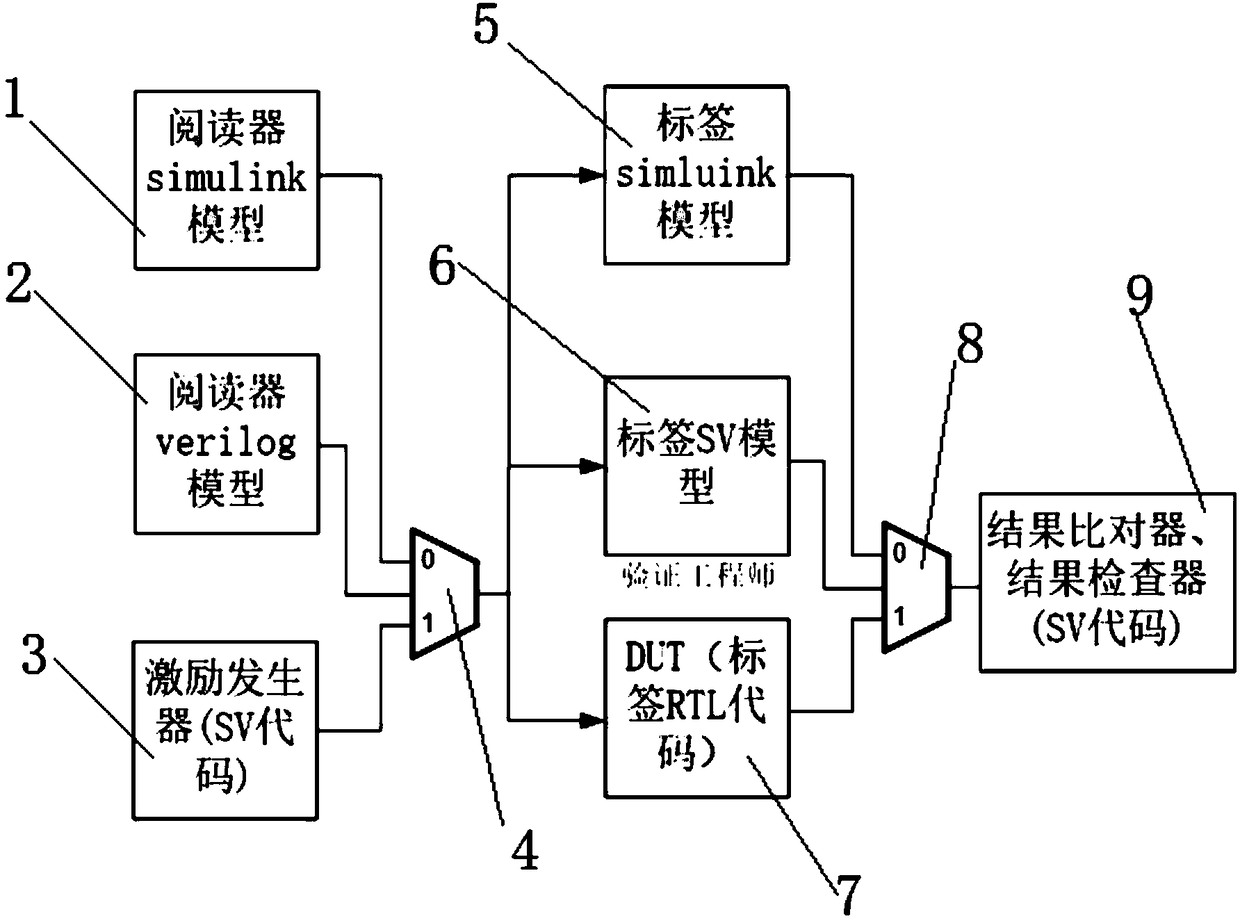

[0042] Such as image 3 and 5 As shown, an EDA and FPGA reusable verification system for passive tag chips: including EDA environment verification system and FPGA environment verification system;

[0043] Reader simulink model 1 in the described EDA environment verification system, reader verilog model 2 and excitation generator 3 are connected with the input end of selection controller-4, and the output end of selection controller 4 is conn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More