Memory physical layer interface logic for generating dynamic random access memory (dram) commands with programmable latency

A physical layer interface, memory technology, applied in the field of processing systems, can solve problems such as change

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

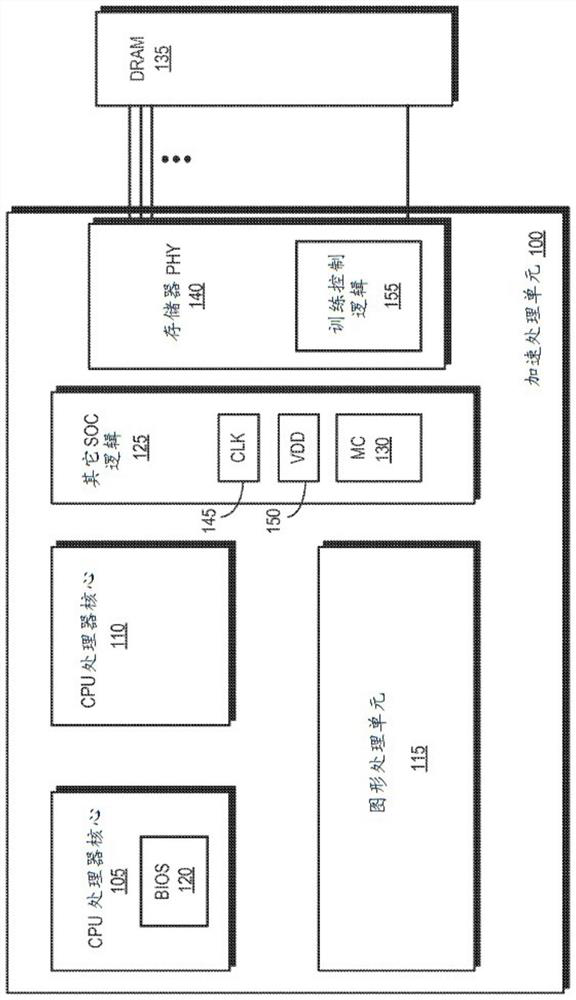

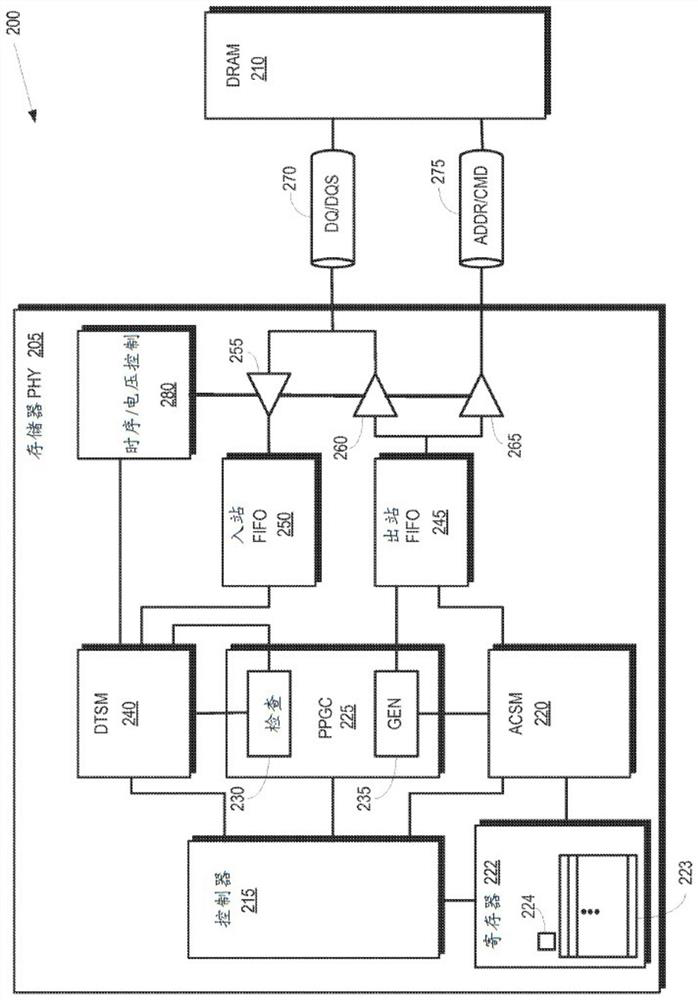

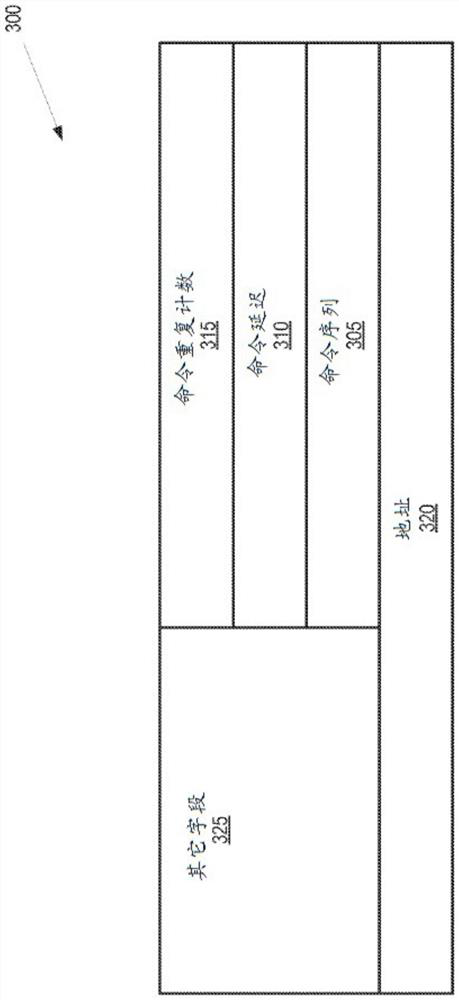

[0015] A conventional training sequence uses a predetermined sequence of commands separated by predetermined delay intervals. Therefore, conventional training sequences (for example) cannot be modified to account for different timing requirements of different DRAM designs. However, as discussed herein, the delay time interval between commands issued to the DRAM may be different for different types of commands, and the delay time interval may also be different for different types of DRAM, and may change when new DRAM designs are introduced. To account for the timing requirements of different memory PHYs or DRAM designs, training sequences can be flexibly defined by a programmable training engine implemented in the memory PHY. The training engine may be programmed using an instruction word comprising a first field for indicating a command and a second field for indicating a delay time interval to elapse before executing the command. Some implementations of the instruction word ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com