Behavior level modeling and verification method of power amplifier underlying circuit

A verification method and circuit model technology, applied in CAD circuit design, electrical digital data processing, special data processing applications, etc., can solve complex problems such as power amplifier bottom circuit simulation solution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

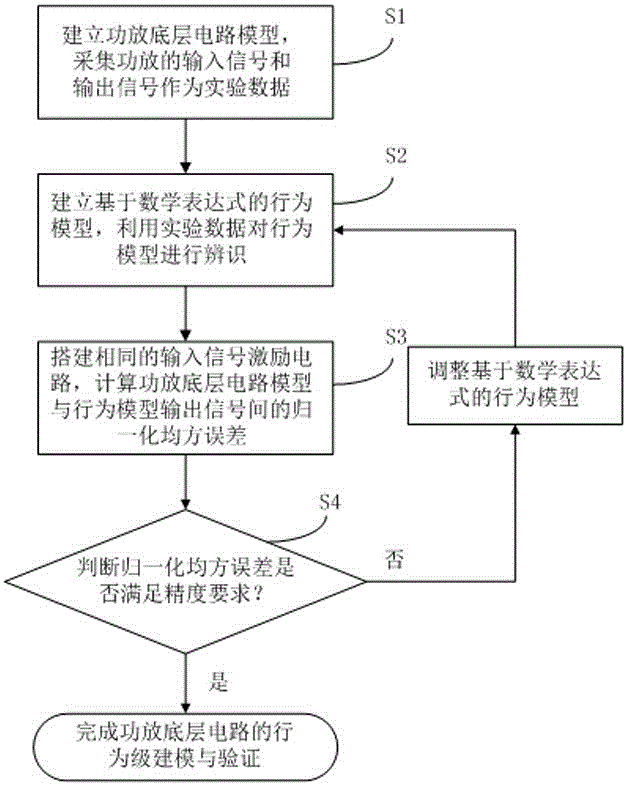

[0031] The following combination Figure 1 ~ Figure 3 , a preferred embodiment of the present invention is described in detail.

[0032] Such as figure 1 As shown, the behavior-level modeling and verification method for the bottom circuit of the power amplifier provided by the present invention includes the following steps:

[0033] S1. Establish the bottom circuit model of the power amplifier, and collect the input signal and output signal of the power amplifier as experimental data;

[0034] S2. Establish a behavior model based on mathematical expressions, and use the experimental data of input signals and output signals collected in S1 to identify the behavior model;

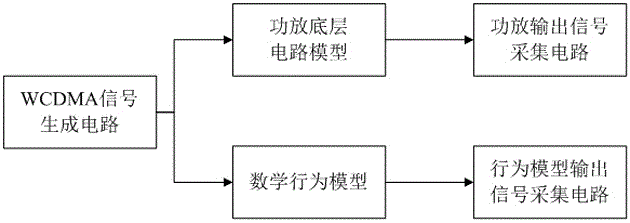

[0035] S3. Build the same input signal excitation circuit, and calculate the normalized mean square error between the bottom circuit model of the power amplifier and the output signal of the behavior model;

[0036] S4. Determine whether the normalized mean square error meets the accuracy requirements, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More