Chip package structure and manufacturing method thereof

A technology of chip packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problem of increasing the inner pin pitch, unable to increase the contact density of the chip packaging structure, and unable to achieve micro-pitch, etc. problem, to achieve the effect of increasing the contact density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

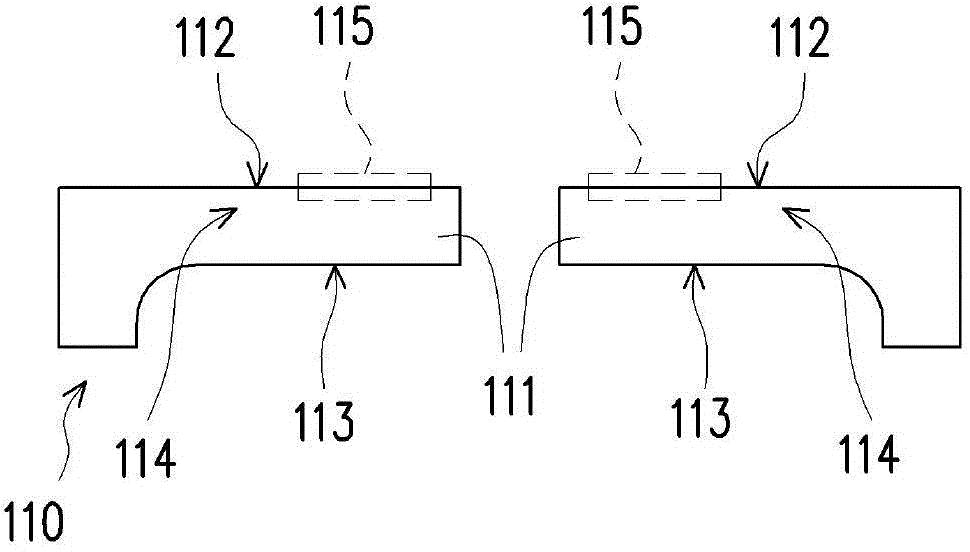

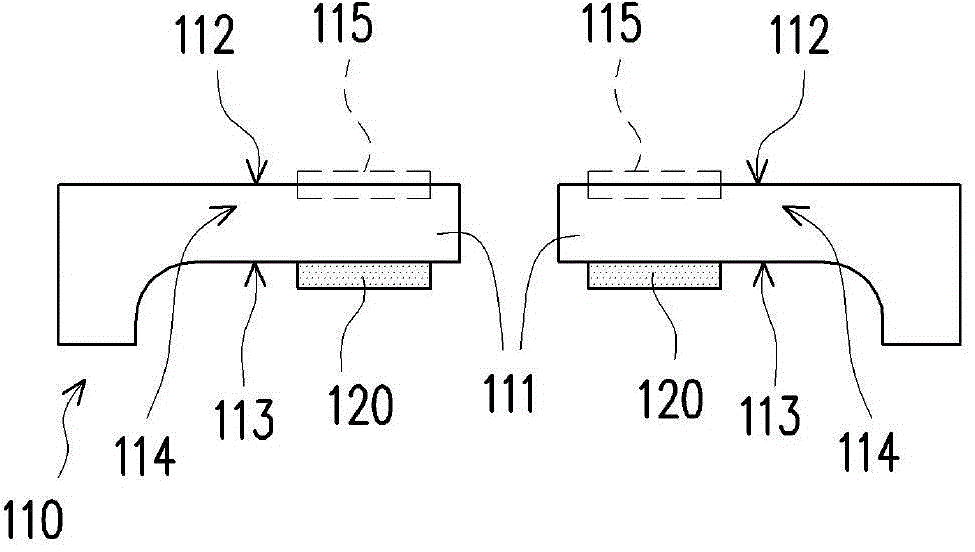

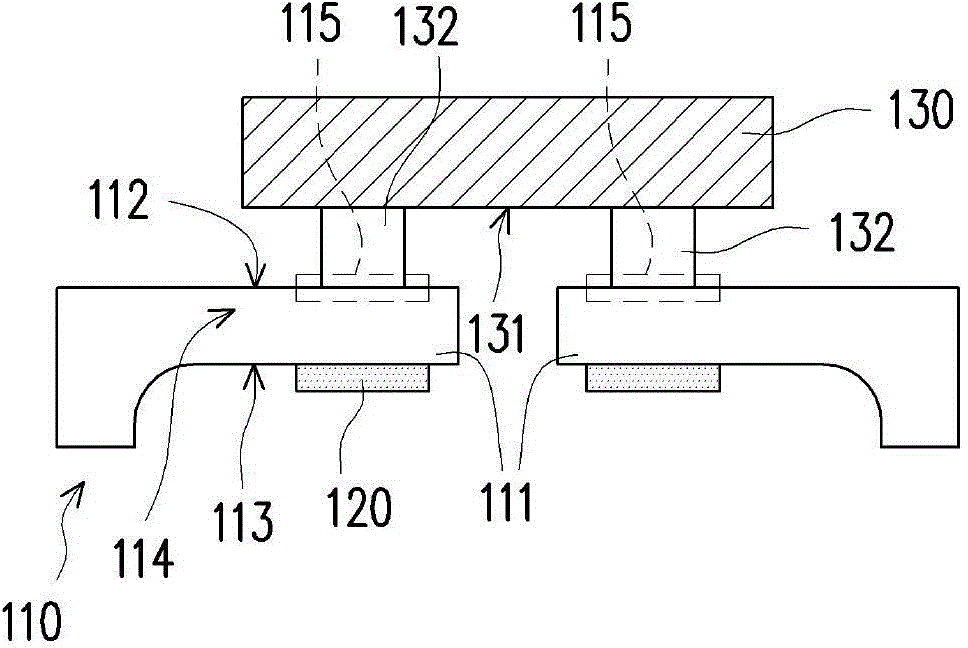

[0046] Figure 1A to Figure 1E It is a schematic diagram of the manufacturing process of the chip packaging structure according to an embodiment of the present invention. Figure 1F for Figure 1E A partial cross-sectional schematic diagram of the chip package structure along the section line A-A. First, please refer to Figure 1A , providing a lead frame 110 as a carrier. The lead frame 110 has a plurality of inner pins 111, wherein each inner pin 111 has an upper surface 112, a lower surface 113 opposite to the upper surface 112, and opposite side surfaces 114 connecting the upper surface 112 and the lower surface 113 (shown in Figure 1F ) and the bonding area 115 on the upper surface 112.

[0047] Next, please refer to Figure 1B A solder resist layer 120 is formed on the lower surface 113 of each inner lead 111 and at least corresponds to the bonding area 115 of each inner lead 111 . Specifically, the solder resist layer 120 is, for example, formed on the lower surfa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More