Integrated circuits with embedded double-clocked components

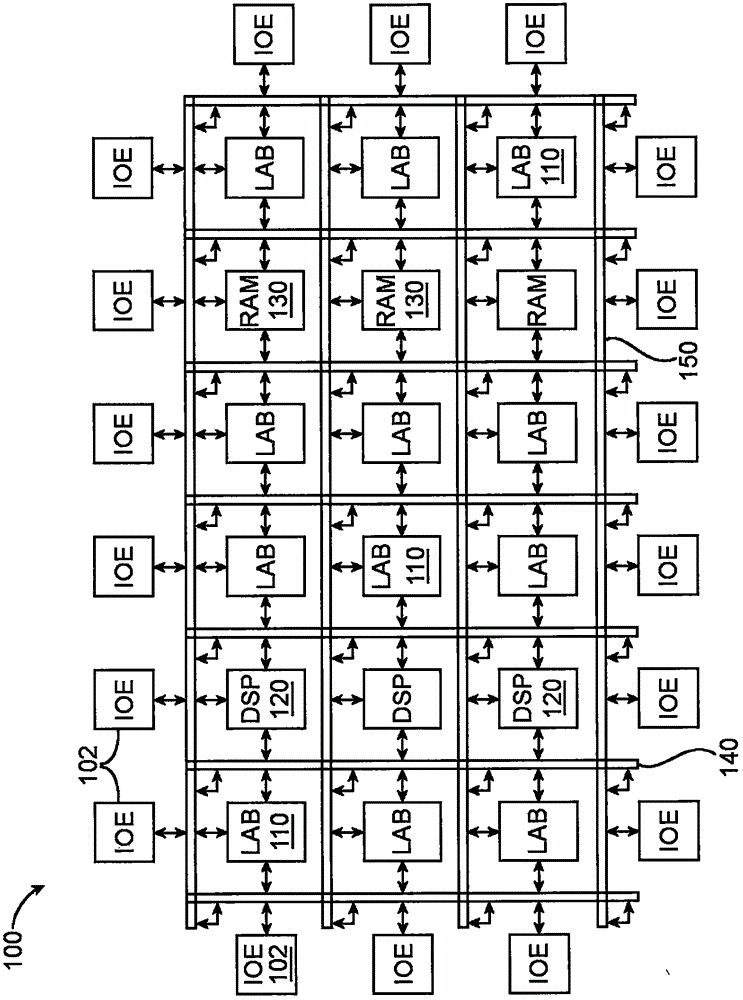

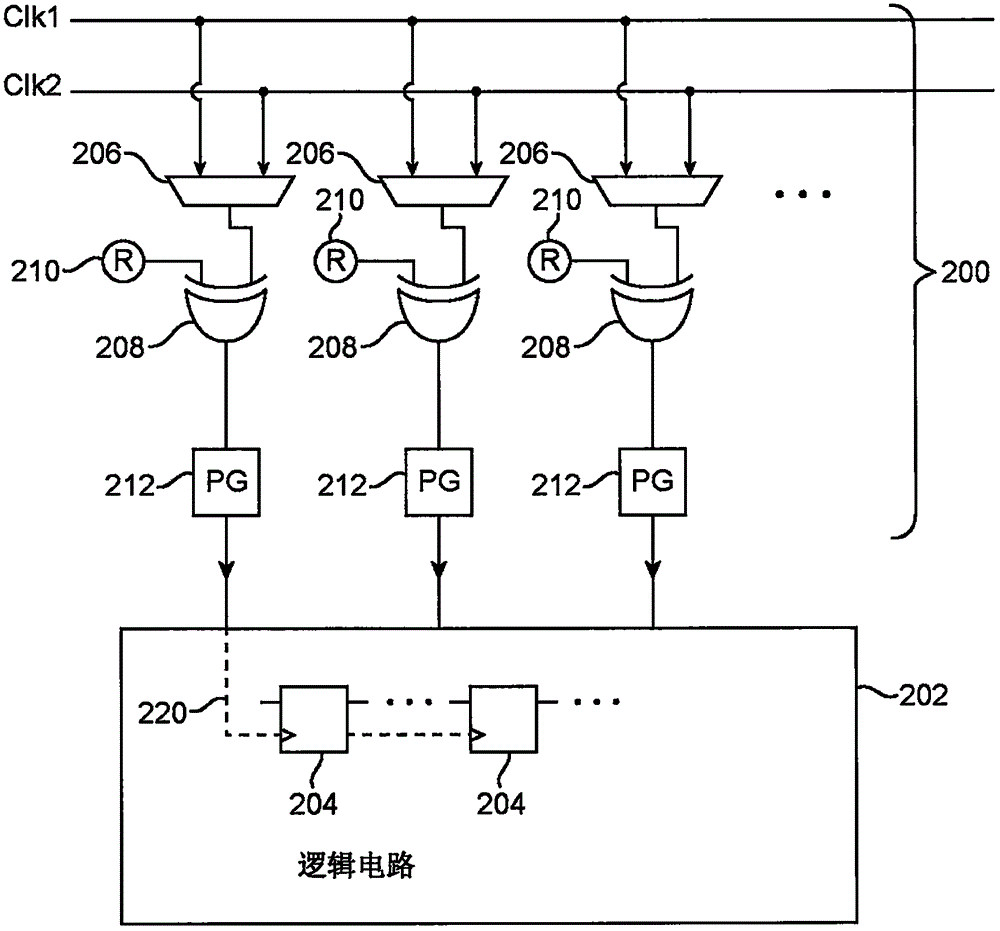

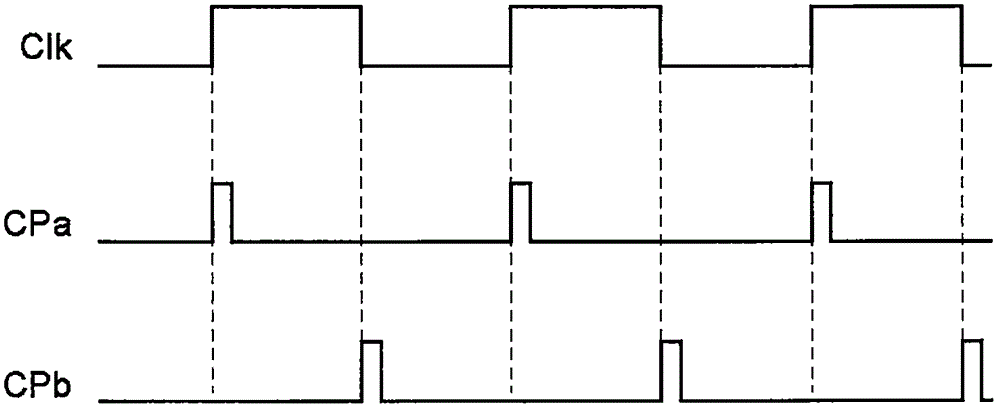

A clock generation circuit, integrated circuit technology, applied in the direction of logic circuits, electrical components, generation/distribution of signals, etc., can solve problems such as expensive, reduced performance gain, huge routing pressure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0080] Additional Embodiments 1. An integrated circuit comprising: a first functional block operating at a first data rate; a second functional block operating at a data rate greater than the first data rate; a second data rate operation at a rate; and a data rate concentrating circuit that receives stored data from the first functional block at the first data rate and converts the stored data at the second data rate The stored data is output to the second functional block.

Embodiment 2

[0081] Additional embodiment 2. The integrated circuit of additional embodiment 1, wherein the second data rate is twice the first data rate.

Embodiment 3

[0082] Additional embodiment 3. The integrated circuit of additional embodiment 1, wherein said first functional block is physically adjacent to said second functional block on said integrated circuit.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com