Method and router for processing packets in network on chip

An on-chip network and router technology, applied in the computer field, can solve problems such as long branch jump spans, performance impact, and lack of instruction caches, and achieve the effects of reducing network access overhead, improving overall performance, and reducing memory access delays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

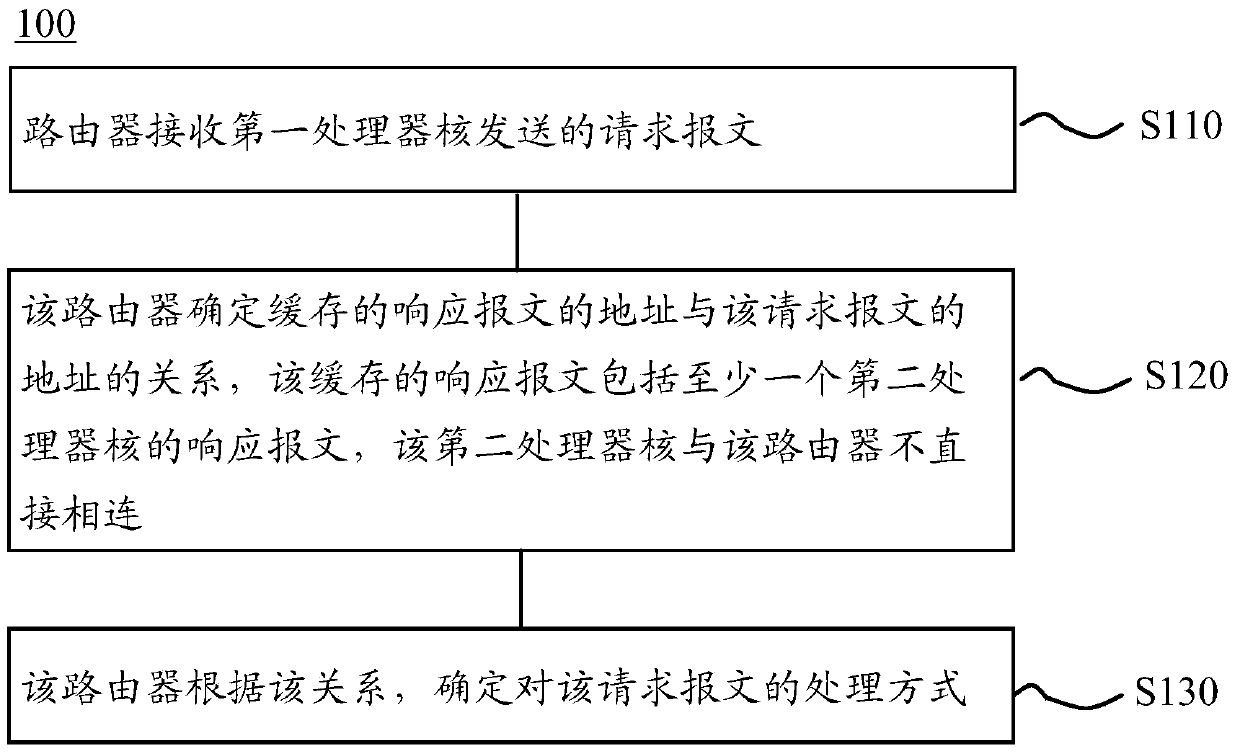

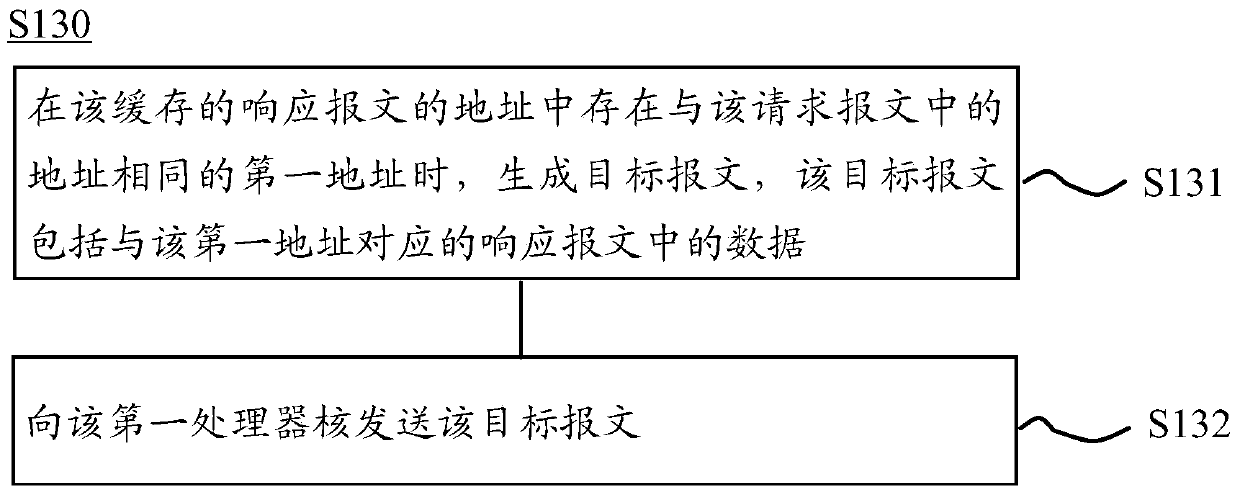

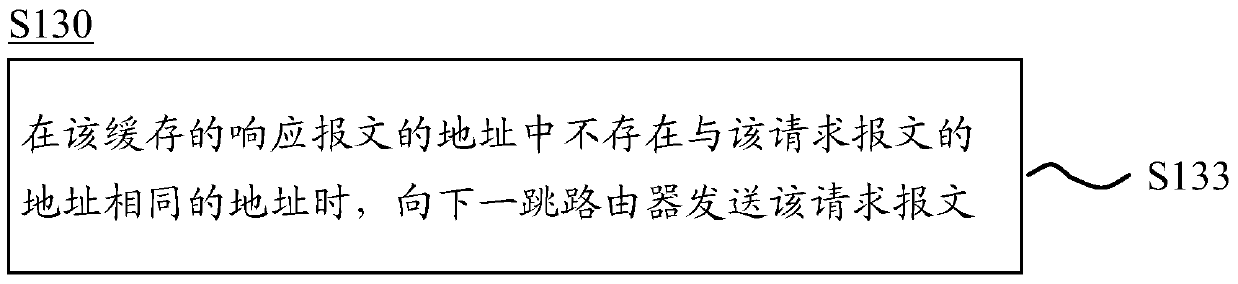

[0040] figure 1 A schematic flowchart of a method for processing packets in a network on chip according to an embodiment of the present invention is shown. The method 100 can be performed by a router in a network on chip, such as figure 1 As shown, the method 100 includes:

[0041] S110. The router receives the request message sent by the first processor core;

[0042] S120, the router determines the relationship between the address of the cach...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More