Unified Bit Width Conversion Method for Cache and Bus Interface in System Chip

A bus interface and bit-width conversion technology, applied in memory systems, memory address/allocation/relocation, instruments, etc., can solve undiscovered problems, achieve the effect of clear design structure, localized modification scope, and guaranteed consistency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be further described in detail below in conjunction with the accompanying drawings, which are explanations rather than limitations of the present invention.

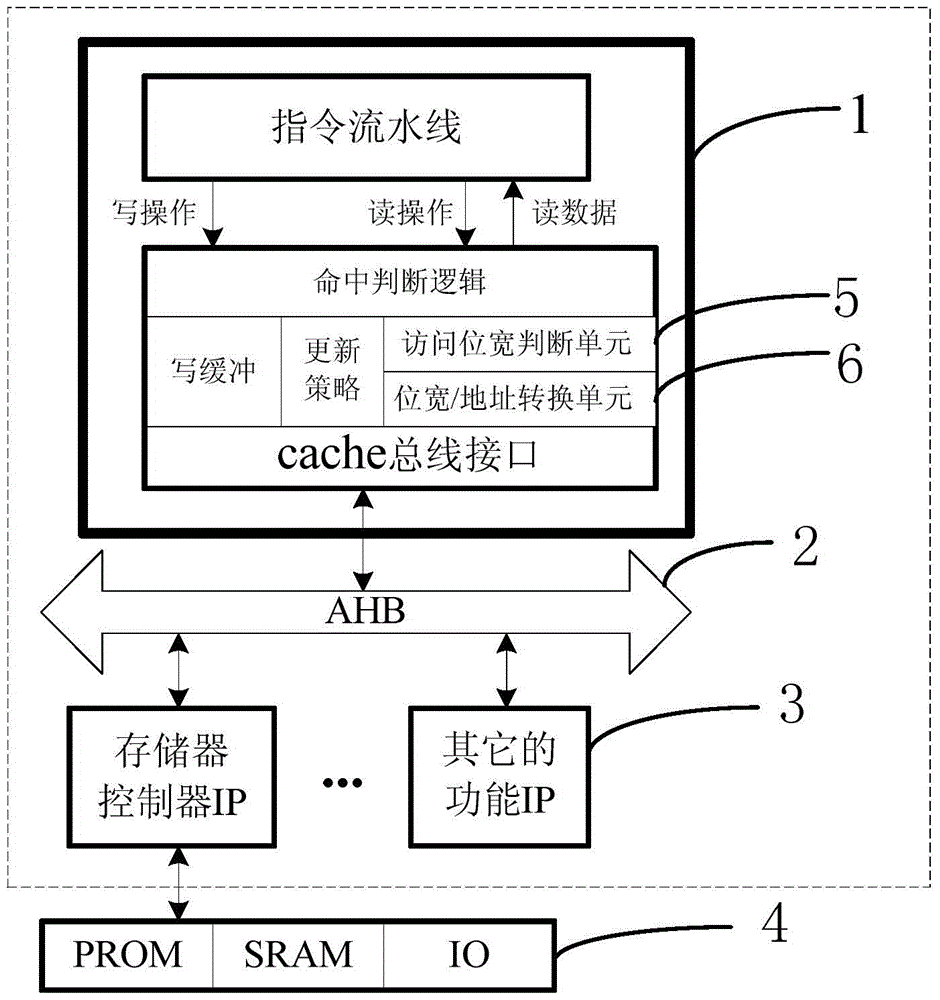

[0033] see figure 1 , the unified bit width conversion structure of the cache and the bus interface in the system chip of the present invention includes a processor core 1 and a plurality of IP cores 3 that perform data interaction with the processor core 1 through the on-chip bus 2, wherein the memory controller IP and the off-chip The main memory 4 is connected; the processor core 1 includes an instruction pipeline and a hit judgment logic unit capable of receiving instruction pipeline read / write operation instructions, and an access bit width judgment unit 5 and a bit width / bit width judgment unit 5 are arranged between the hit judgment logic unit and the cache bus interface. The address conversion unit 6 and the hit judgment logic unit can send the judgment result data to the instruc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More