Single event upset-resistant satellite-borne data processing system and method

An on-board data and anti-single particle technology, applied in aerospace electronics integration and aviation fields, can solve the problems of difficult software upgrade and maintenance, small memory capacity, and inability to maintain on-orbit, so as to improve the ability to resist single-event overturn, storage The effect of large capacity and reduced requirements for hardware circuit design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0065] The present invention is described in further detail now in conjunction with accompanying drawing.

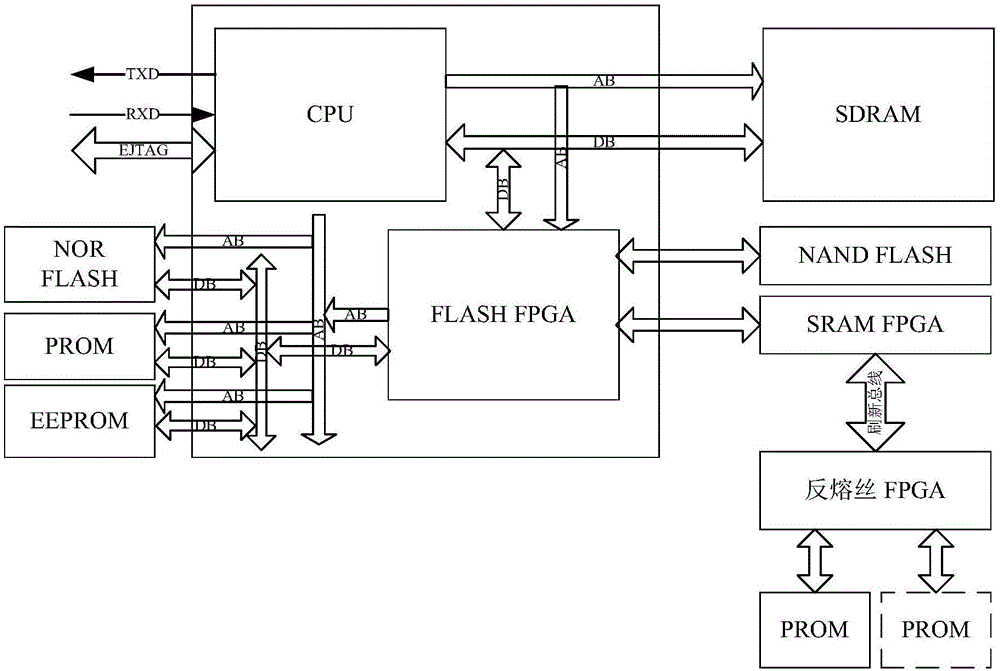

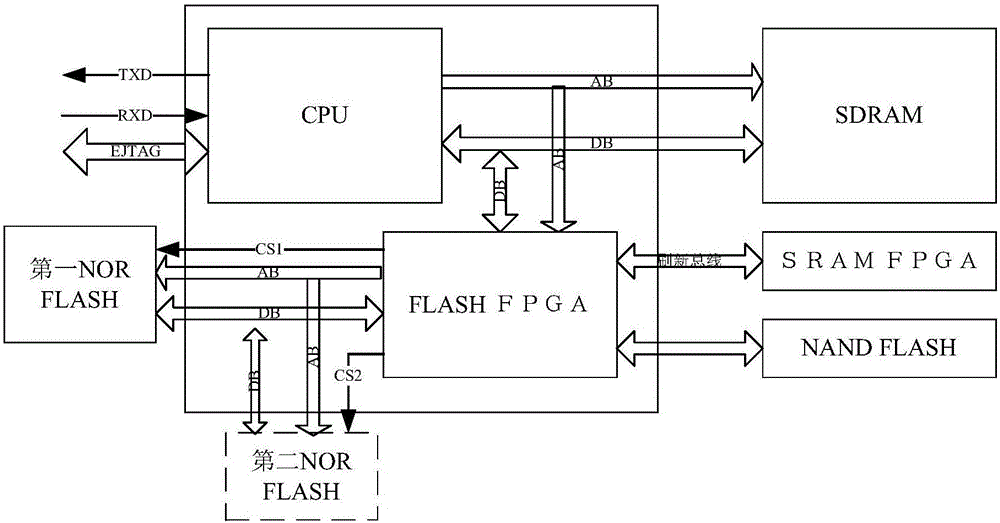

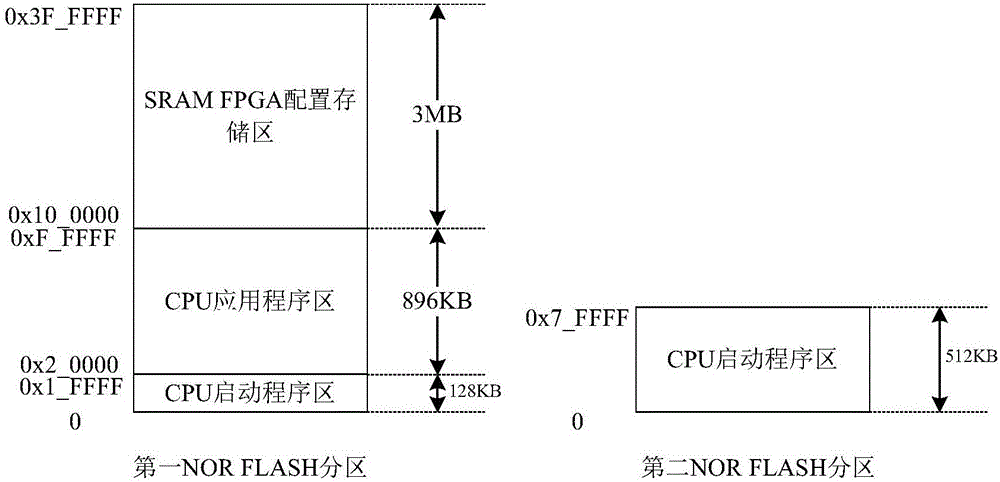

[0066] Such as figure 2 Shown, a kind of on-board data processing system of anti-single-event upset, said system comprises: CPU, FLASHFPGA, SDRAM, first NOR FLASH, SRAM FPGA, NAND FLASH and second NOR FLASH; Wherein, described CPU The data, address and control buses are connected to the FLASH FPGA and the SDRAM, and the said FLASH FPGA is connected to the first NOR FLASH, the SRAM FPGA, the NAND FLASH and the second NOR FLASH.

[0067] The EMI module of the CPU has an ECC codec function, and the CPUs commonly used in aerospace are AT697 and Loongson LS1E. The interface between the CPU and the outside includes two asynchronous serial ports TXD, RXD and EJTAG.

[0068] The FLASH FPGA is used for CPU software guidance, SRAM FPGA configuration and refresh, and NAND FLASH control. In order to eliminate the single event flip effect of space radiation, all logic of the FLASH...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More