Method for outputting peripheral through dual core sharing of Zynq chip in asymmetric multi-processing mode

A multi-processing and chip technology, applied in the direction of electrical digital data processing, multi-channel program device, program control design, etc., can solve problems such as loss, data processing efficiency reduction, etc., to simplify scheduling, reduce system complexity, and improve system reliability sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solution of the present invention will be further introduced in detail below in conjunction with the accompanying drawings of the description.

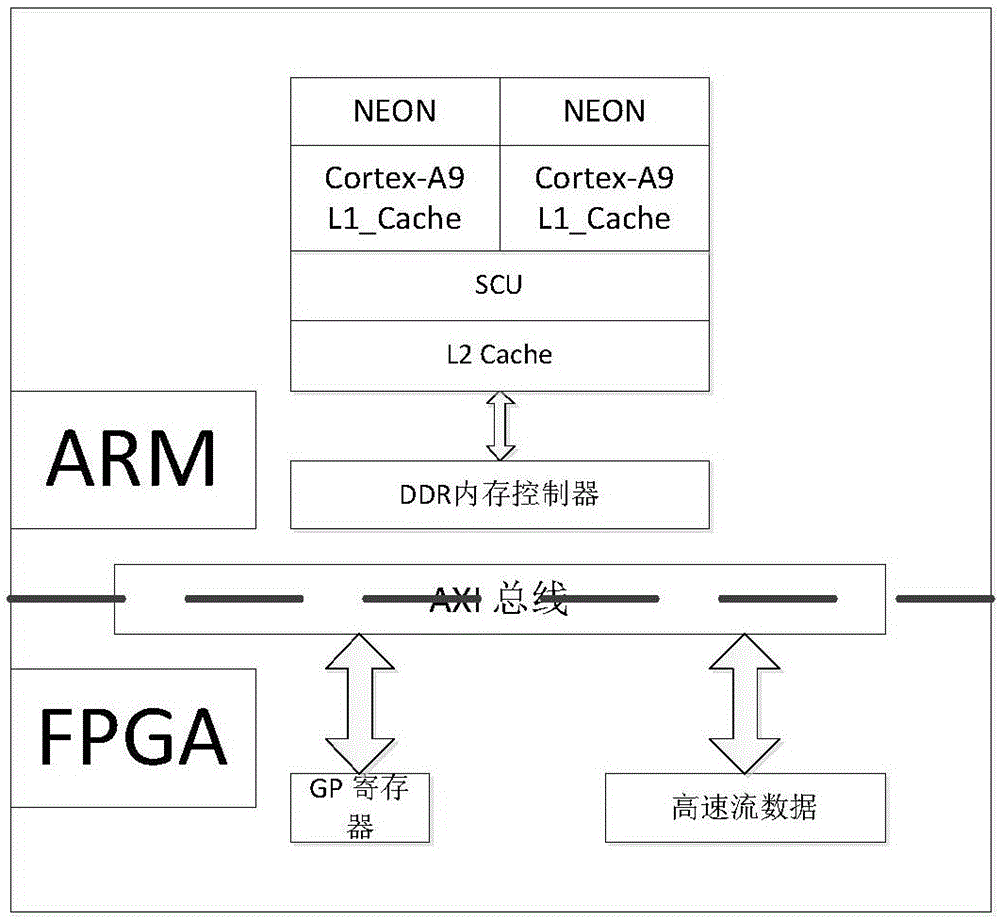

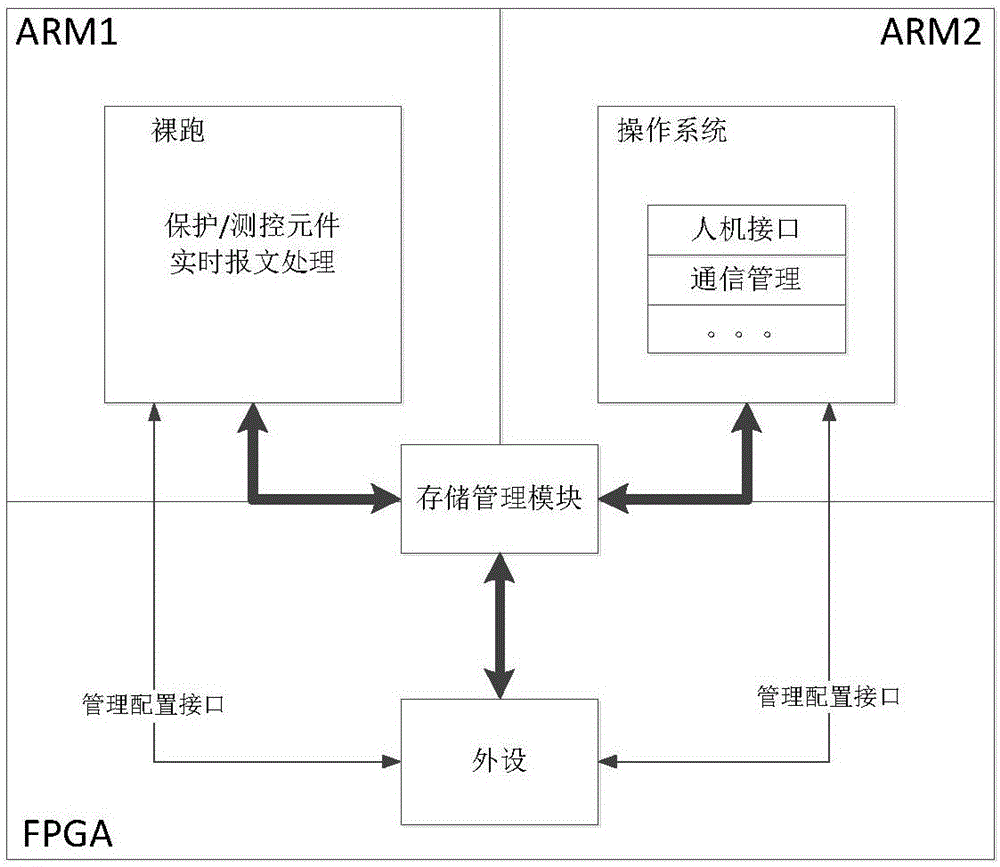

[0025] The Zynq chip is the Zynq dual-core series chip of Xilinx Company, which is composed of a dual-core ARM (2 Cortex-A9s in the figure) and an FPGA. The dual-core ARM and FPGA are connected through the on-chip Advanced Extensible Interface (AXI) bus. Shared external memory with FPGA. The internal hardware structure is as figure 1 shown. The function distribution of a digital intelligent electronic device in AMP mode is as follows: figure 2 As shown, high real-time tasks such as protection calculation and SV / GOOSE message processing run on the naked core, and functions such as man-machine interface and communication management run on the operating system core.

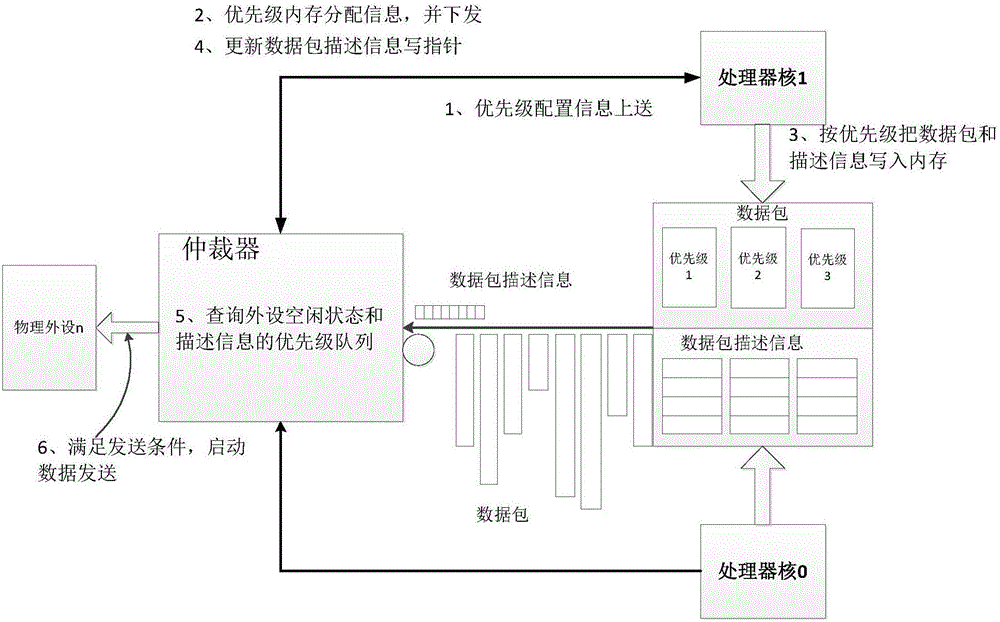

[0026] The ARM and FPGA cores are connected through the AXI standard bus. Configuration information interacts through registers, which is more fle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More