Three-level H-bridge five-level inverter direct-current side capacitor voltage balancing method

A DC-side capacitor and five-level technology, which is applied in the direction of converting AC power input to DC power output, electrical components, and output power conversion devices, can solve DC-side capacitor voltage imbalance, output performance degradation, and dynamic response capabilities Inferior problems, to achieve the effect of fewer optimization times, less calculation, and strong dynamic performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The technical scheme of the present invention is further described below in conjunction with accompanying drawing and embodiment;

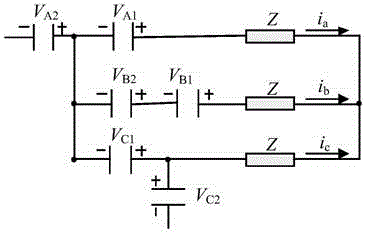

[0020] refer to figure 2 The balance control of the DC side capacitor voltage of the three-phase three-level H-bridge five-level inverter shown adopts the technical scheme of the present invention;

[0021] figure 2 The topology shown can output {V dc , V dc / 2, 0, -V dc / 2, V dc}Five states, respectively in state S x = {2, 1, 0, -1, -2} represents.

[0022] The corresponding pulse mapping of the three-level H-bridge five-level inverter is: state "V dc "corresponds to "1100 0011", state "V dc / 2" corresponds to "1100 0110", state "0" corresponds to "0110 0110", state "-V dc / 2" corresponds to "0110 1100", state "-V dc " corresponds to "0011 1100";

[0023] image 3 Shown is the single-phase circuit structure diagram in each state, V dc / 2 and -V dc / 2 will affect the charging and discharging of the capacitor, and the other t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More