Aging test device and method of integrated circuit chip on the basis of daughter boards and mother board

A chip aging test, integrated circuit technology, applied in the direction of electronic circuit testing, measuring devices, measuring electricity, etc., can solve the problems of lengthening test cycle, long preparation time, reducing test efficiency, etc., to reduce test cost, reduce test cycle, The effect of improving test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The idea, specific structure and technical effects of the present invention will be further described below in conjunction with the accompanying drawings, so as to fully understand the purpose, features and effects of the present invention.

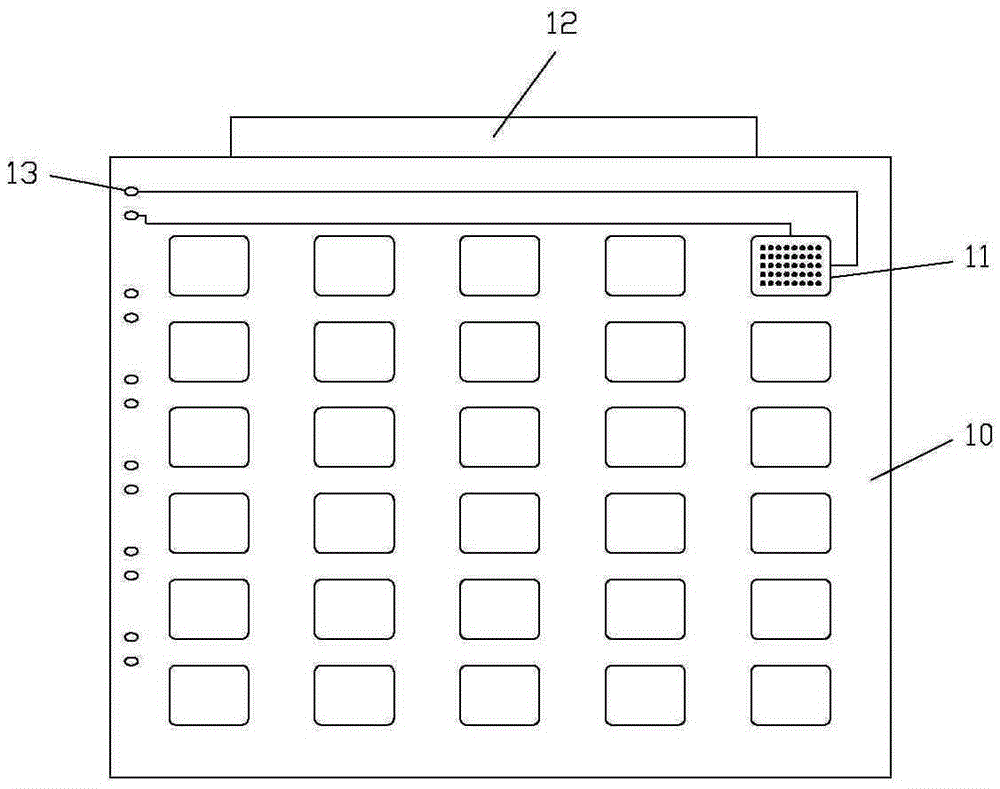

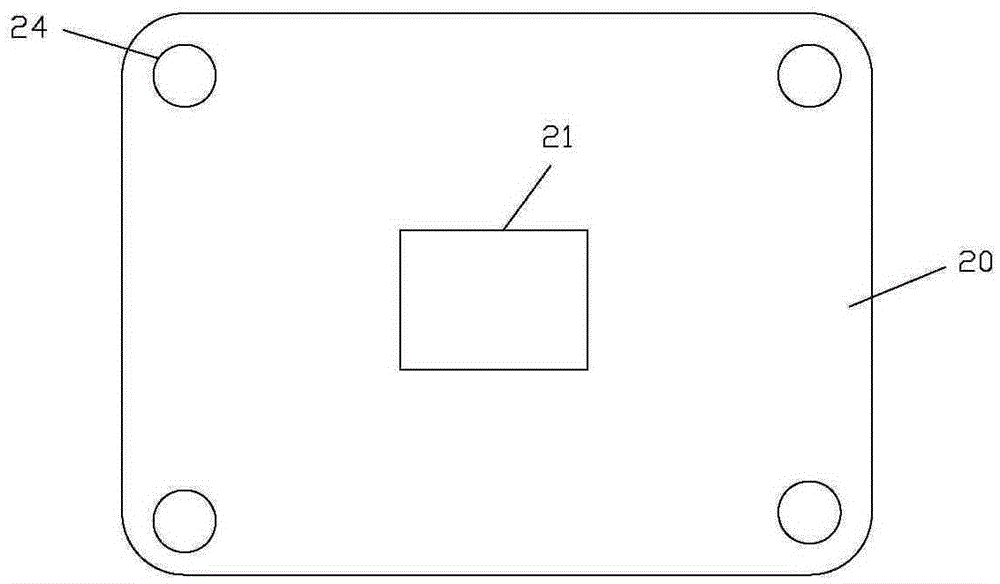

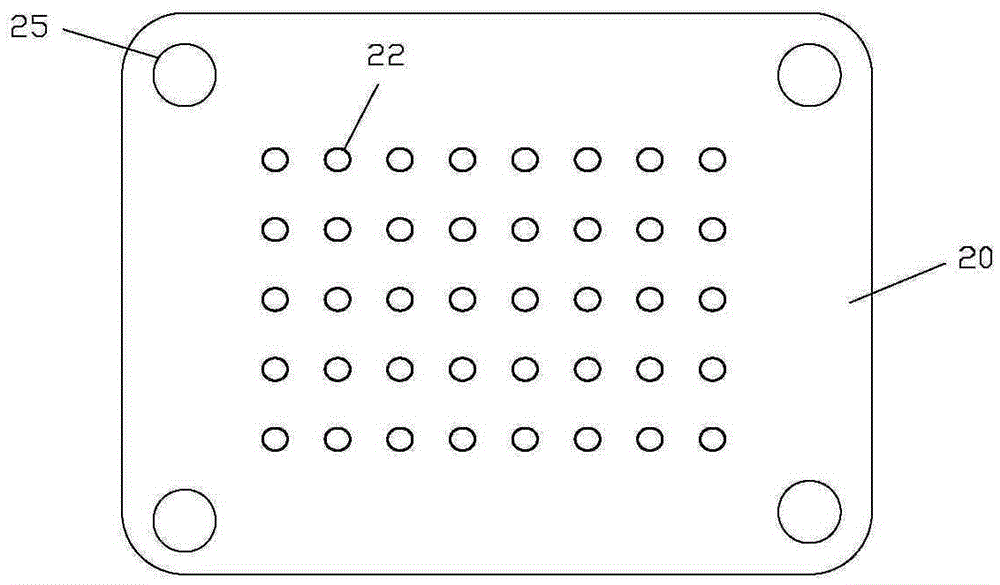

[0034] like Figure 1 to Figure 8 As shown, a burn-in testing device for integrated circuit chips based on daughter boards includes a general burn-in mother board 10 and multiple burn-in daughter boards 20 .

[0035] The universal burn-in motherboard 10 is provided with a plurality of stations 11 for installing the burn-in sub-board 20, a golden finger interface 12 for connecting with the burn-in test machine, a power supply interface 13 and an LED indicator light. There are a plurality of contact pins 111 arranged in an array; among them, the gold finger 12, the power interface 13 and the LED indicator light are used to realize functions such as the access of the drive module, power supply and work instructions of the aging test m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More