Initialization phase alignment method of high-speed source synchronous LVDS interface

A phase-aligned, source-synchronized technology, applied in synchronous signal speed/phase control, synchronizing devices, digital transmission systems, etc., to solve problems such as reduced reliability, inaccurate results, and confusion over the effective window of the transition area, to improve accuracy Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

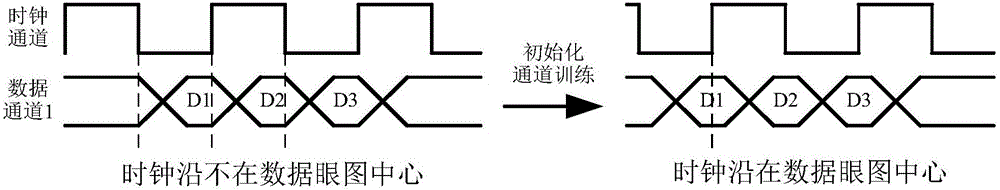

[0025] Changguang Chenxin's CMOS detector GSENSE400 has 8 300Mbps LVDS data channels and 1 150MHz DDR LVDS clock channel at the output, and the image data is 12 bits. The receiving end is Virtex-4 series FPGA of Xilinx Company, the specific method is as follows:

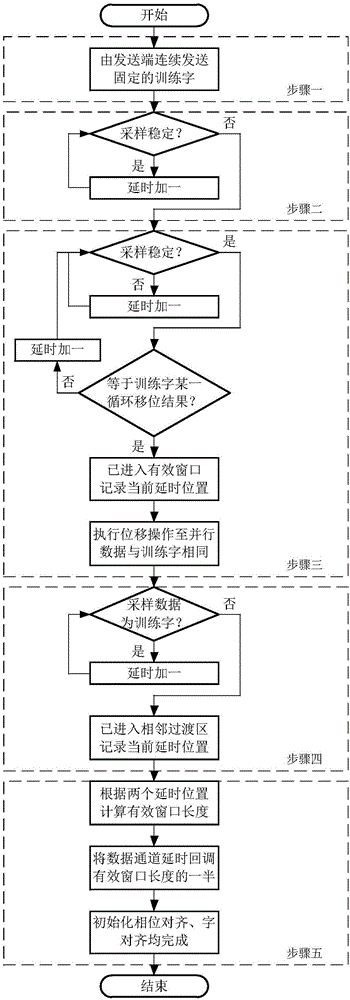

[0026] 1. In the initial stage, channel training is performed on the channel, and the sending end continuously sends fixed training words;

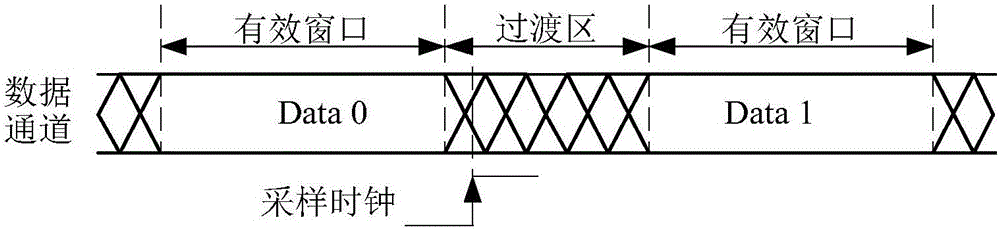

[0027] 2. Find the first transition zone. Compare whether the parallel data sampled continuously is the same, that is, judge whether the parallel data sampled is stable. If it is stable, add one to the delay, and perform this step again; if it is unstable, it indicates that the first transition zone has been found, and perform step 3;

[0028] 3. Go through the first transition zone. Determine whether the sampled parallel data is stable, if not, it means it is still in the transition zone, add one to the delay, and execute this step again. If it is stable, judge whether it is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More