High-speed parallel low-density parity-check decoder with multi-core scheduling and its decoding method

A low-density parity and decoder technology, applied in the field of high-speed parallel low-density parity-check decoder and its decoding, can solve the problem of insufficient utilization of hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be described in further detail below in conjunction with the accompanying drawings.

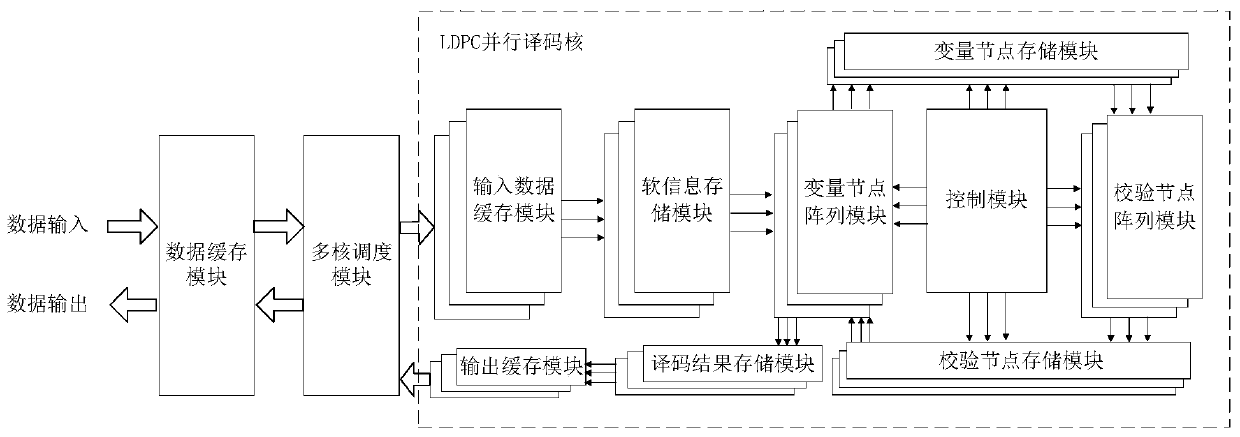

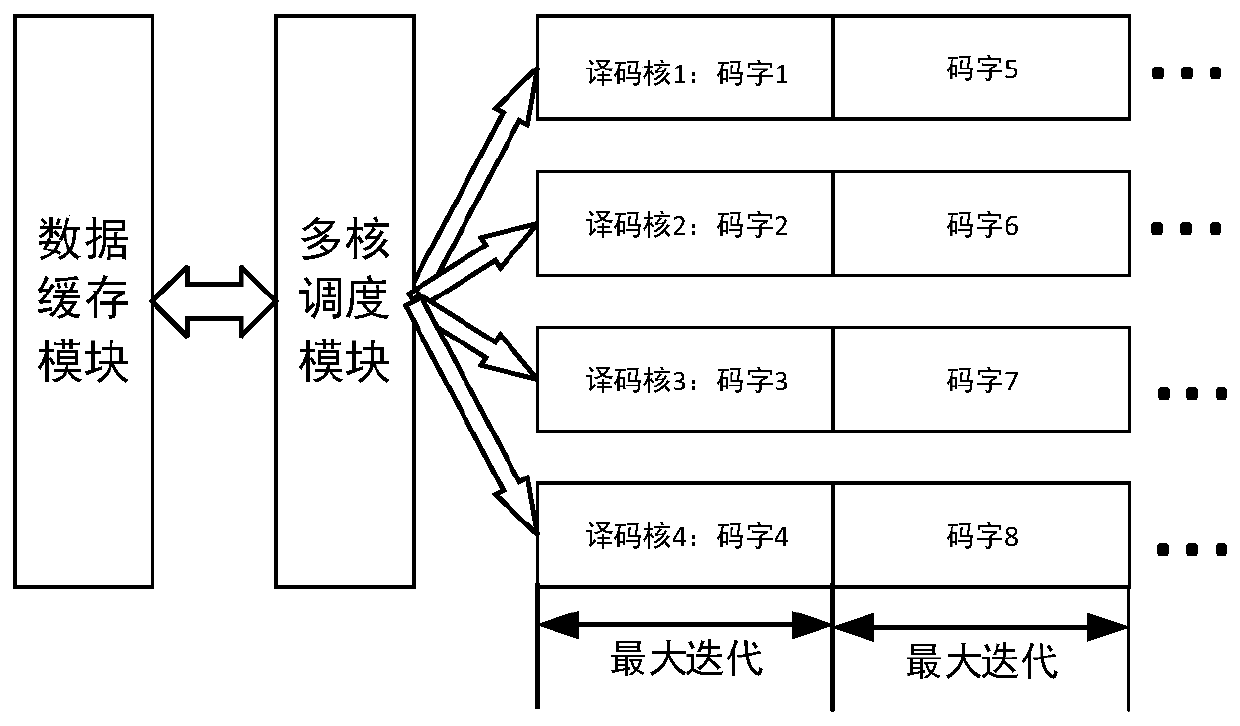

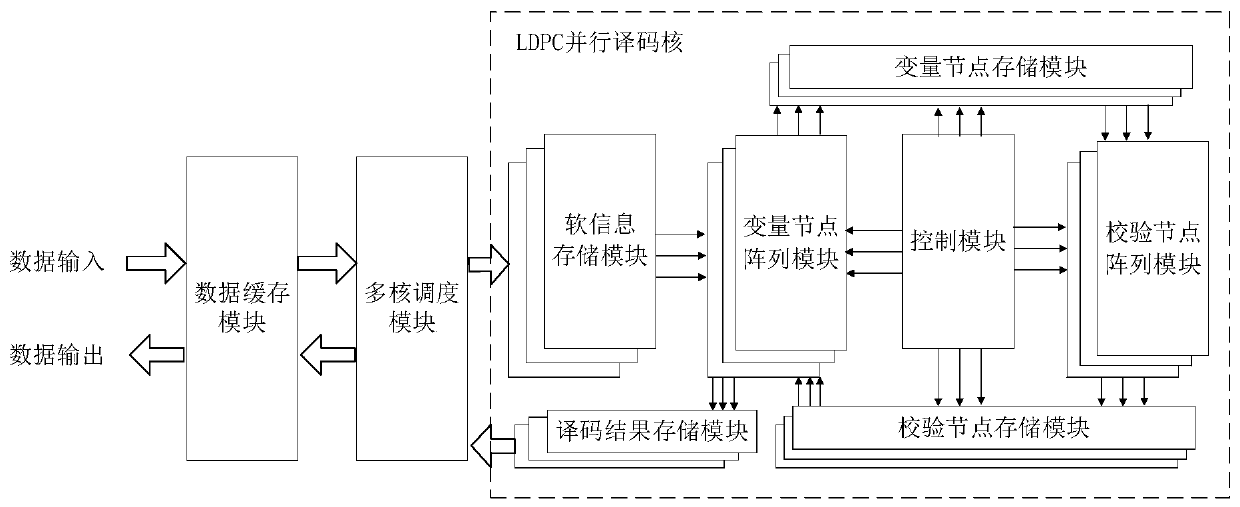

[0028] A kind of high-speed LDPC decoder of multi-core scheduling proposed by the present invention, such as figure 2 As shown, it includes sequentially connected data cache modules, multi-core scheduling modules, and LDPC parallel decoding cores composed of multiple decoding cores, which can be implemented with an FPGA chip the same as traditional LDPC decoders; this multi-core scheduling high-speed The difference between the LDPC decoder and the traditional decoder is:

[0029] 1) The data buffer module is composed of FIFO inside the FPGA. This FIFO has a deeper storage depth than the FIFO in the traditional LDPC decoder data buffer module, so that more codeword sequence information can be cached to ensure that the next codeword arrives. , can have enough buffer space, after a decoding core completes the decoding of the previous code word, assign the new ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More