Array substrate

An array substrate and pixel electrode technology, applied in nonlinear optics, instruments, optics, etc., can solve problems affecting panel display uniformity, and achieve the effects of improving uniformity, consistent output voltage, and consistent voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

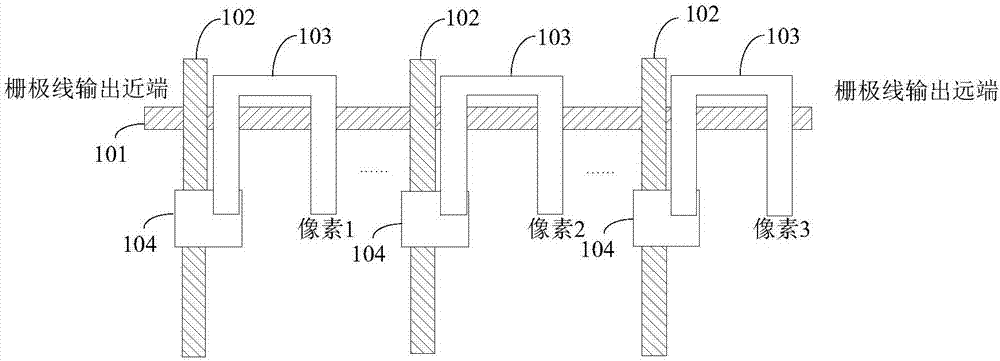

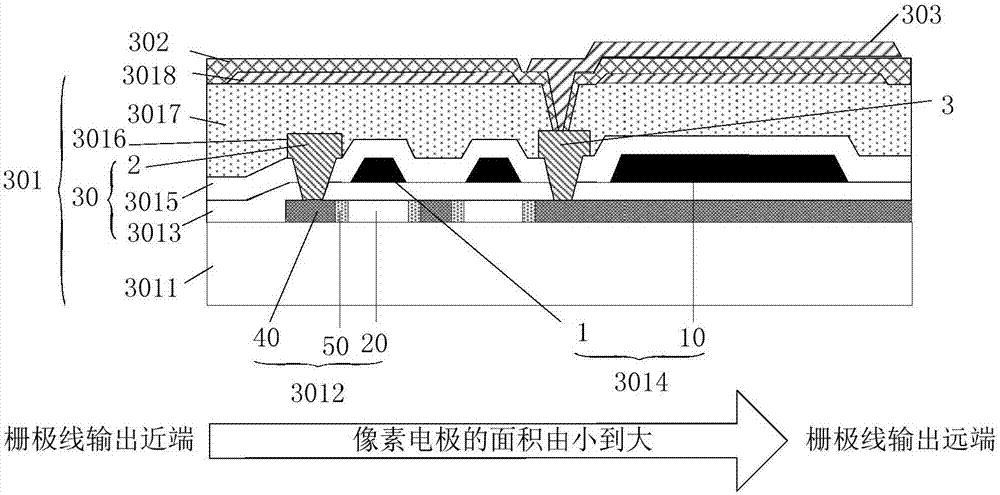

[0039] Such as image 3 Shown is a schematic cross-sectional view of each film layer of the array substrate according to the embodiment of the present invention. The array substrate of this embodiment mainly includes a substrate 301 , a passivation layer 302 and a pixel electrode layer 303 . Specifically, the substrate 301 includes the gate lines 10 . A passivation layer 302 is formed on the substrate 301 . The pixel electrode layer 303 is formed on the passivation layer 302 and includes the pattern of the pixel electrode. Wherein, along the direction from the output near end of the gate line 10 to the output far end (such as image 3 As indicated by the direction marked by the middle arrow, that is, the direction from near to far from the scanning signal driving circuit), the area of the pixel electrode gradually increases.

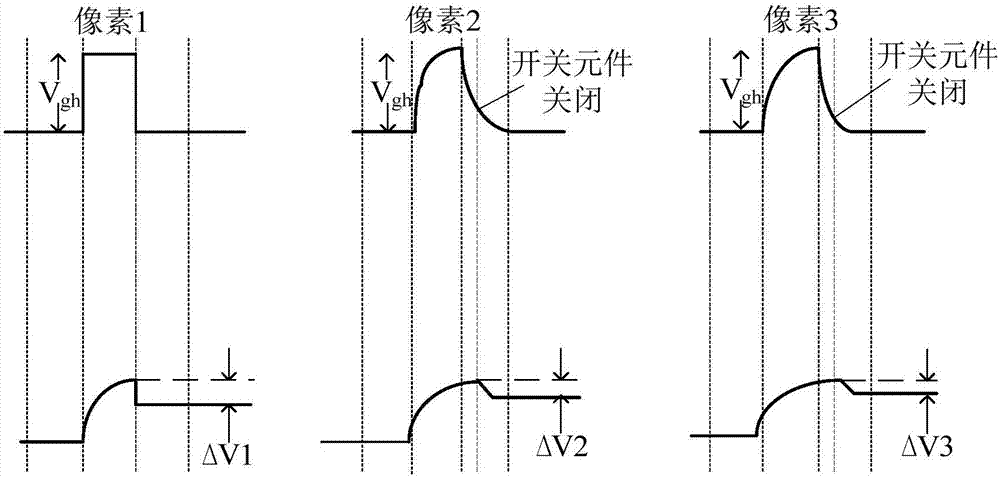

[0040] In a liquid crystal display panel, the expression of the gate line voltage drop is:

[0041]

[0042] Among them, ΔVp represents the vo...

Embodiment 2

[0051] This embodiment is a further optimization of Embodiment 1.

[0052] Figure 4 A schematic diagram of wiring of an array substrate according to Embodiment 2 of the present invention is shown. Such as Figure 4 As shown, the pixel electrode 3031 has a comb structure with comb teeth. Along the direction from the output near end of the gate line 10 to the output far end (such as Figure 4 As indicated by the direction marked by the middle arrow, that is, the direction from near to far from the scanning signal driving circuit), the length of the comb teeth is the same, and the width gradually increases. That is, the area of the pixel electrode 3031 is changed by changing the width of the comb teeth without changing the length of the comb teeth. This embodiment only provides a preferred manner, and does not make specific limitations.

[0053] In this embodiment, since the size of each pixel has been determined and the length of the comb teeth of each pixel is close to ...

Embodiment 3

[0059] In this embodiment, the structure of the substrate 301 in the first embodiment is further optimized.

[0060] Such as image 3 As shown, the substrate 301 is a complex of various film layers below the passivation layer 302 . The array substrate further includes a plurality of switch elements 30 , and each switch element 30 is electrically connected to a corresponding pixel electrode 3031 . Preferably, the switch element 30 is a double-gate thin film transistor.

[0061] In this embodiment, the substrate 301 may include a substrate 3011, a channel layer 3012, a first insulating layer 3013, a first metal layer 3014, a second insulating layer 3015, a second metal layer 3016, a flat layer 3017, and a common electrode layer 3018 .

[0062] Specifically, the channel layer 3012 is formed on the substrate 3011 and includes a plurality of conductive channels 20 . The first insulating layer 3013 is formed on the channel layer 3012 and the exposed substrate 3011 . The first m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More