PCIE-based FPGA updating system and method

A base address and device technology, which is applied in the field of PCIE-based FPGA update system, can solve the problems of unsatisfactory large-scale update and slow loading speed of FPGA update speed, so as to improve FPGA loading speed, save labor cost and improve work efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

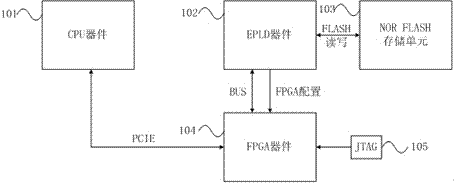

[0035] Such as figure 1 As shown, it is a schematic diagram of the equipment structure of the PCIE-based FPGA update system in Embodiment 1 of the present invention. The update system includes a CPU device 101, an erasable programmable logic (Erasable Programmable LogicDevice, EPLD) device 102, a non-volatile Flash memory (NOR Flash) storage unit 103, Field Programmable Gate Array (Field Programmable Gate Array, FPGA) device 104, JTAG (Joint Test Action Group) download interface 105, wherein CPU device 101 is connected with FPGA device 104 through PCIE interface, FPGA device 104 is connected with EPLD device 102 through internal bus interface and FPGA configuration signal line, and EPLD device 102 is connected with NOR Flash storage unit 103 through FLASH read and write signal line, and JTAG download interface 105 is the download interface that FPGA de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More