Multi-core processor deterministic repetition-oriented optimized segmental memory competition recording system and method

A multi-core processor and recording system technology, applied in the direction of multi-channel program device, program synchronization, hardware monitoring, etc., can solve the problems of conflicting dependencies, unable to find out records, record redundancy, etc., to optimize memory contention logs, The effect of reducing the number of times

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

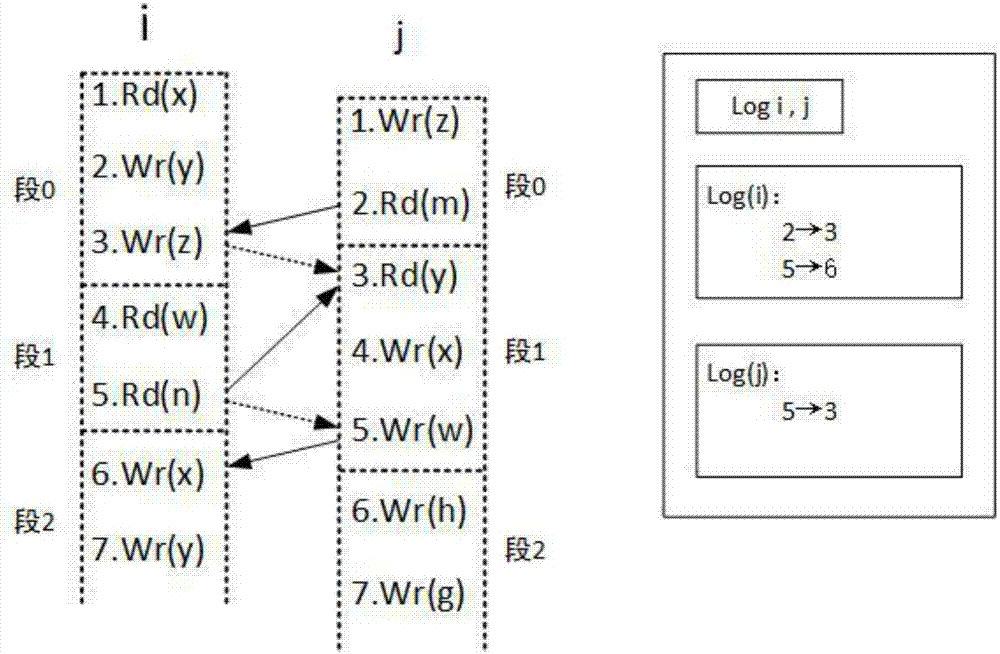

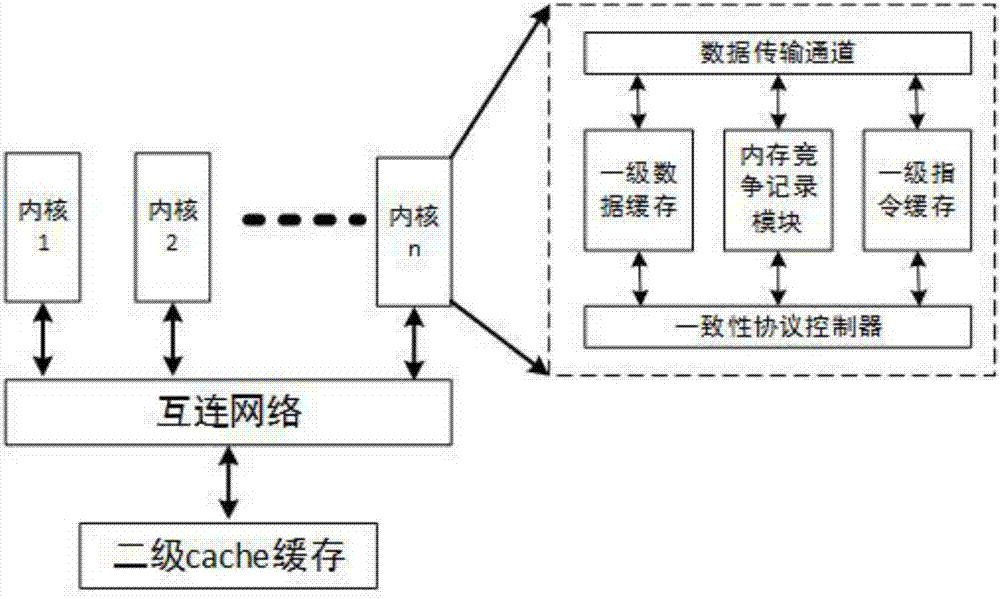

[0033] Specific implementation mode one: combine figure 1 with figure 2 To illustrate, the optimized segmented memory contention recording system for multi-core processor deterministic replay described in this embodiment includes n processor cores and shared data buffer memory (L2Cache), wherein the n processors Each processor core includes a memory contention recording module (DRstate), a private data buffer memory (L1 Cache), a private instruction buffer memory (Instructions L1 Cache), a coherent protocol controller (Protocol controller), and a data transmission channel; its characteristics In that: the memory contention recording module (DRstate) includes an instruction counter (IIC), a segment counter (SC), a control logic module (CL) and a segment number register (SN);

[0034] Instruction counter (IIC), used to record the number of instructions;

[0035] Segment counter (SC), used to record the segment number of the processor core;

[0036] Control logic module (CL),...

specific Embodiment approach 2

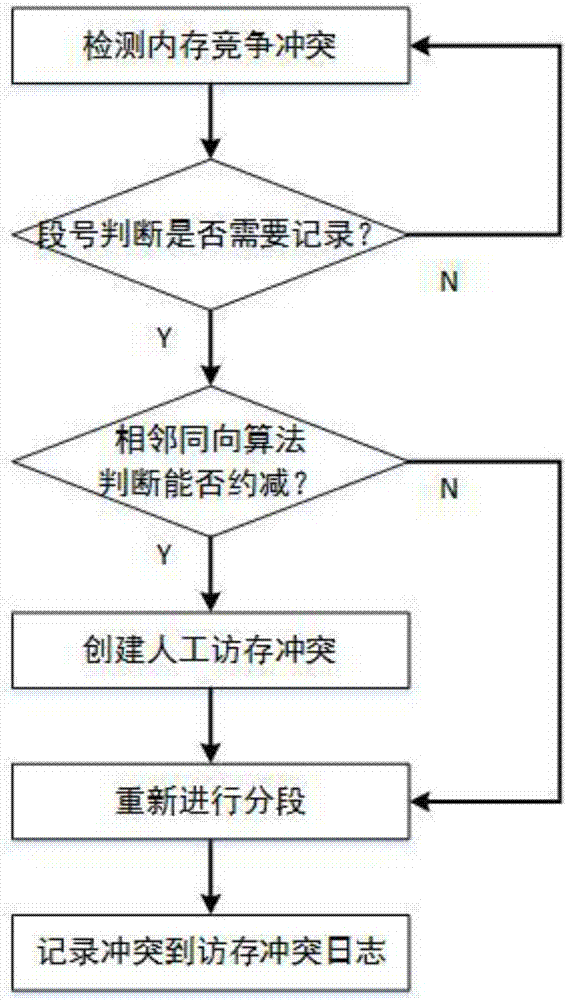

[0043] Specific embodiment two: this embodiment is based on the memory recording method of the multi-core processor deterministic replay-oriented optimized segmentation memory contention recording system described in specific embodiment one, and the working process of the described control logic module includes The following steps:

[0044] When the submitted instruction is a memory operation instruction, update the value of the instruction counter IC, and set the segment number of the memory block corresponding to the memory operation;

[0045] When a requester consistency request is received, a step of detecting whether memory competition occurs through a buffer memory (Cache) consistency protocol controller;

[0046] When the cache memory (Cache) coherence protocol controller detects the memory competition, the step of judging whether the memory competition needs to be recorded is determined by using an optimization segmentation method;

[0047] When the memory competition...

specific Embodiment approach 3

[0050] Specific implementation mode three: combination image 3 , this embodiment is a further limitation of the memory contention recording method oriented to multi-core processor deterministic replay described in the second specific embodiment, when the cache memory (Cache) coherence protocol controller detects memory contention, use The steps of optimizing the segmentation method to determine whether the memory competition needs to be recorded are as follows:

[0051] When a new memory competition is detected, compare it with the current occurrence sequence of each pair of conflicts that have been recorded. If there is a pair of recorded conflicts whose segment number is greater than the first occurrence of the conflict, the later occurrence If the segment number is smaller than the party after the conflict, it means that the current sequence of occurrence of the conflict can be deduced and will not be recorded. Otherwise, it is determined that the memory competition needs ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More