Fault-based three-dimensional optical on-chip network architecture, communication method and optical router

An optical-on-chip network and communication method technology, which is applied to architectures with a single central processing unit, instruments, and general-purpose stored-program computers, can solve problems such as uneven distribution of vertical interconnect lines, achieve good scalability, and control the overall Effects of energy consumption and efficient communication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0024] Existing 3D optical on-chip networks using low-order vertical interconnection lines cannot fully utilize the high bandwidth advantages of 3D networks, which can easily lead to vertical blocking problems, while existing 3D optical on-chip networks using interlayer high-order interconnection mechanisms The layout method adopted by the network will lead to uneven distribution of vertical interconnection lines, which will destroy the regularity of the network and limit the expansion of the network; it will also cause serious heat dissipation problems; in addition, the existing high-level interconnection between layers The insertion loss of high-end optical routers is large, which can easily lead to an increase in network energy consumption.

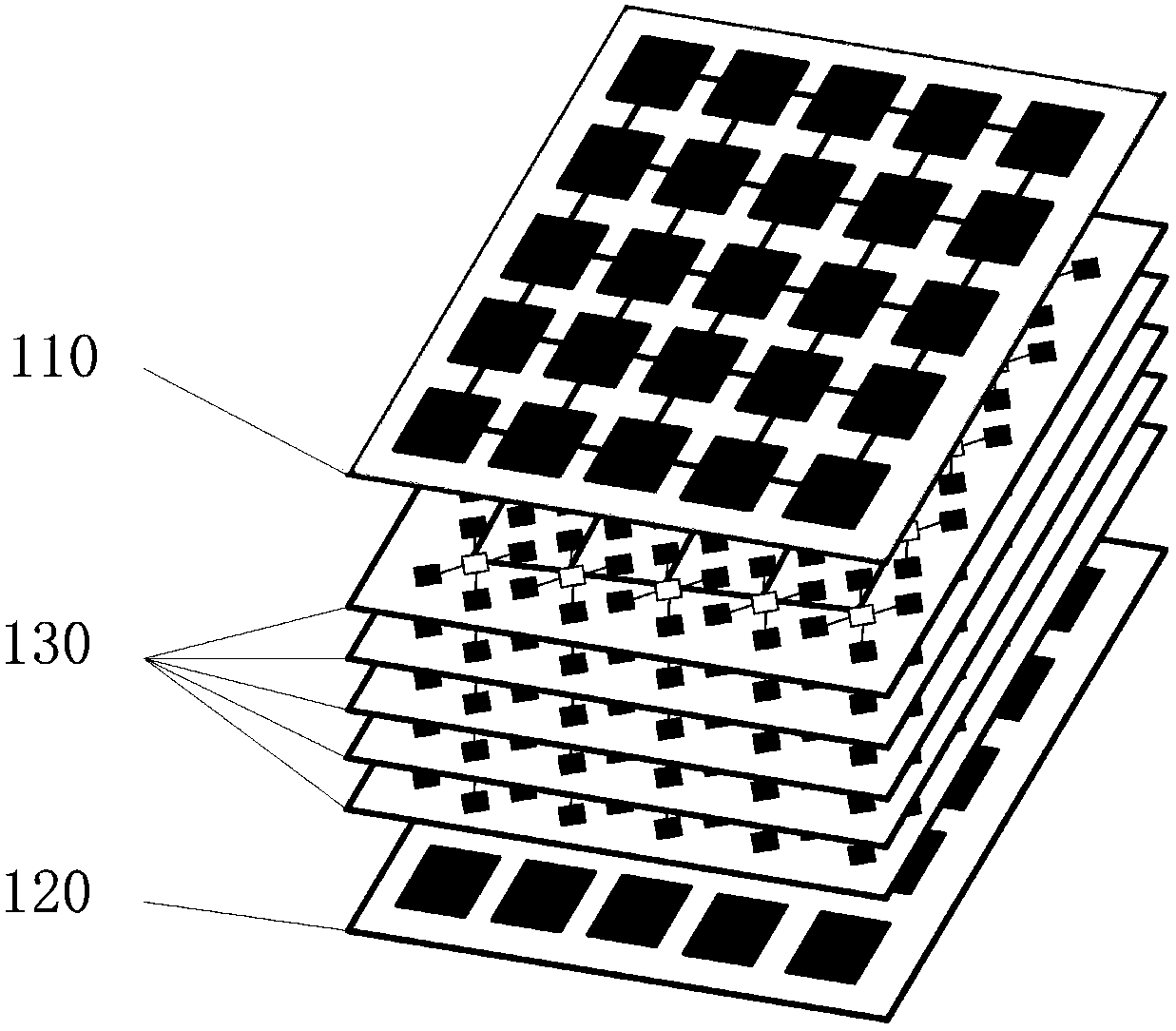

[0025] Aiming at the above technical problems, the present invention carried out innovation and research, and proposed a three-dimensional optical-on-chip network architecture based on stacking faults, see the attached figure 1 , the f...

Embodiment 2

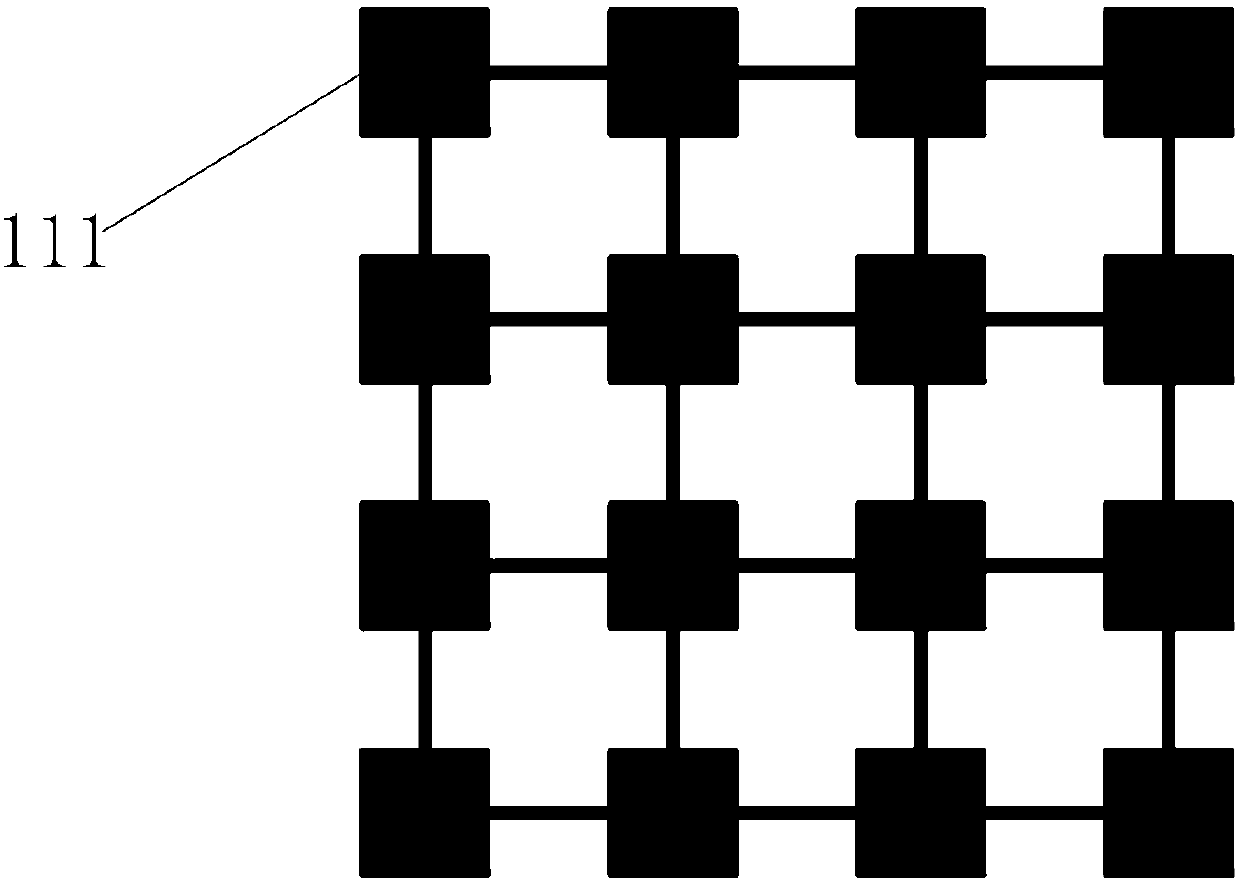

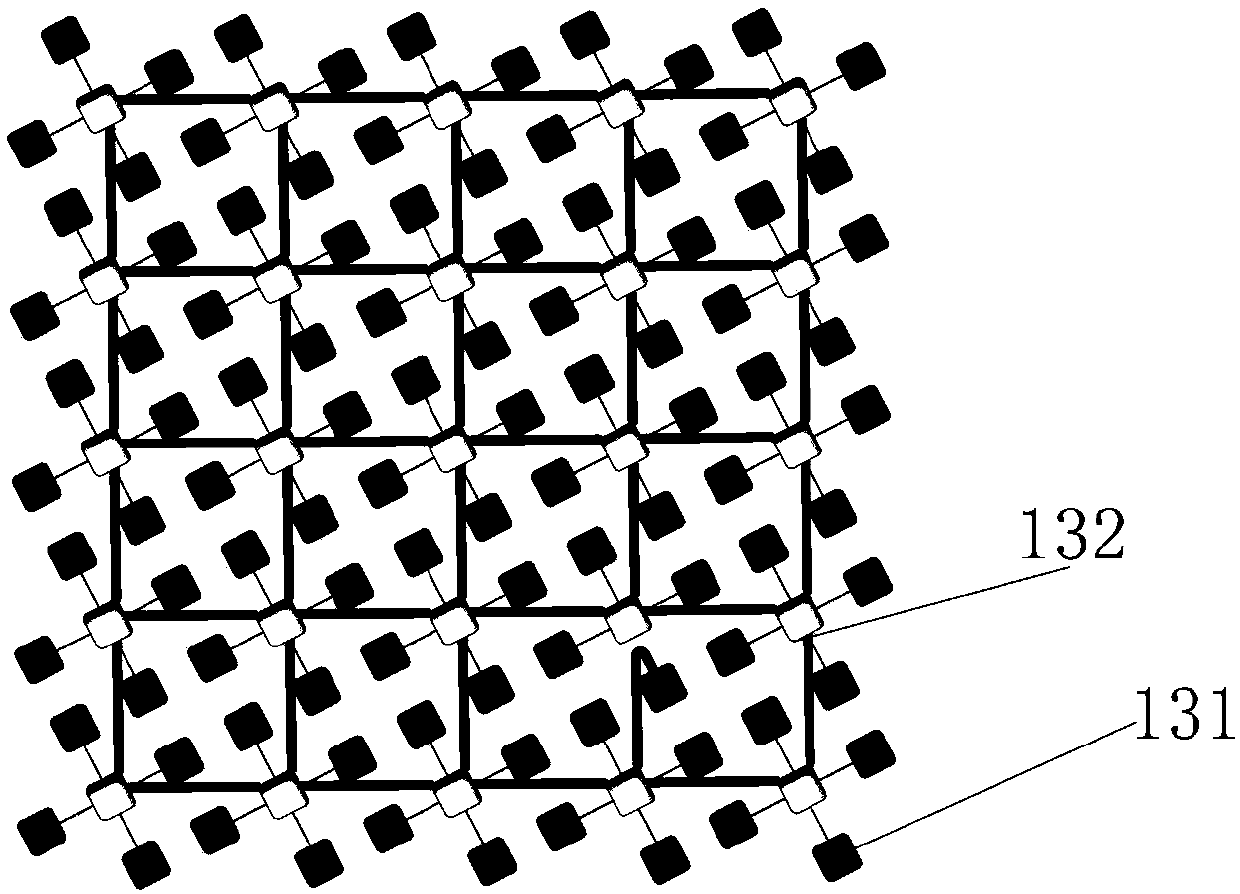

[0028] The fault-based three-dimensional optical on-chip network architecture is the same as that in Embodiment 1. All IP cores and routers in the network use the (x, y, z, m) coordinate system, and the meanings of x, y, and z are the same as the Cartesian three-dimensional coordinate system, where 0 ≤x,y≤(N-1), 0≤z≤6, m is set to 0 for all routers, for the IP core in the middle layer, the positive direction of m is clockwise within the node, 1≤m≤4, And in each intermediate layer, optical / electrical routers at the same position in the optical network and electrical network share the same set of coordinate information, refer to the attached Figure 4 , the coordinate information in each intermediate layer is x=x 0 ,y=y 0 The electrical router 132 in the node is respectively connected to the top layer and the bottom layer through its upper and lower ports and the corresponding two TSVs. The coordinate information is x=x 0 ,y=y 0 The new nine-port optical router 111 and five-p...

Embodiment 3

[0031] The present invention is also a novel nine-port non-blocking optical router, referred to as a nine-port optical router, which is dedicated to a layer-fault-based three-dimensional optical network on chip architecture, which is the same as that of Embodiment 1-2. The new nine-port non-blocking optical router includes nine pairs of full-duplex ports, of which the southbound port, northbound port, westbound port, and eastbound port are respectively used to connect the south, north, west, and east ports of the current nine-port optical router. The nine-port optical router on the side; the remaining five ports of the new nine-port non-blocking optical router: ports z=1, z=2, z=3, z=4, z=5 are respectively used for optical / electrical interface, electrical The / optical interface and TSV connect the electrical routers in the five intermediate layers. Since the network uses the OXY routing algorithm, there is no optical path between the south / north port and the east / west port in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More