Patents

Literature

38 results about "Network on chip architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

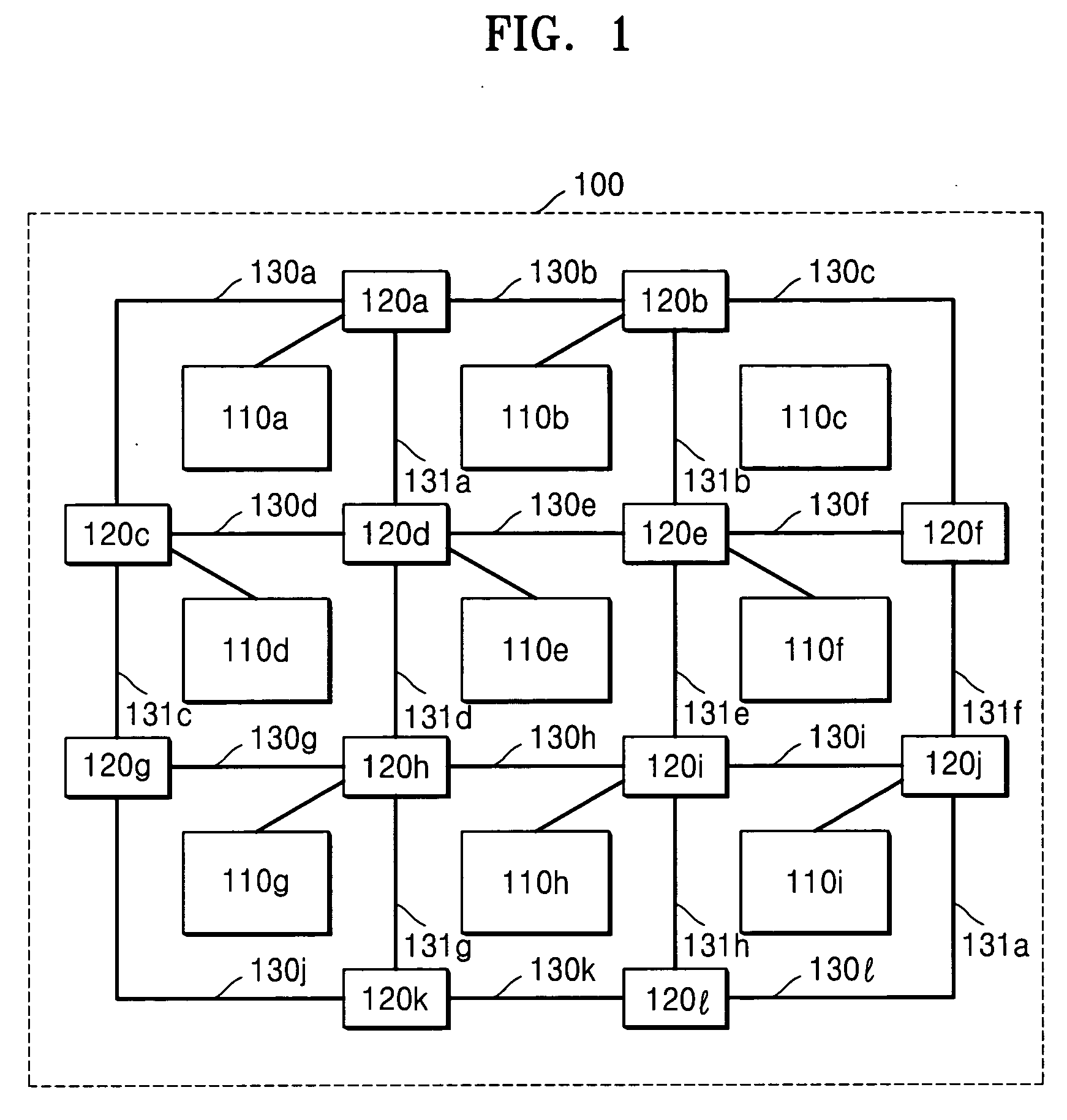

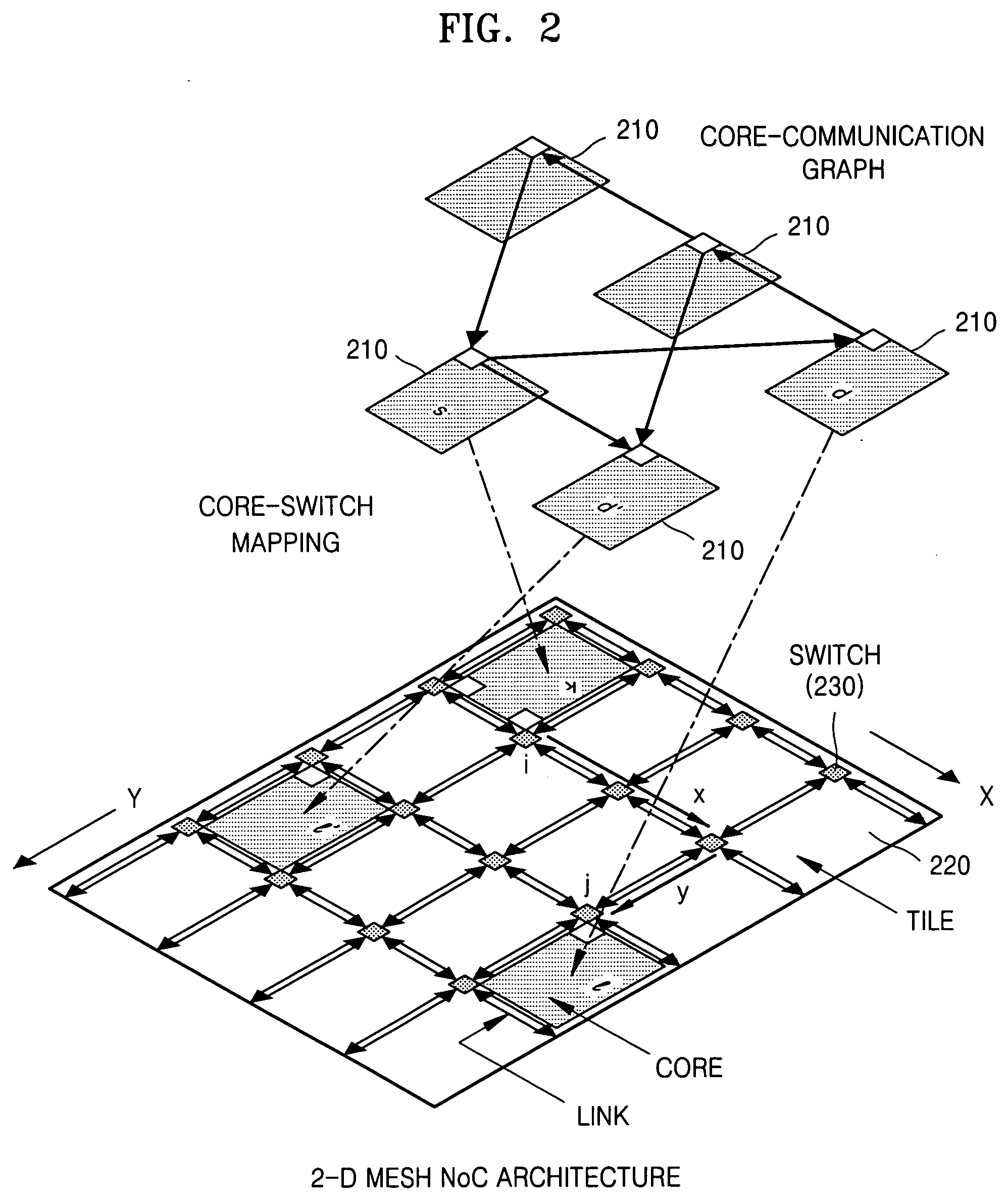

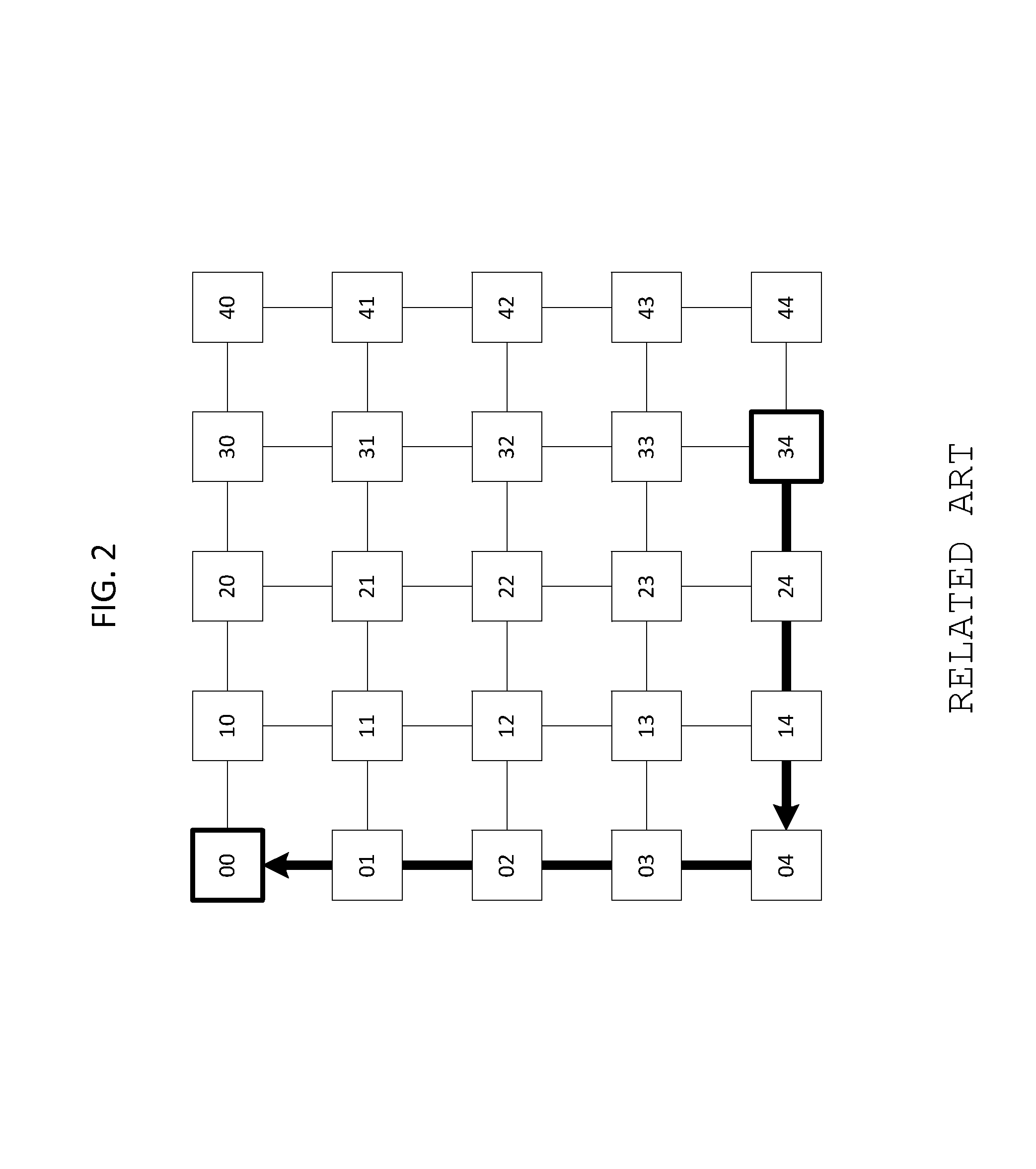

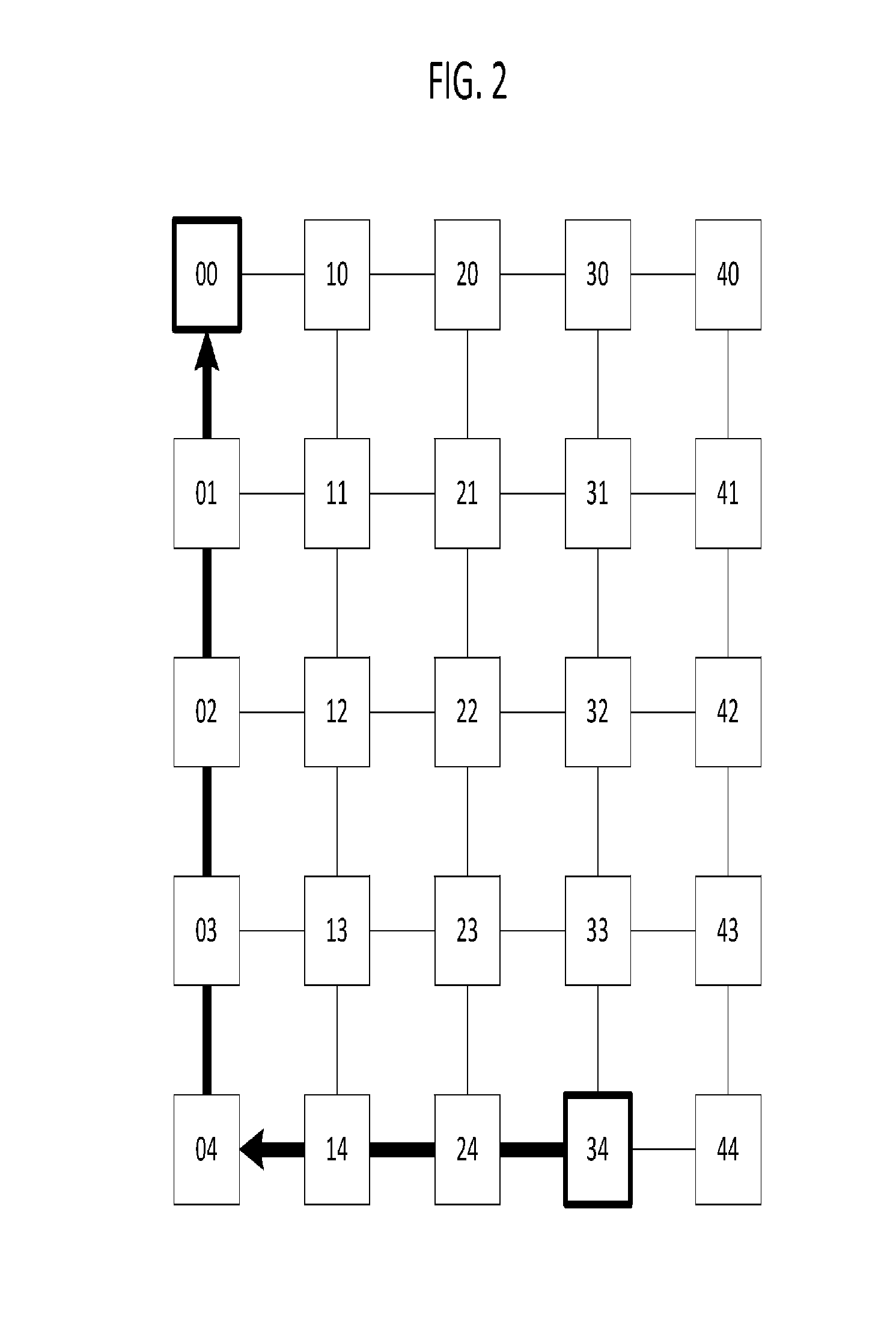

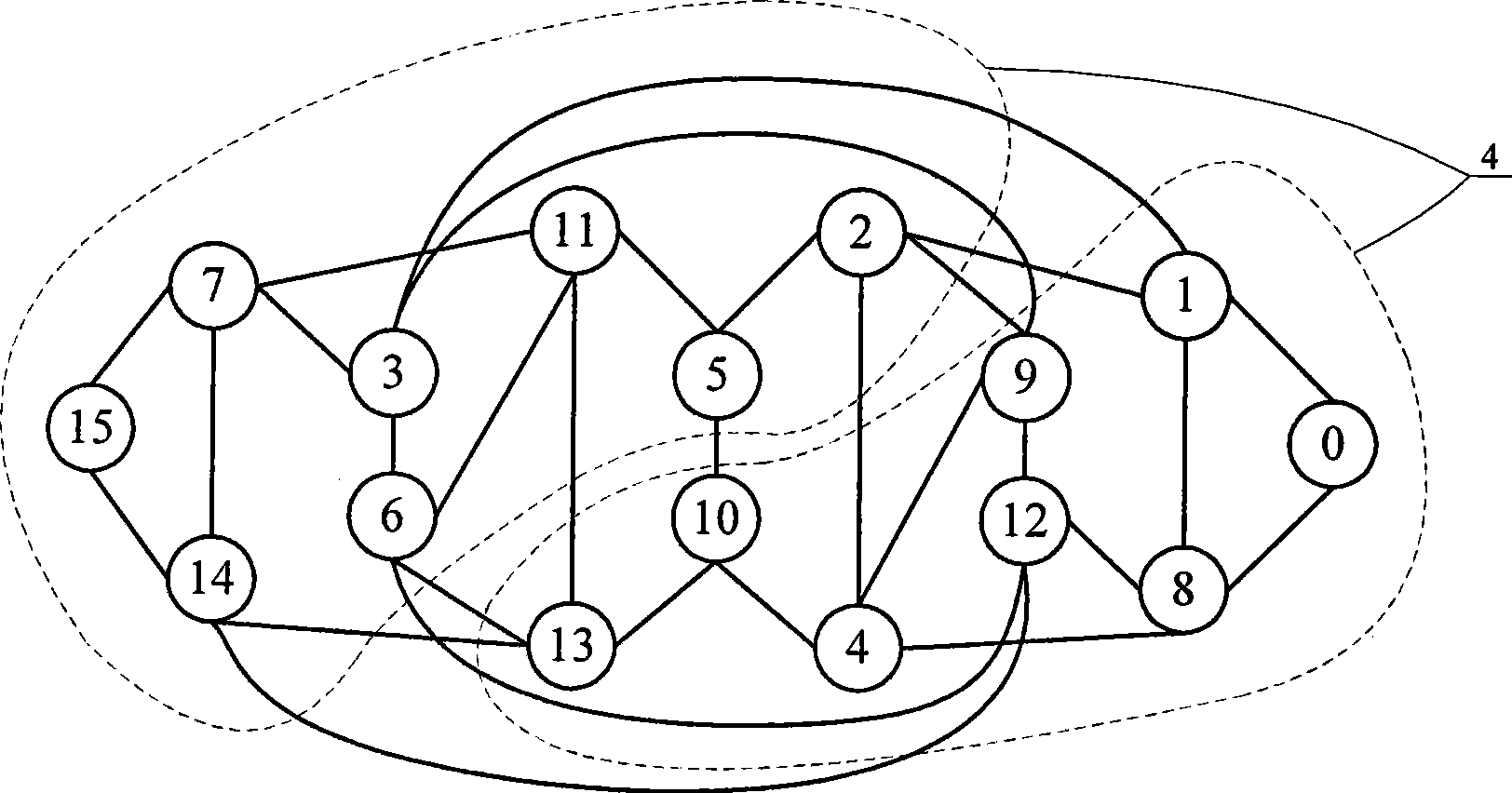

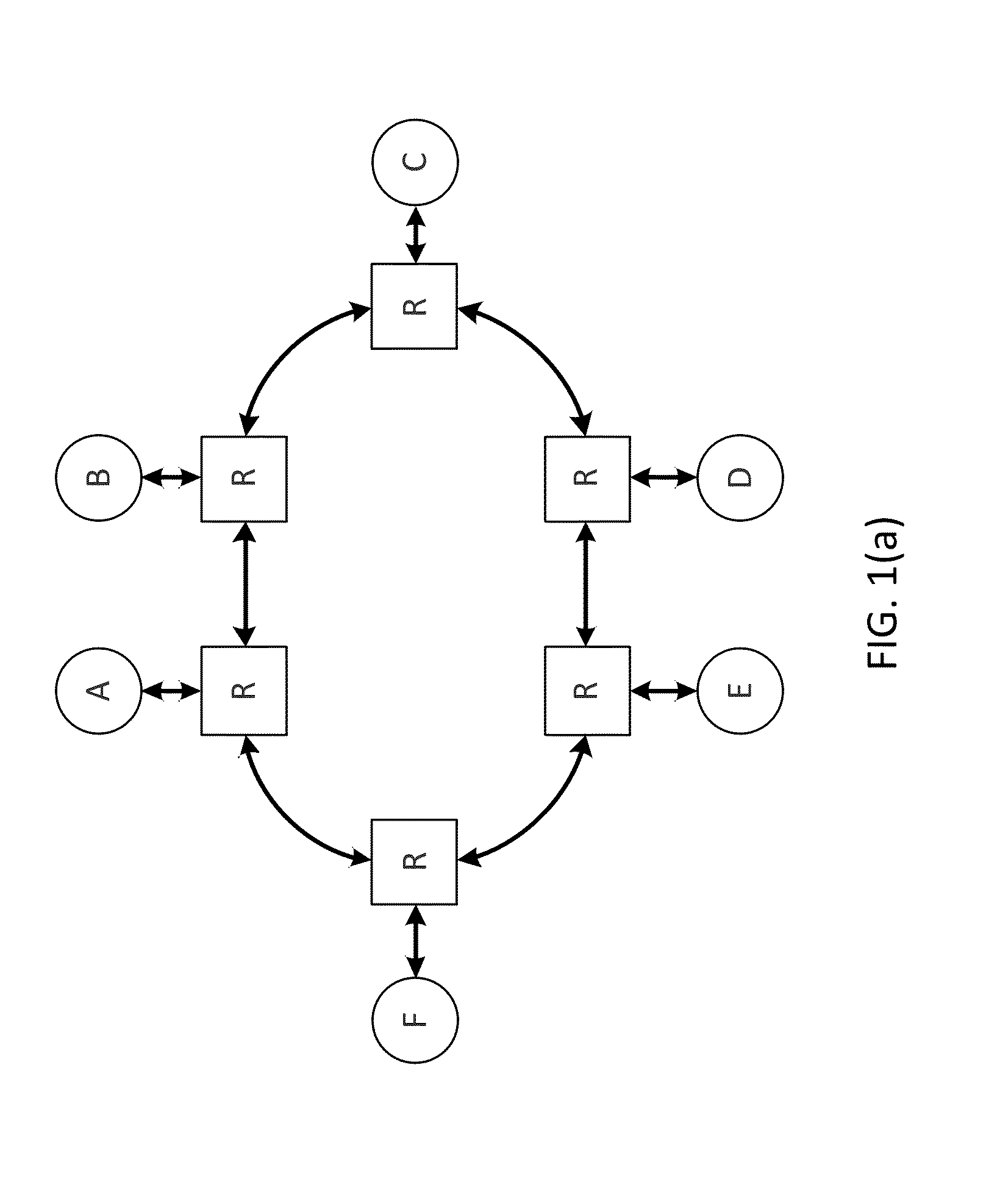

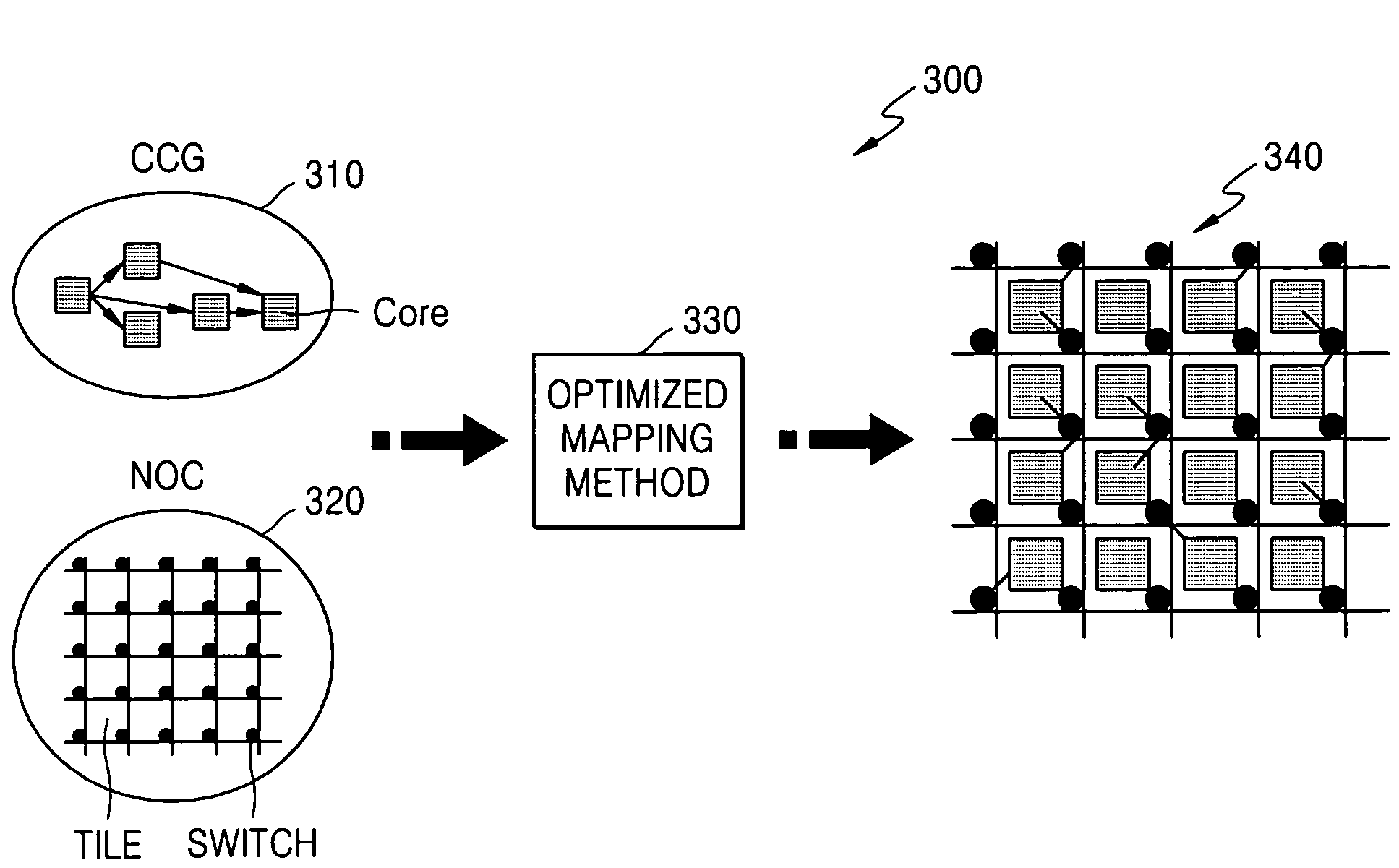

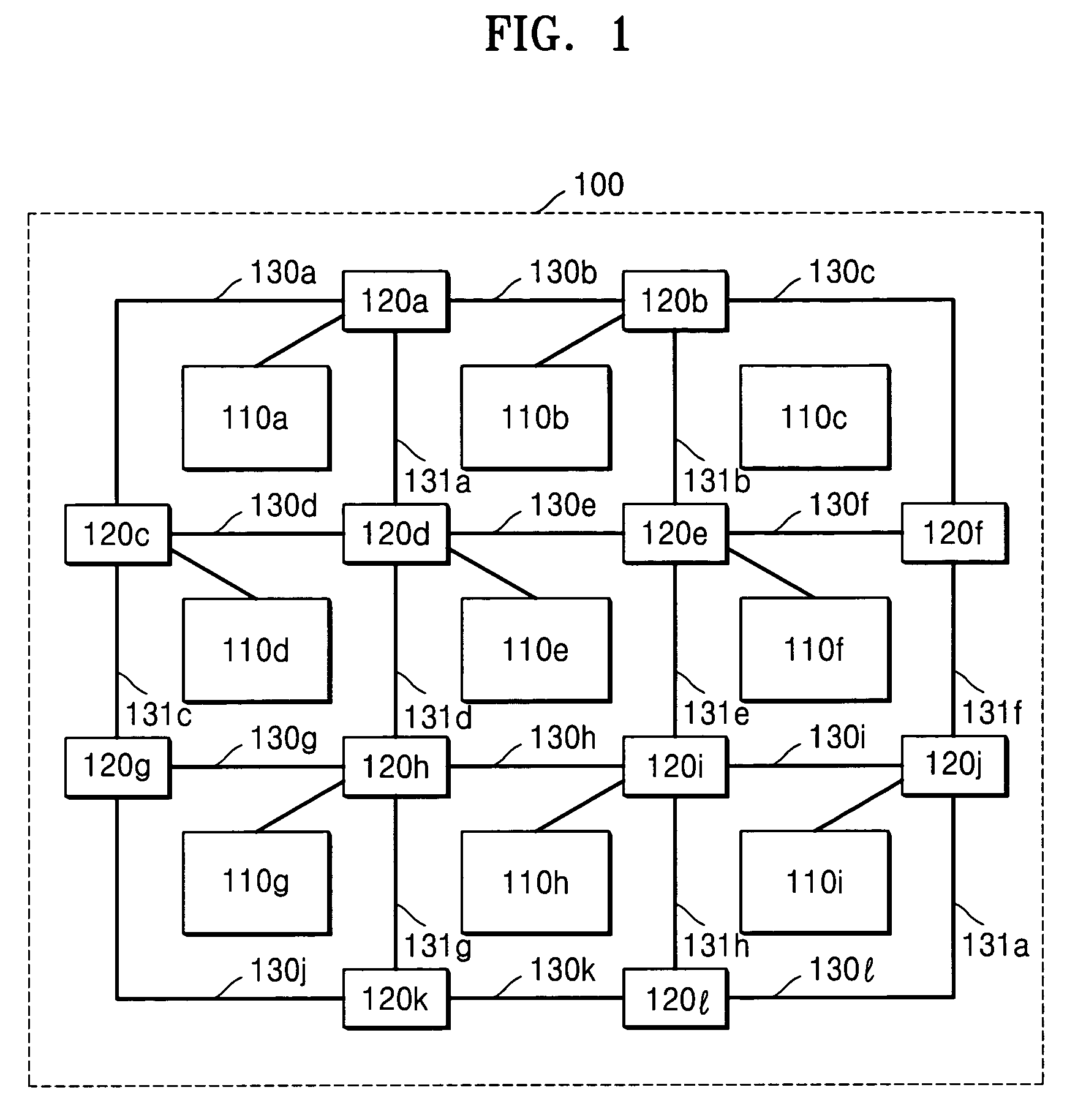

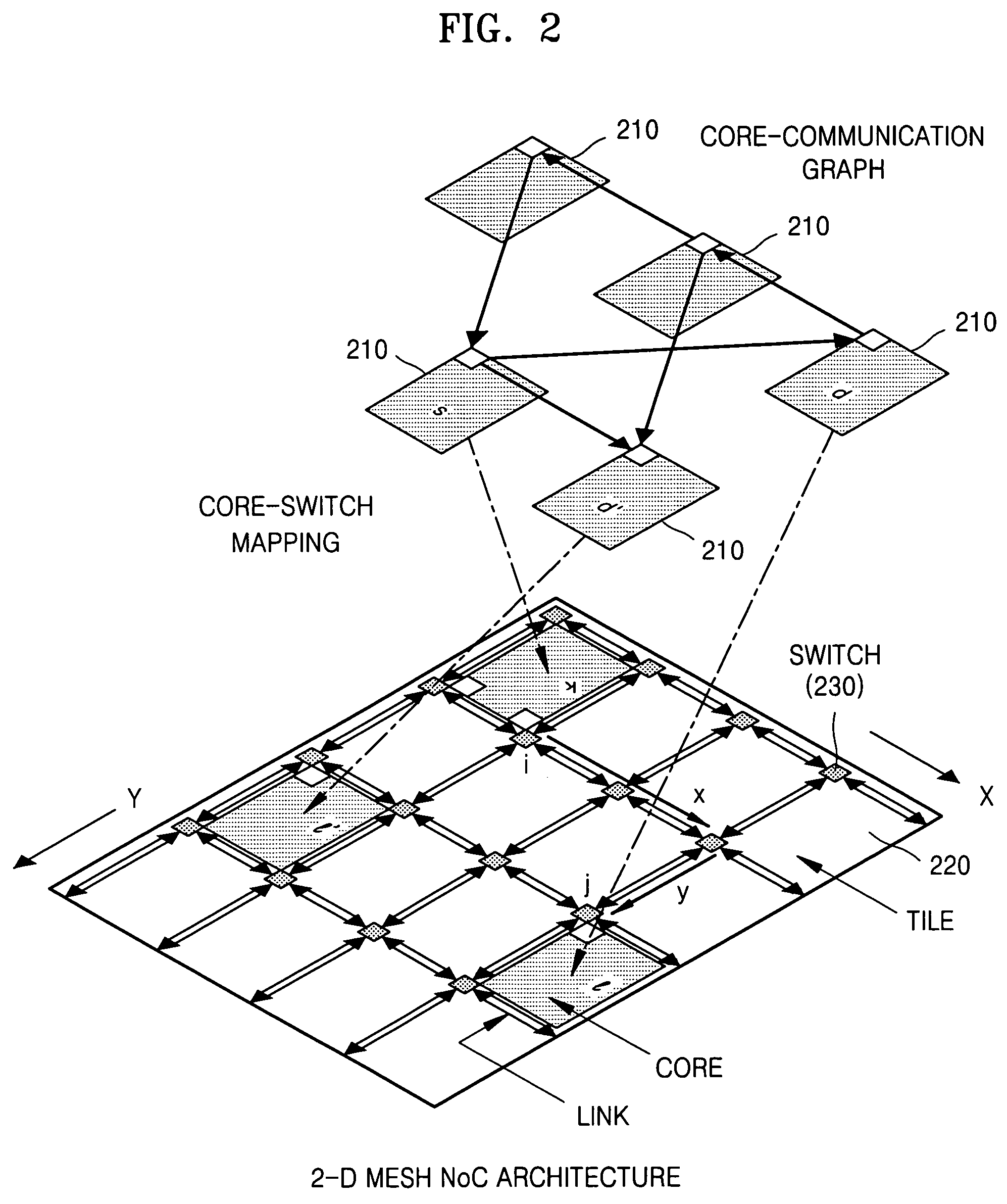

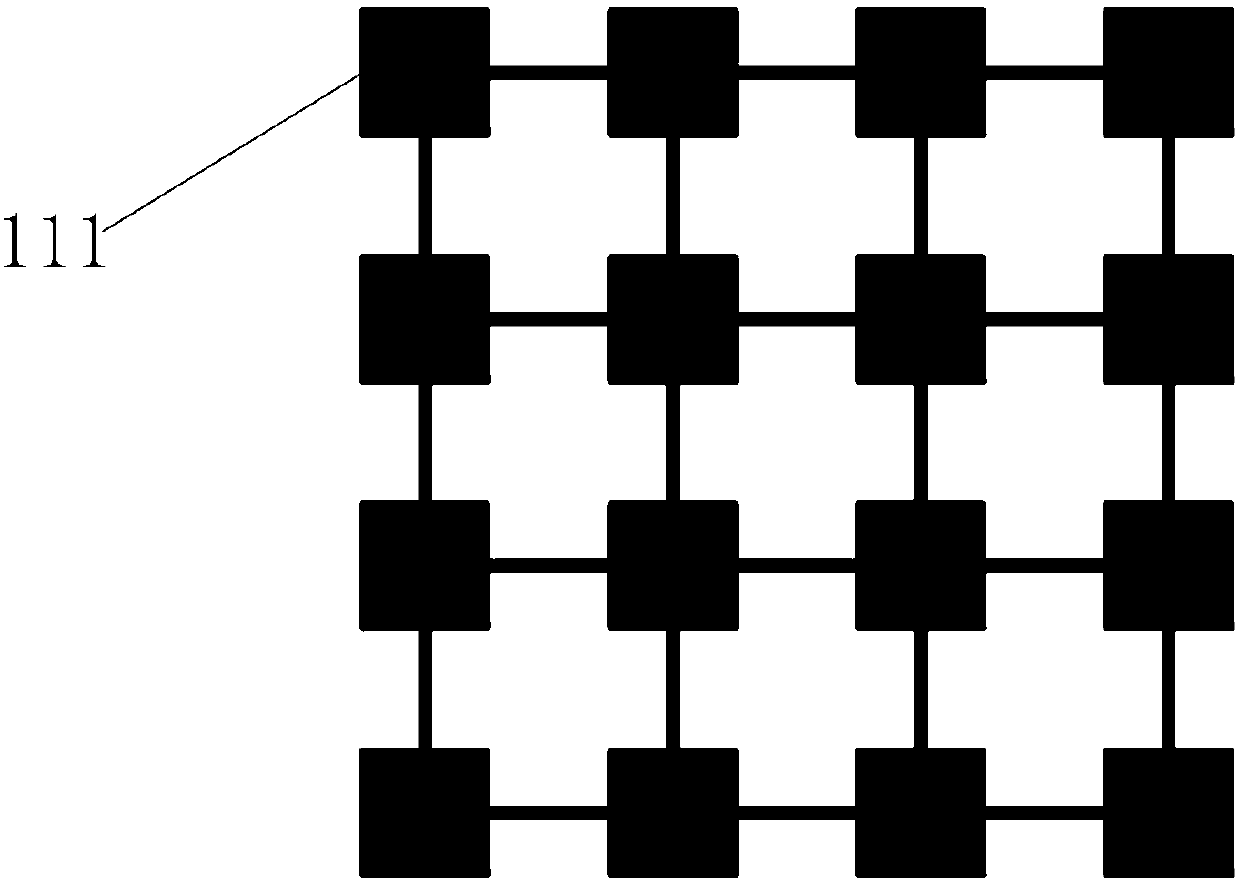

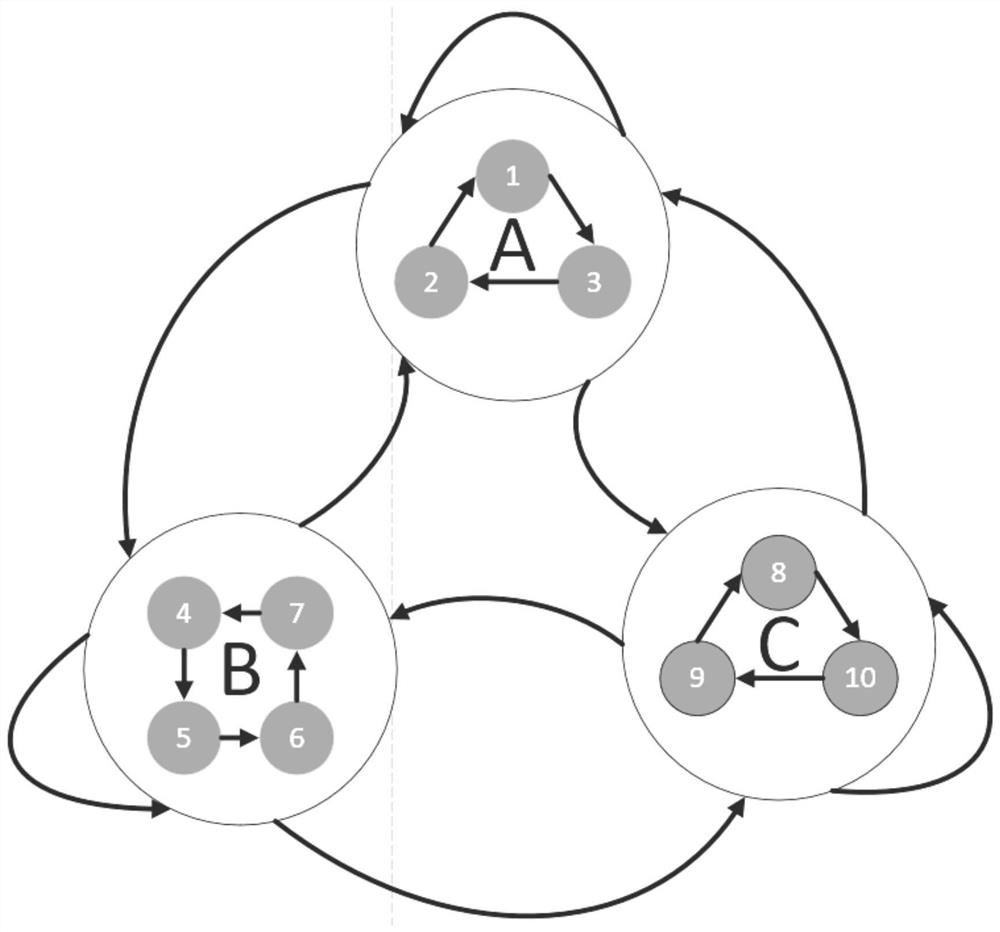

Method of creating core-tile-switch mapping architecture in on-chip bus and computer-readable medium for recording the method

There are provided a method of creating an optimized core-tile-switch mapping architecture in an on-chip bus and a computer-readable recording medium for recording the method. The core-tile-switch mapping architecture creating method includes: creating a core communication graph representing the connection relationship between arbitrary cores; creating a Network-on-chip (NOC) architecture including a plurality of switches, a plurality of tiles, and a plurality of links interconnecting the plurality of switches; and mapping the cores to the tiles using a predetermined optimized mapping method to thereby create the optimized core-tile-switch mapping architecture. The optimized mapping method includes first, second, and third calculating steps. According to the optimized core-tile-switch mapping architecture creating method and the computer-readable recording medium for recording the method, since the hop distance between cores is minimized, it is possible to minimize energy consumption and communication delay time in an on-chip bus. Furthermore, the optimized mapping architecture presents a standard for comparing the optimization of other mapping architectures.

Owner:SAMSUNG ELECTRONICS CO LTD

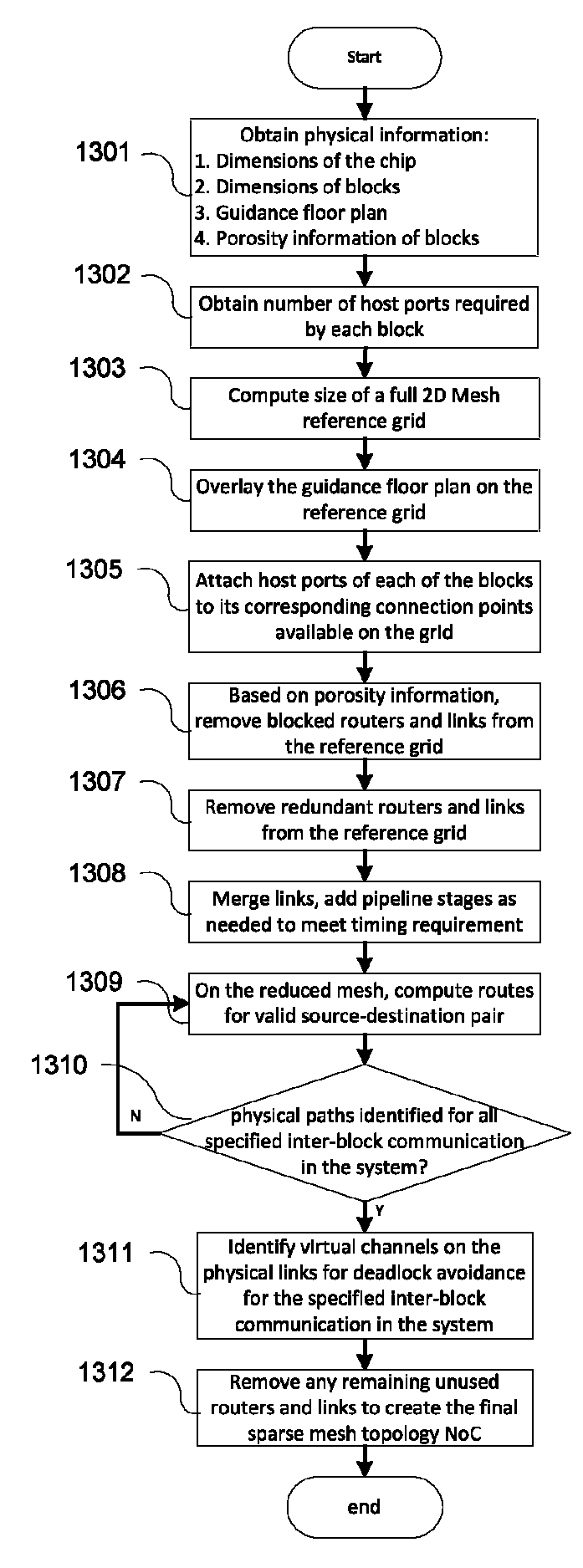

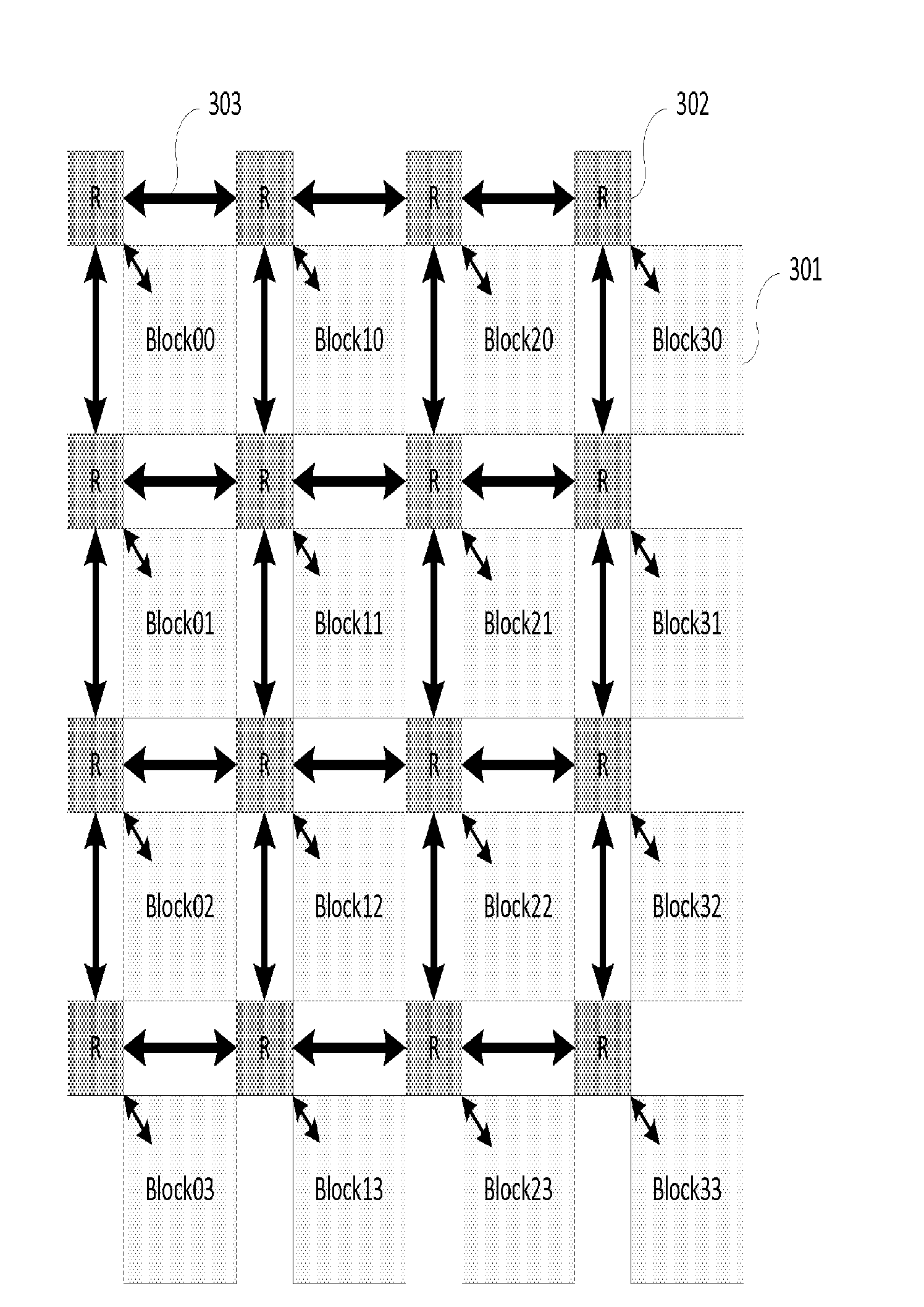

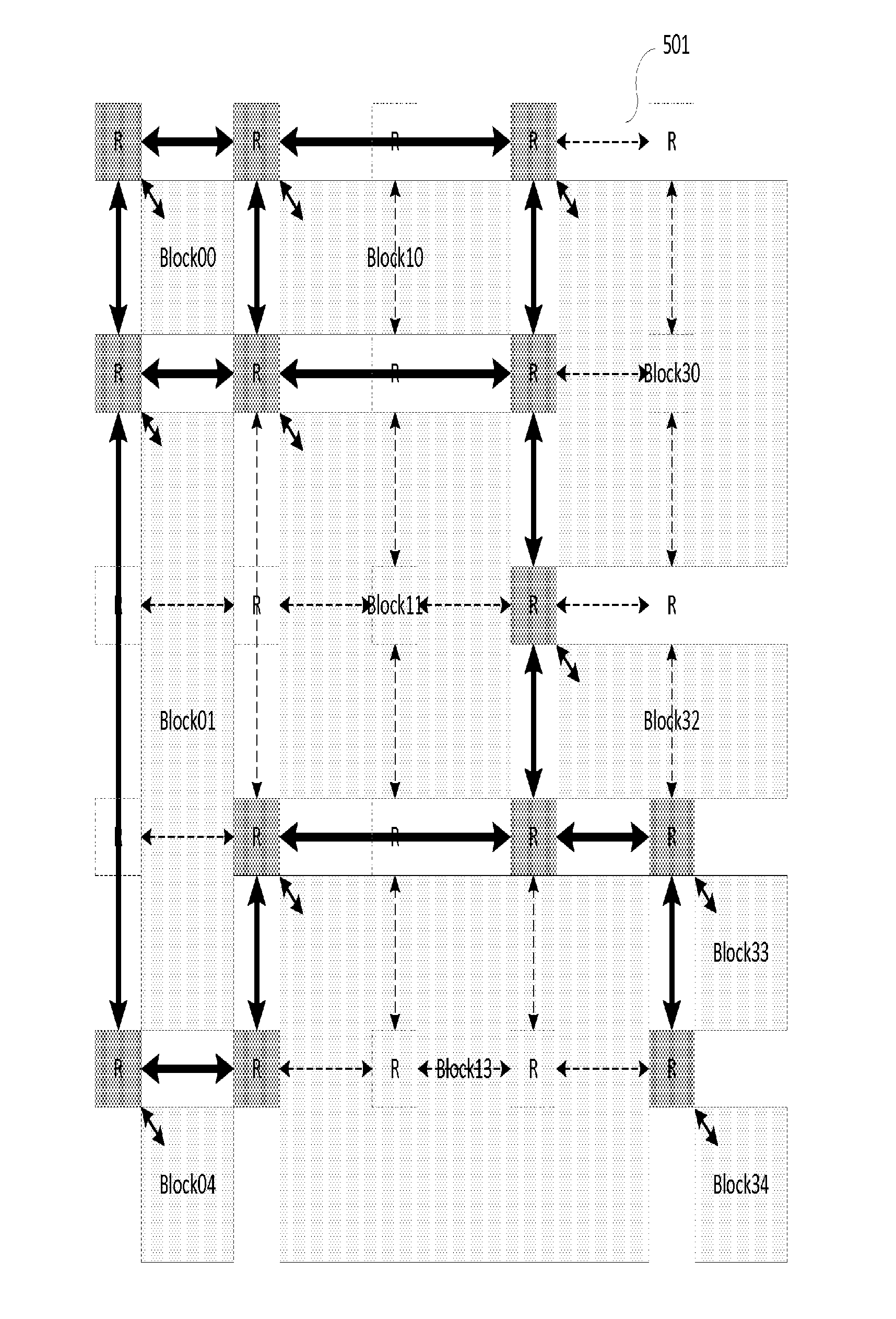

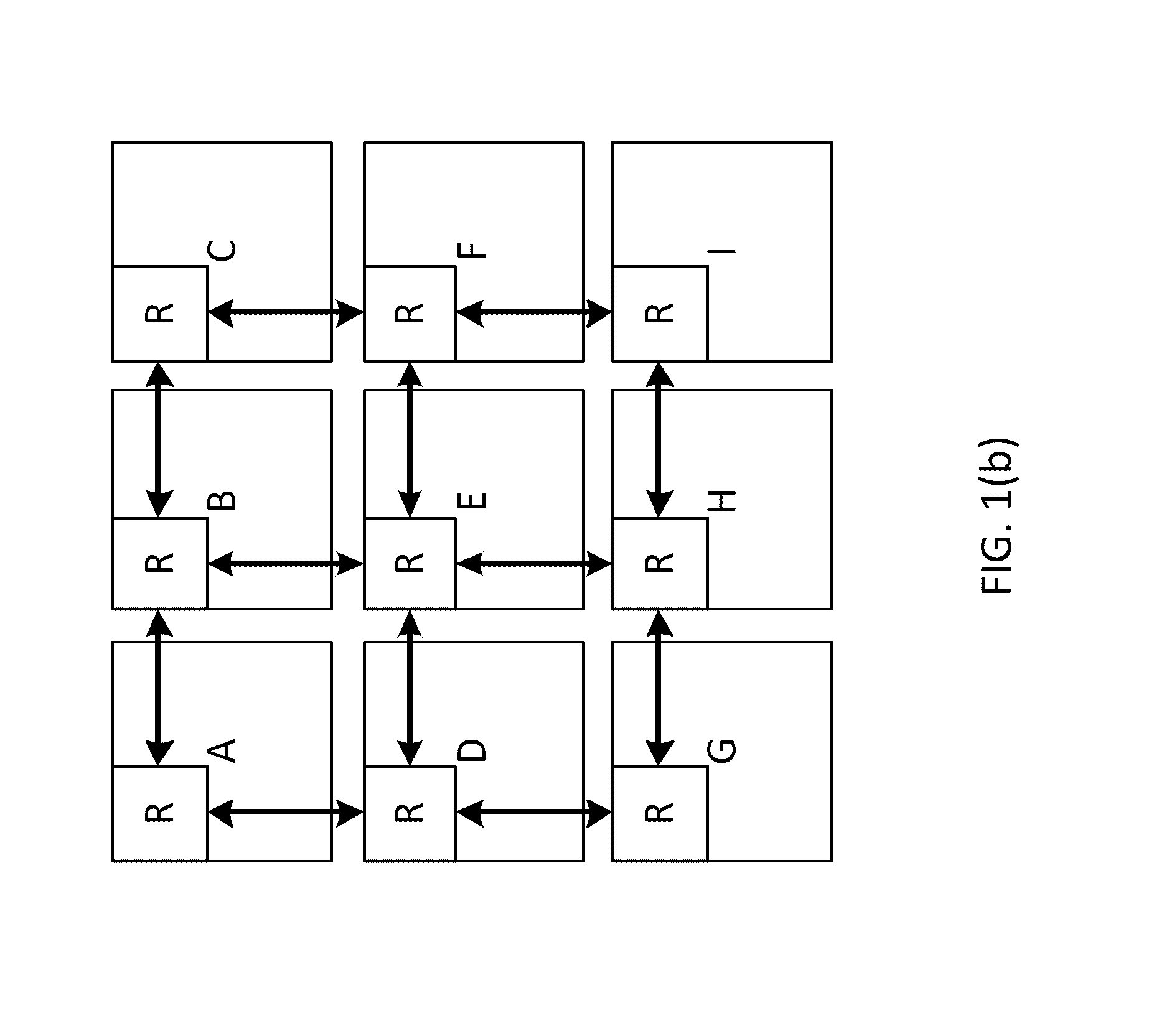

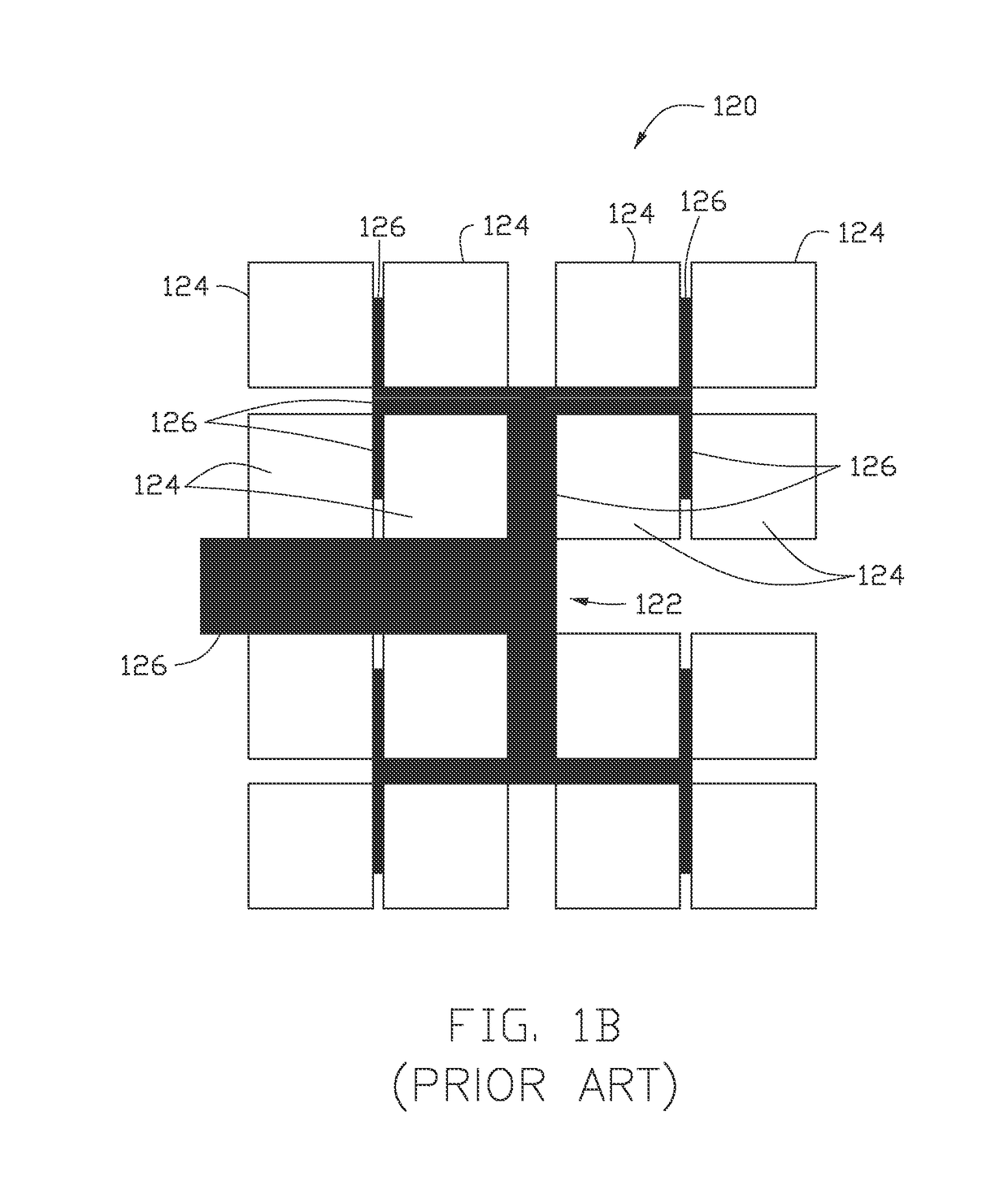

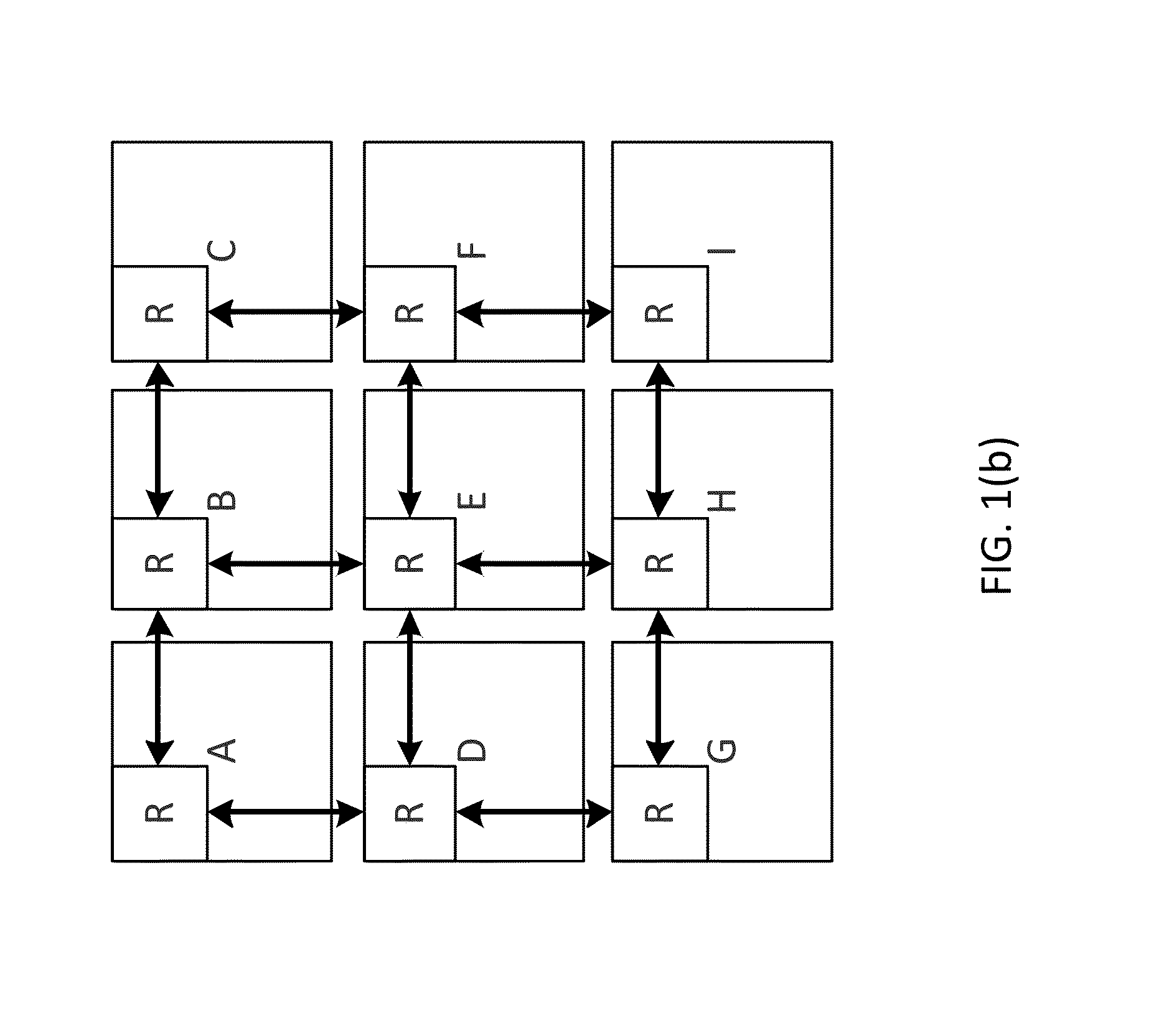

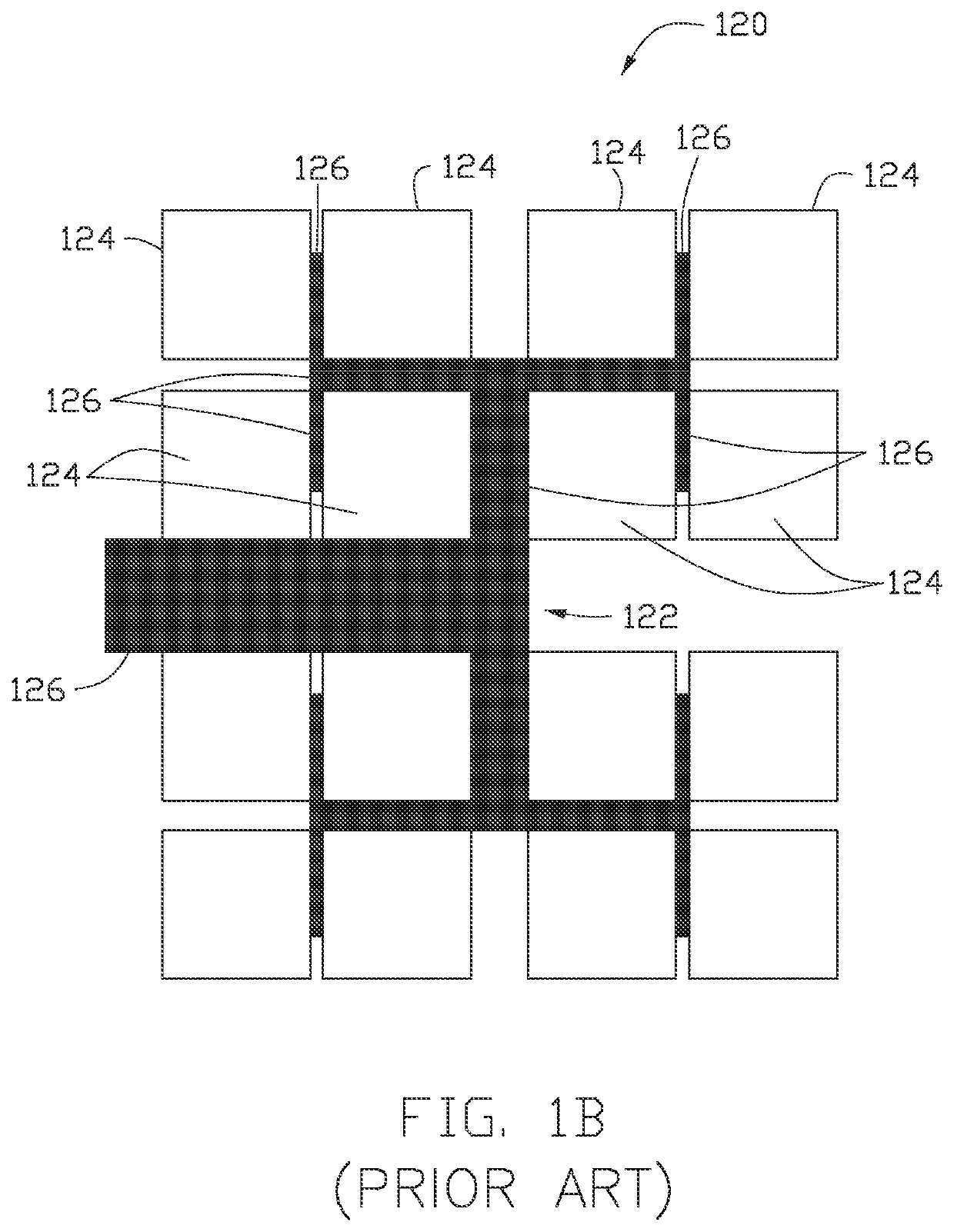

Asymmetric mesh NoC topologies

A method of interconnecting blocks of heterogeneous dimensions using a NoC interconnect with sparse mesh topology includes determining a size of a mesh reference grid based on dimensions of the chip, dimensions of the blocks of heterogeneous dimensions, relative placement of the blocks and a number of host ports required for each of the blocks of heterogeneous dimensions, overlaying the blocks of heterogeneous dimensions on the mesh reference grid based on based on a guidance floor plan for placement of the blocks of heterogeneous dimensions, removing ones of a plurality of nodes and corresponding ones of links to the ones of the plurality of nodes which are blocked by the overlaid blocks of heterogeneous dimensions, based on porosity information of the blocks of heterogeneous dimensions, and mapping inter-block communication of the network-on-chip architecture over remaining ones of the nodes and corresponding remaining ones of the links.

Owner:INTEL CORP

ASYMMETRIC MESH NoC TOPOLOGIES

A method of interconnecting blocks of heterogeneous dimensions using a NoC interconnect with sparse mesh topology includes determining a size of a mesh reference grid based on dimensions of the chip, dimensions of the blocks of heterogeneous dimensions, relative placement of the blocks and a number of host ports required for each of the blocks of heterogeneous dimensions, overlaying the blocks of heterogeneous dimensions on the mesh reference grid based on based on a guidance floor plan for placement of the blocks of heterogeneous dimensions, removing ones of a plurality of nodes and corresponding ones of links to the ones of the plurality of nodes which are blocked by the overlaid blocks of heterogeneous dimensions, based on porosity information of the blocks of heterogeneous dimensions, and mapping inter-block communication of the network-on-chip architecture over remaining ones of the nodes and corresponding remaining ones of the links.

Owner:INTEL CORP

ASYMMETRIC MESH NoC TOPOLOGIES

A method of interconnecting blocks of heterogeneous dimensions using a NoC interconnect with sparse mesh topology includes determining a size of a mesh reference grid based on dimensions of the chip, dimensions of the blocks of heterogeneous dimensions, relative placement of the blocks and a number of host ports required for each of the blocks of heterogeneous dimensions, overlaying the blocks of heterogeneous dimensions on the mesh reference grid based on based on a guidance floor plan for placement of the blocks of heterogeneous dimensions, removing ones of a plurality of nodes and corresponding ones of links to the ones of the plurality of nodes which are blocked by the overlaid blocks of heterogeneous dimensions, based on porosity information of the blocks of heterogeneous dimensions, and mapping inter-block communication of the network-on-chip architecture over remaining ones of the nodes and corresponding remaining ones of the links.

Owner:INTEL CORP

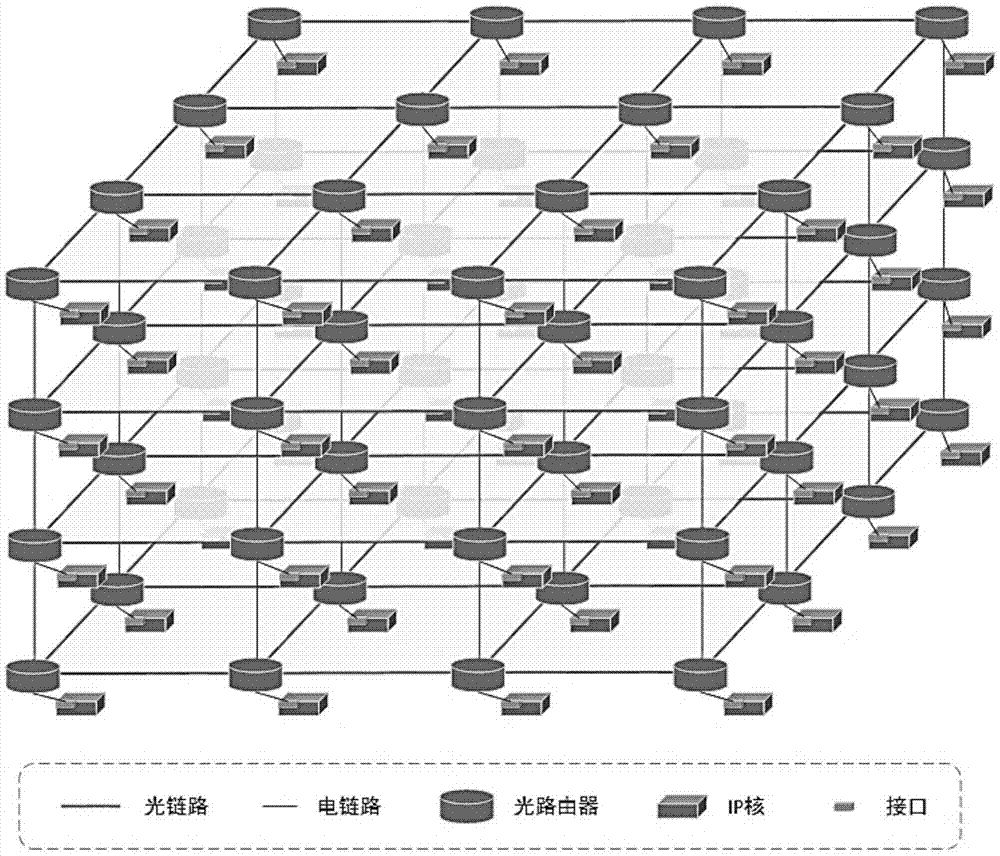

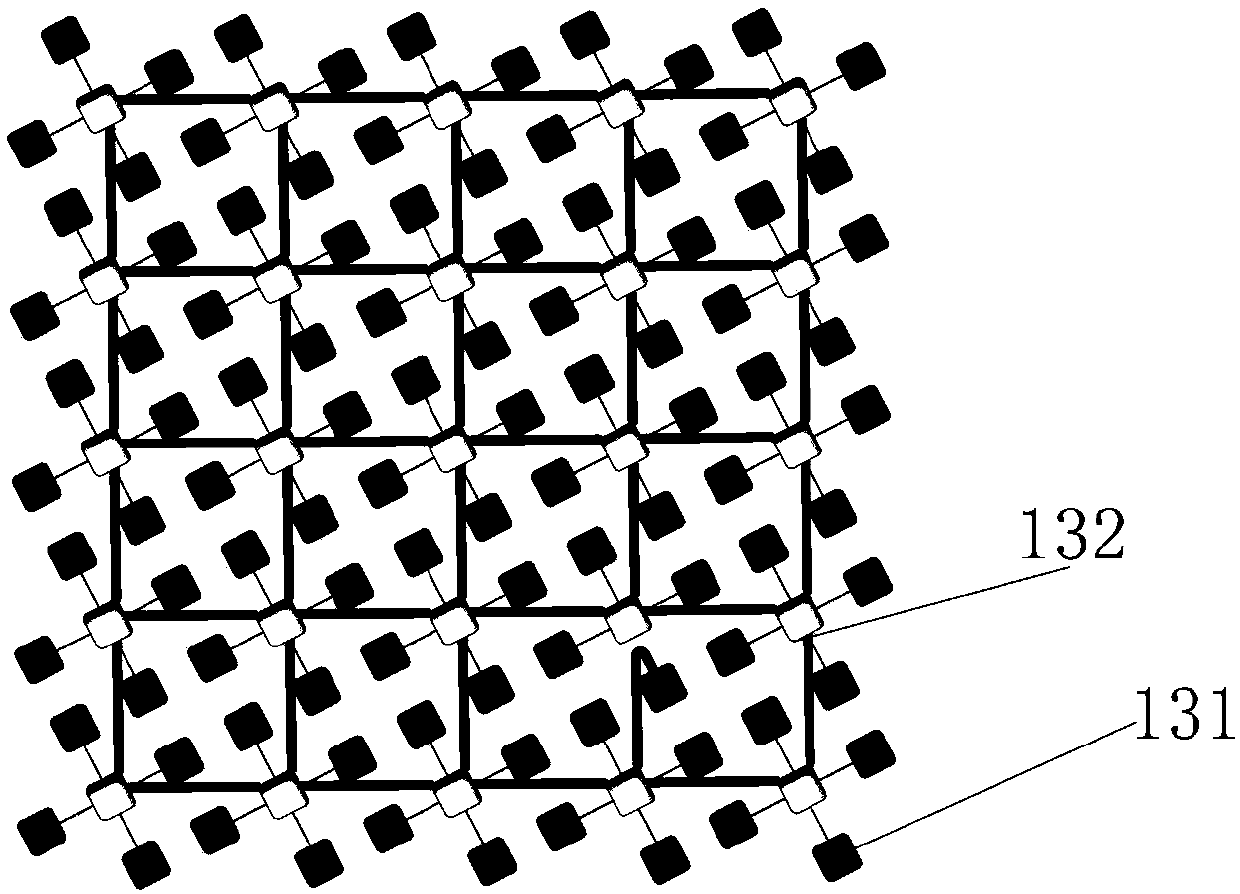

Method for constructing network on three-dimensional chip

InactiveCN101483614AImprove performanceSmall diameterData switching networksVertical planeRound complexity

The invention provides a three-dimensional network on chip (NoC) structuring method by using a horizontal-plane network structure and a flexible imaginary-plane network structure, wherein, the horizontal-plane network of which the network topology adopts a De Bruijn picture is a plane extending along the X direction and the Y direction; while the imaginary-plane network is a curved surface extending along the three directions of X, Y and Z, the network can be formed by connecting certain nodes of each layer of the horizontal-plane network according to the requirement for solving certain problems such as reducing the wiring complexity or improving the fault-tolerant character, namely, the nodes are not necessarily in a vertical plane. The invention also provides two kinds of imaginary-plane structuring methods comprising a De Bruijn picture structure and a double-ring structure. The first method fully utilizing that the De Bruijn picture allows shorter routing algorithm reduces average hop times in the data transmission, provides a small network delay and has a better fault-tolerant character; the second method improves the transmission efficiency by using the characteristics of low wiring complexity of a ring structure and high data transmission speed and by combining the horizontal-plane network utilizing the advantage of small network diameter of the De Bruijn picture.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

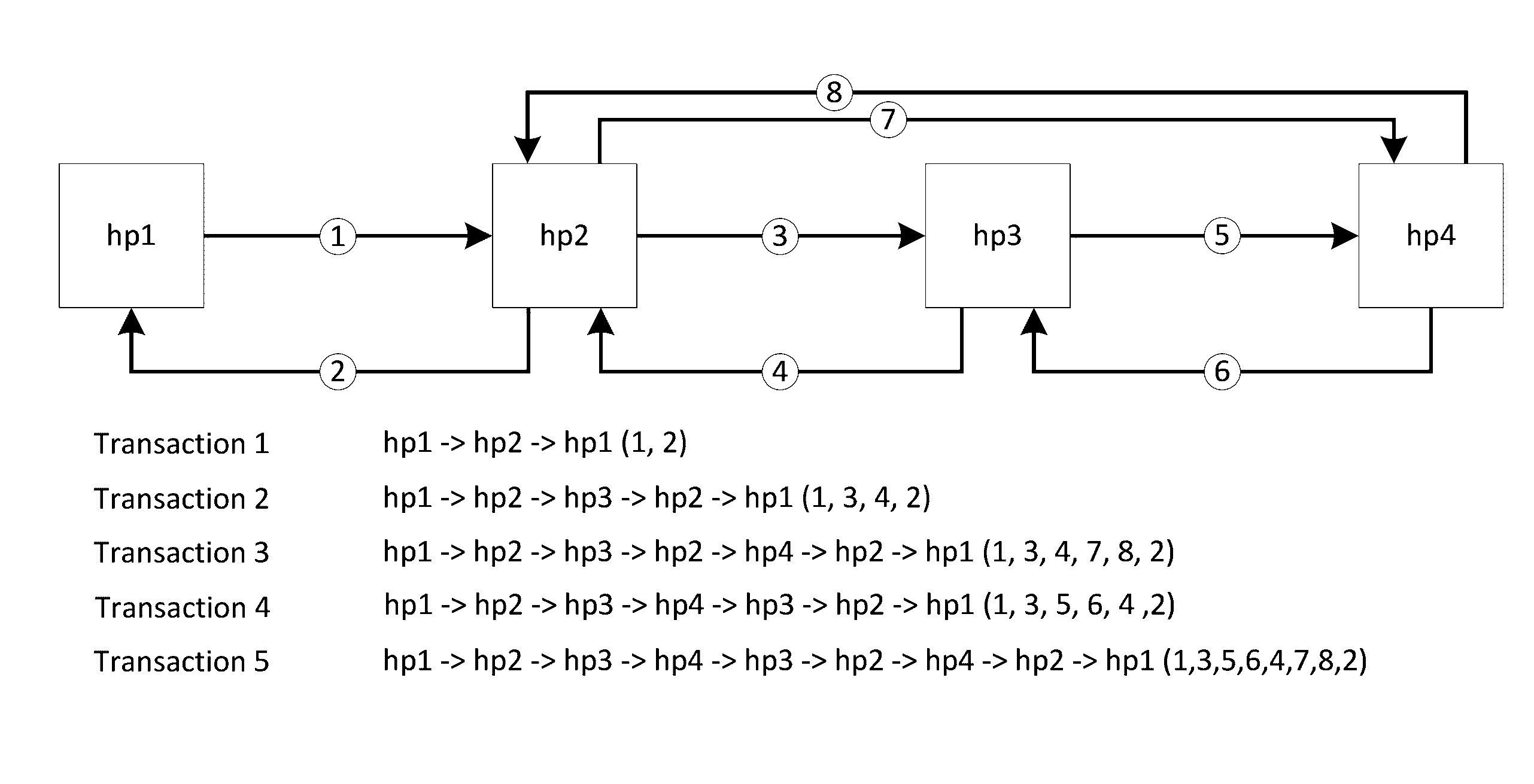

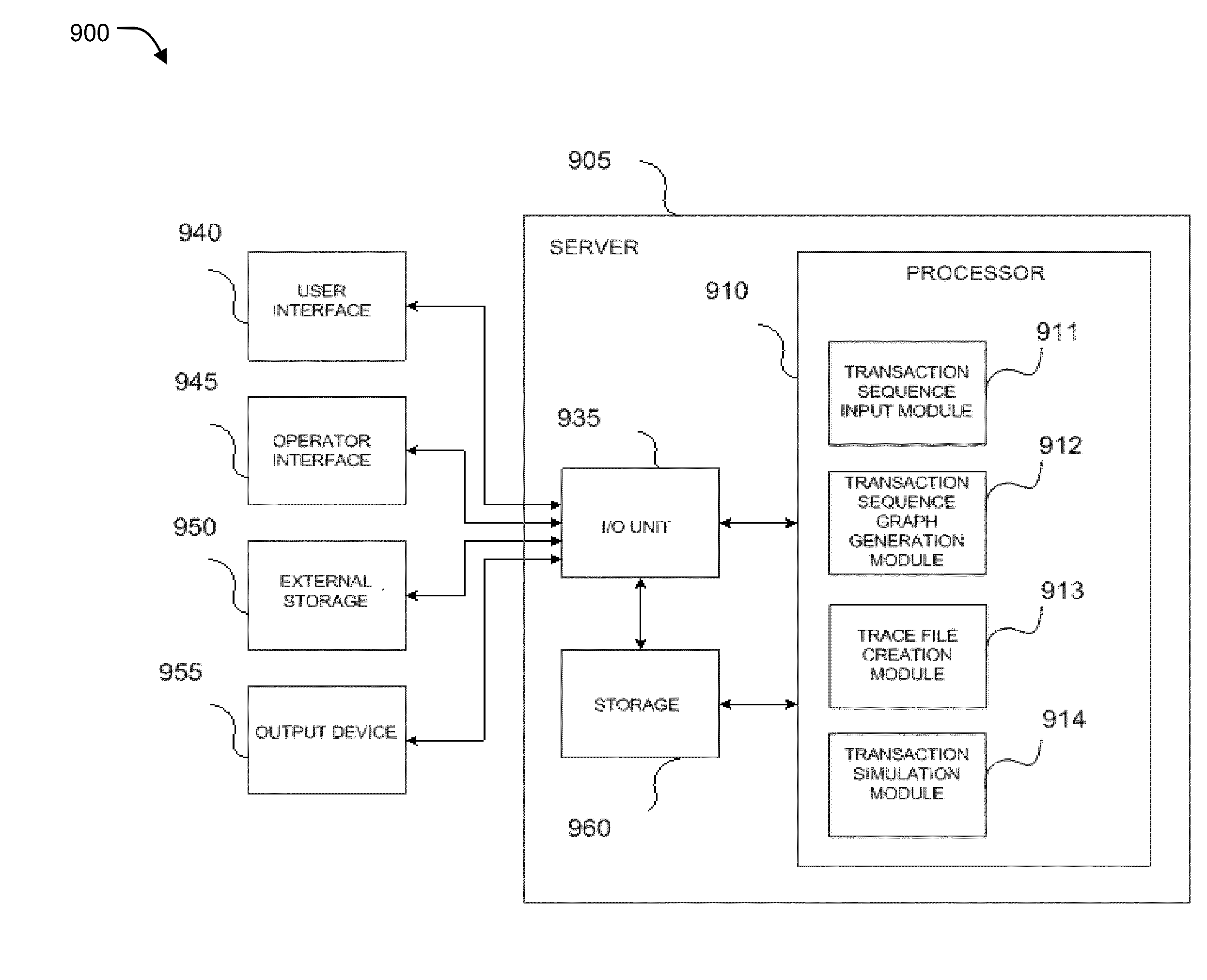

System level simulation in network on chip architecture

ActiveUS9471726B2Design optimisation/simulationCAD circuit designSystem-level simulationParallel computing

Systems and methods for performing multi-message transaction based performance simulations of SoC IP cores within a Network on Chip (NoC) interconnect architecture by accurately imitating full SoC behavior are described. The example implementations involve simulations to evaluate and detect NoC behavior based on execution of multiple transactions at different rates / times / intervals, wherein each transaction can contain one or more messages, with each message being associated with a source agent and a destination agent. Each message can also be associated with multiple parameters such as rate, size, value, latency, among other like parameters that can be configured to indicate the execution of the transaction by a simulator to simulate a real-time scenario for generating performance reports for the NoC interconnect.

Owner:INTEL CORP

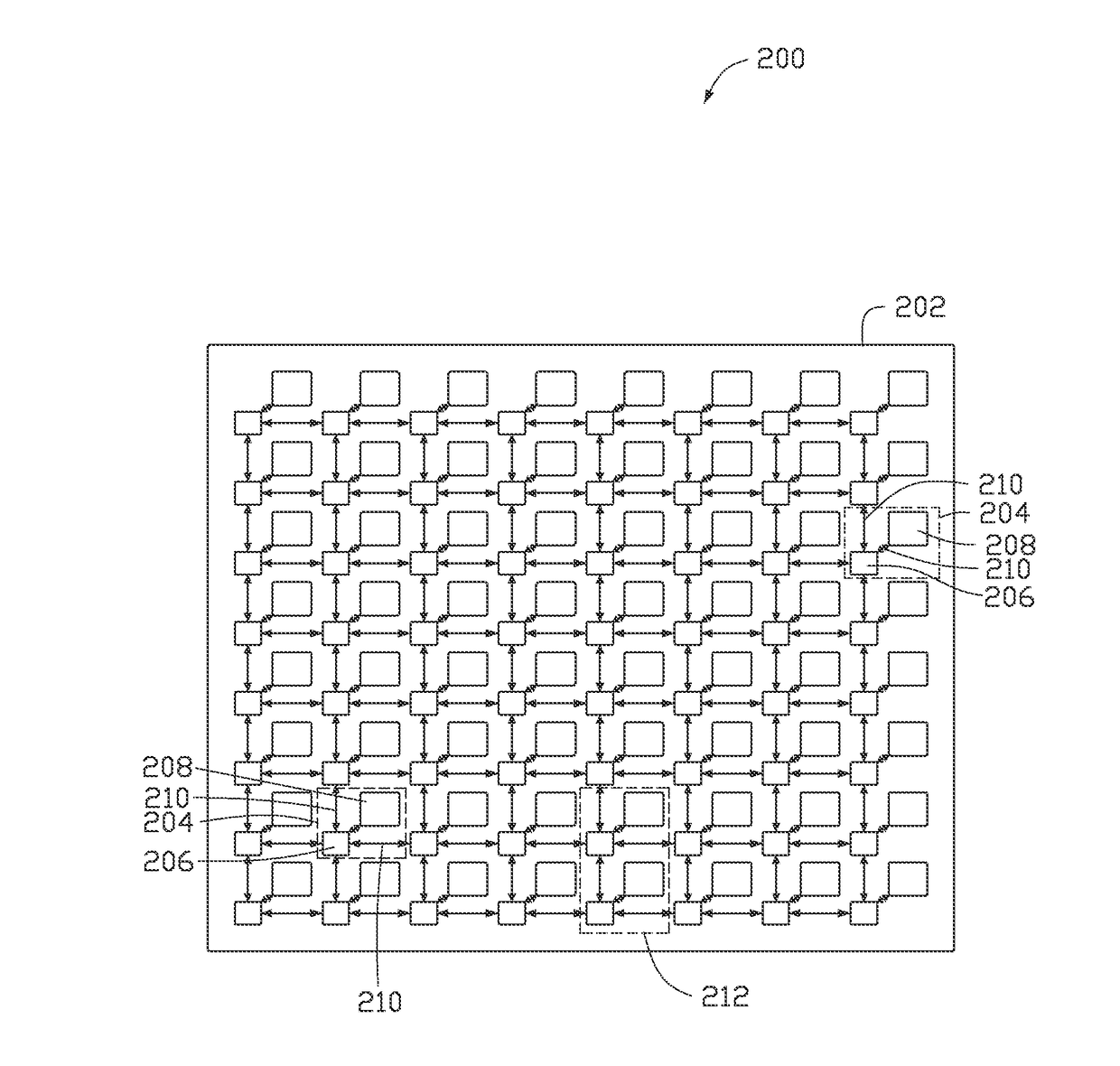

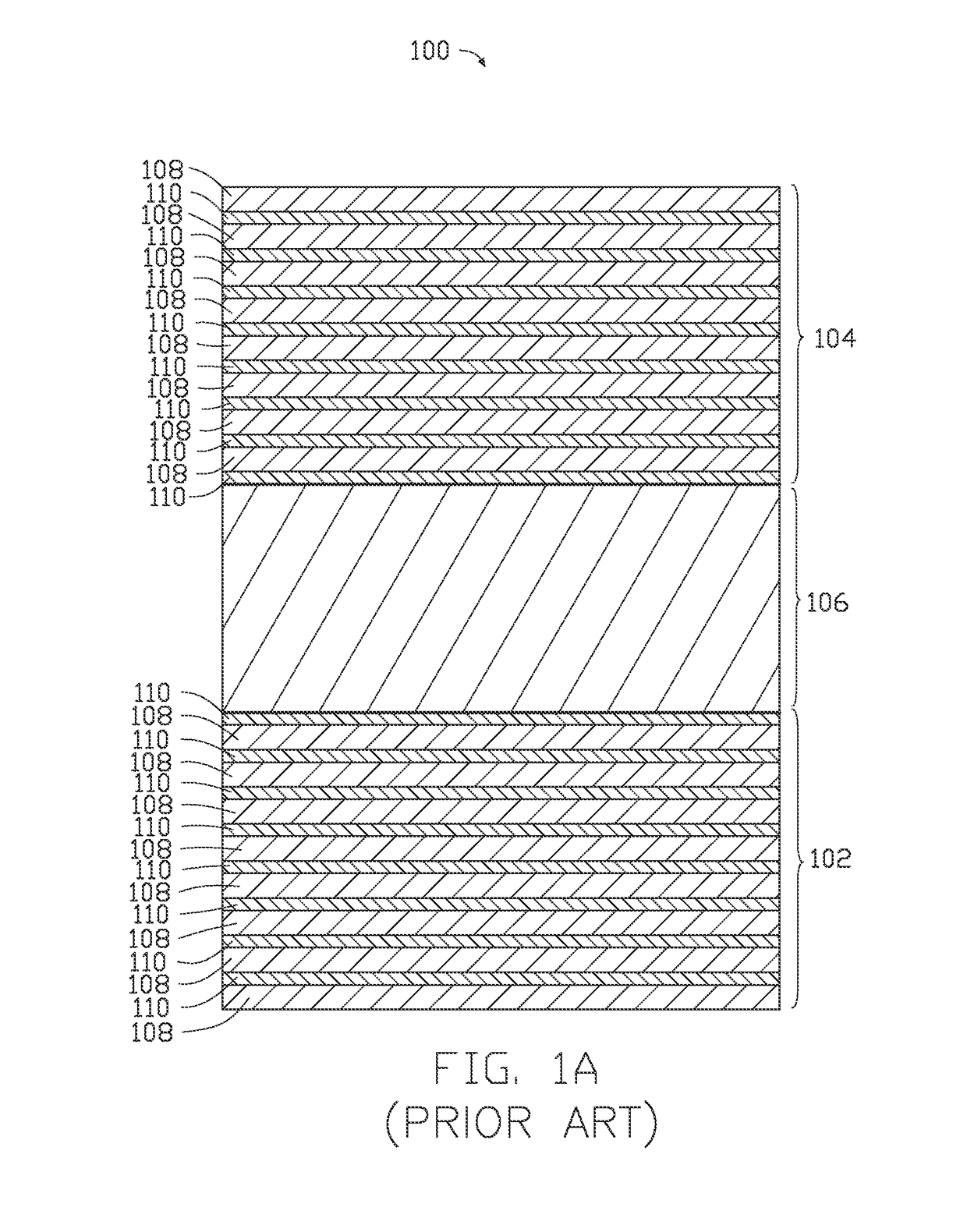

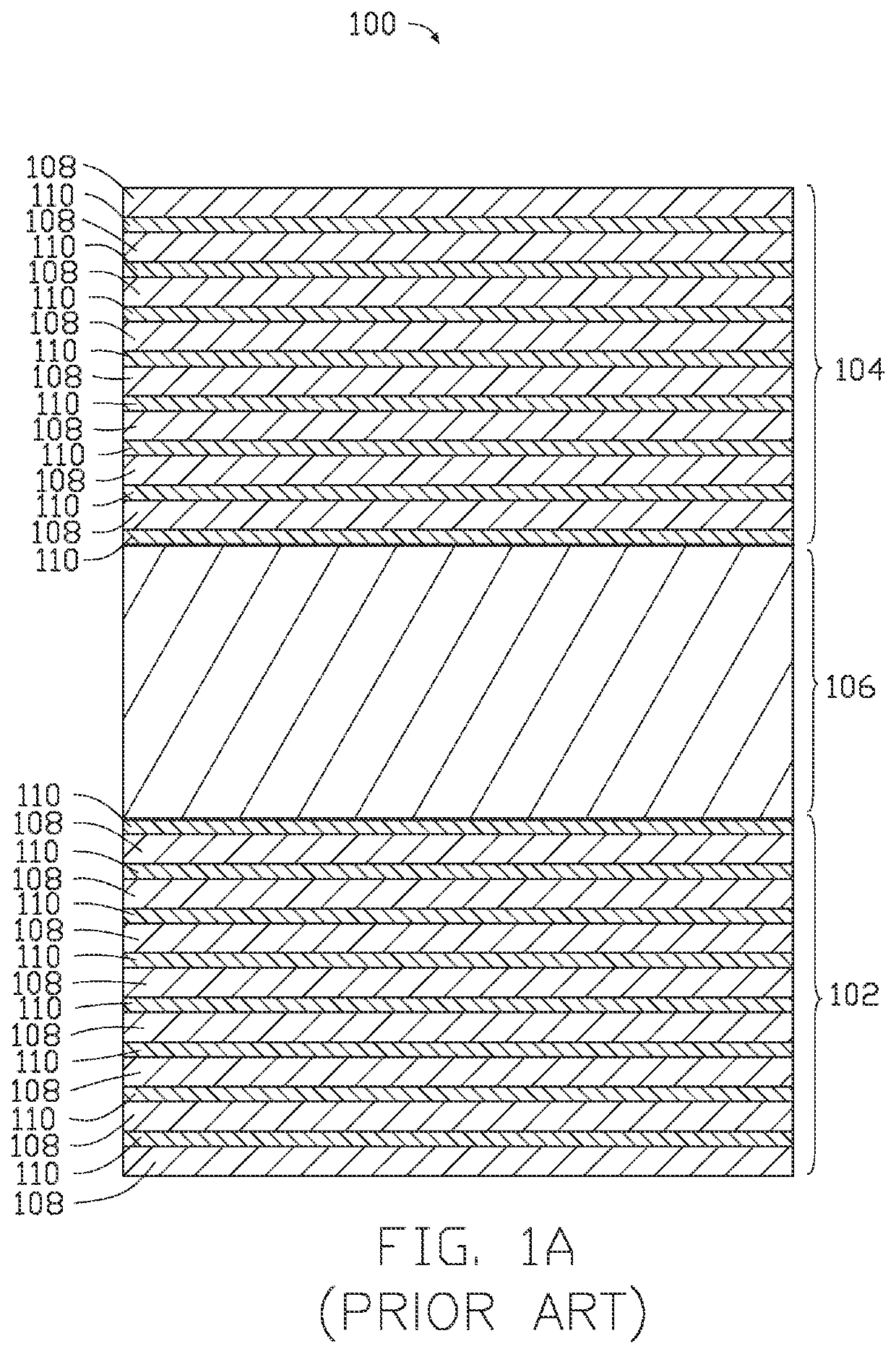

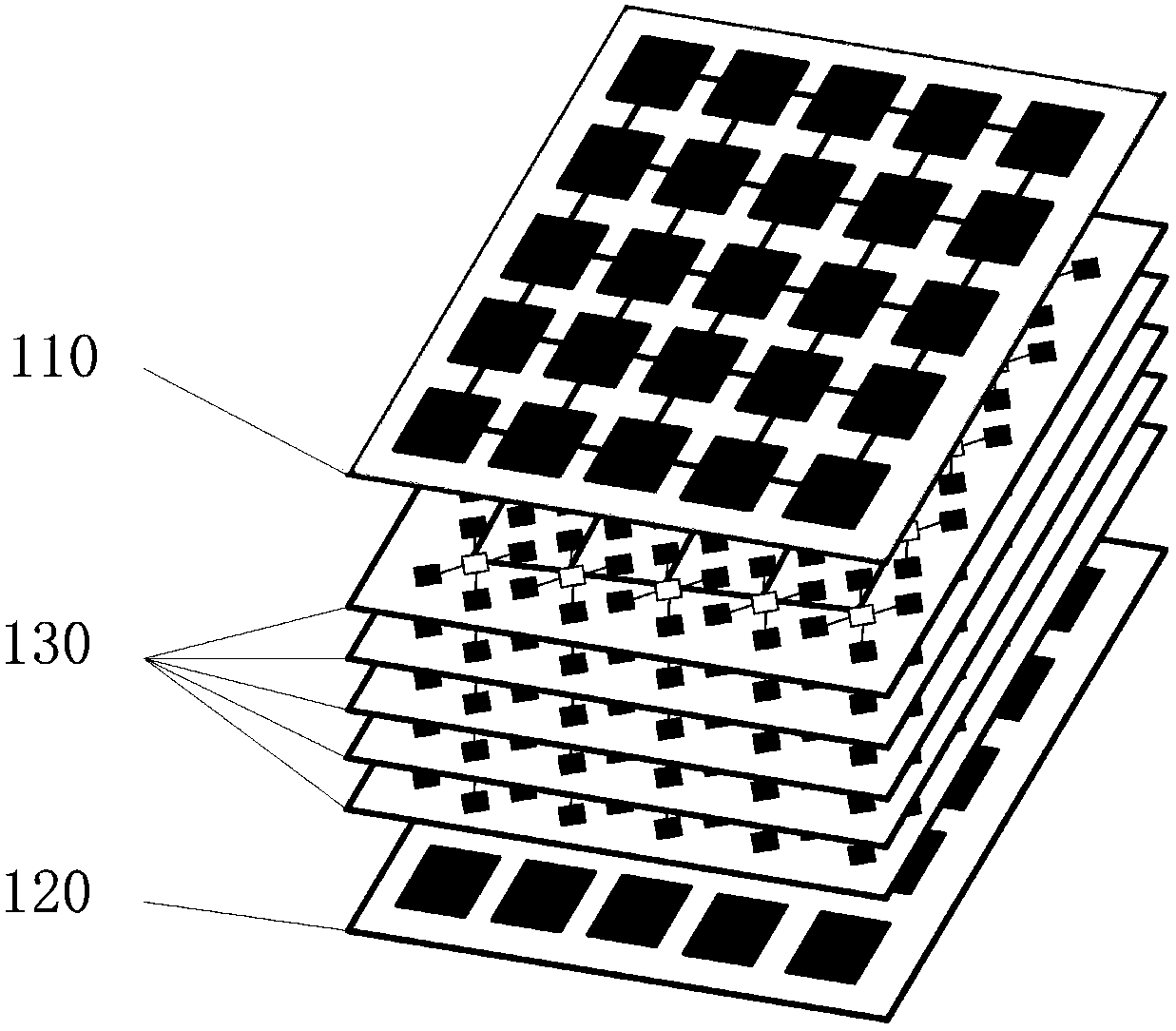

Fabric interconnection for memory banks based on network-on-chip methodology

ActiveUS20170118139A1Lower latencyImprove signal integrityInput/output to record carriersData switching networksParallel computingNetwork on chip architecture

Embodiments disclosed herein generally relate to the use of Network-on-Chip architecture for solid state memory structures, both volatile and non-volatile, which provide for the access of memory storage blocks via a router. As such, data may be sent to and / or from the memory storage blocks as data packets on the chip. The Network-on-Chip architecture may further be utilized to interconnect unlimited numbers of memory cell matrices, spread on a die, thus allowing for reduced latencies among matrices, selective power control, unlimited memory density growth without major latency penalties, and reduced parasitic capacitance and resistance. Other benefits may include improved signal integrity, larger die areas available to implement memory arrays, and higher frequency of operation.

Owner:WESTERN DIGITAL TECH INC

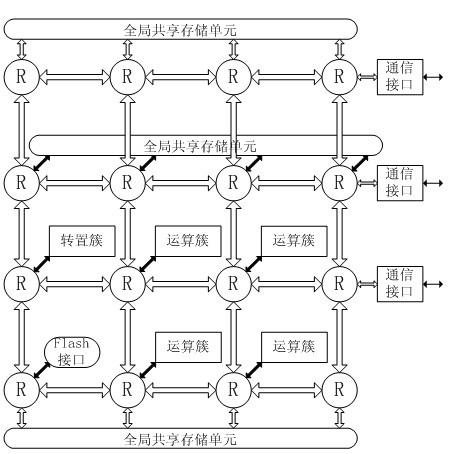

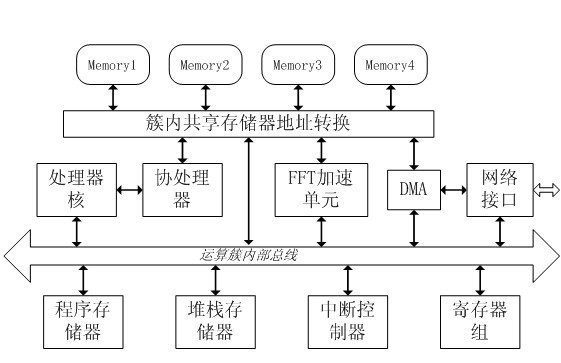

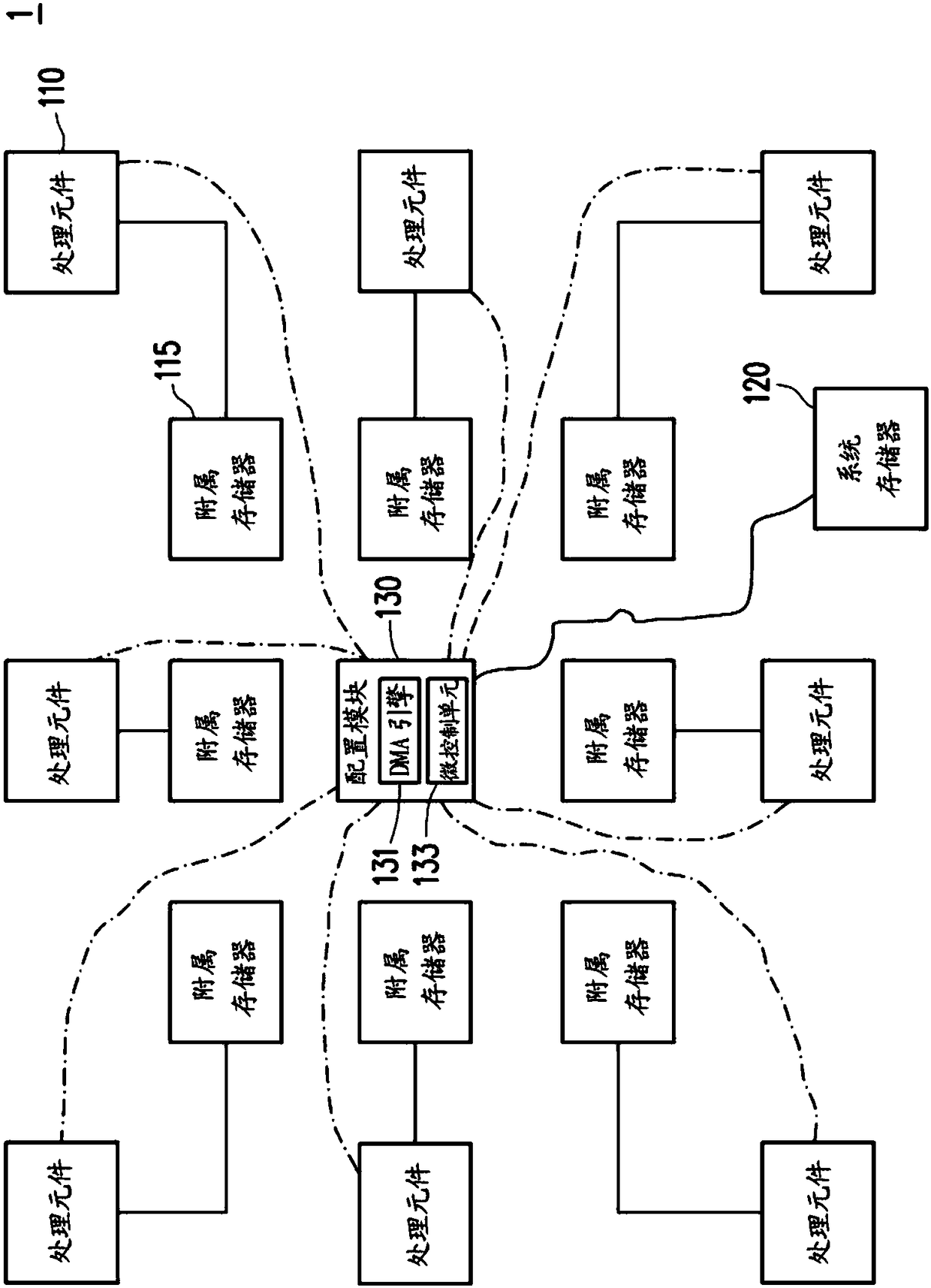

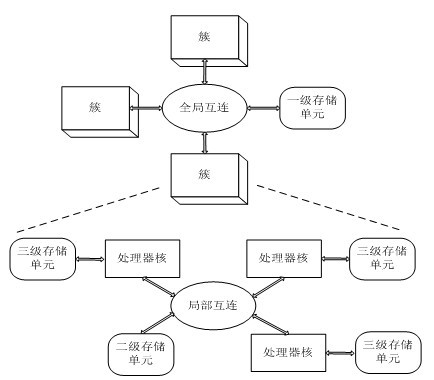

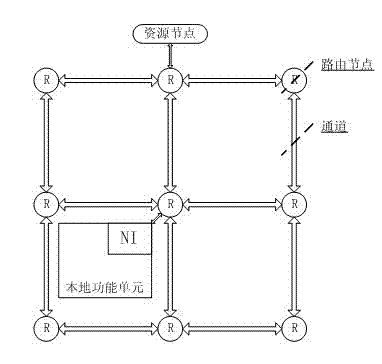

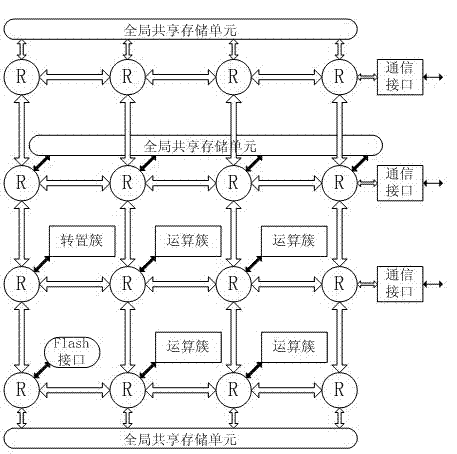

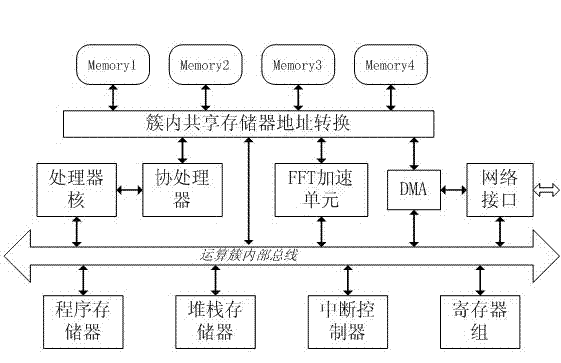

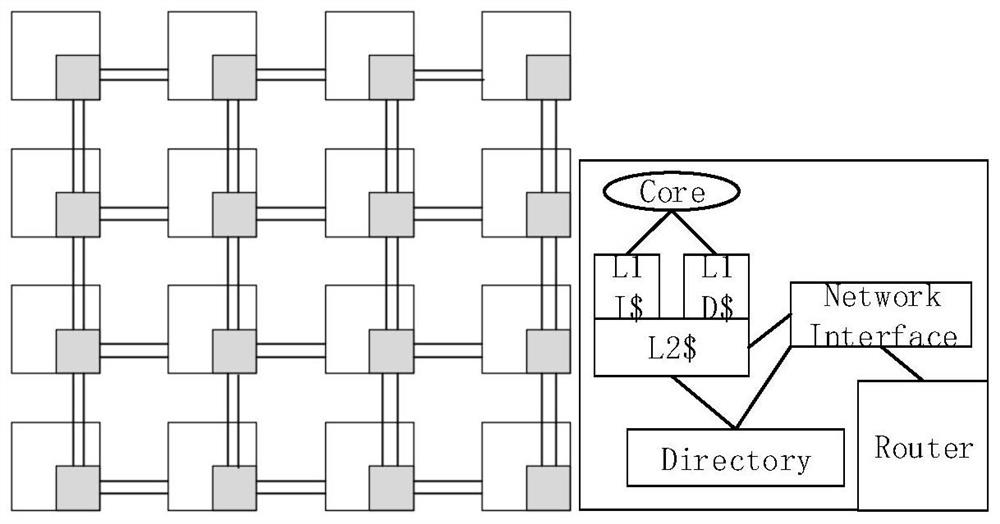

Intensive operation-oriented hierarchical heterogeneous multi-core on-chip network architecture

ActiveCN102497411ATake full advantage of parallel communication performanceGuaranteed transmission speedTransmissionCommunication interfaceDirect memory access

The invention discloses an intensive operation-oriented hierarchical heterogeneous multi-core on-chip network architecture. The top layer of the architecture is integrated with multiple operation clusters, a transposition cluster, a communication interface and a global sharing storage unit by use of a two-dimensional grid on-chip network; a bus architecture is adopted in the operation clusters and the transposition cluster on the bottom layer; the internal bus of each operation cluster is integrated with various operation units and direct memory access, a network interface and an in-cluster sharing storage unit; and the internal bus of the transposition cluster is integrated with a processor core, direct memory access, a network interface and an in-cluster sharing storage unit. The architecture disclosed by the invention can support multiple groups of global sharing storage units which are independent from each other; each global sharing storage unit can be integrated to the on-chip network through multiple network interfaces; the in-cluster sharing storage units are distributed in the operation clusters and the transposition cluster; and the sharing storage units in the operation clusters are divided into multiple groups independent from each other. According to the invention, the communication performance, data processing capability and access bandwidth of the system can be effectively improved through the hierarchical multi-level architecture and multi-channel access.

Owner:NANJING UNIV

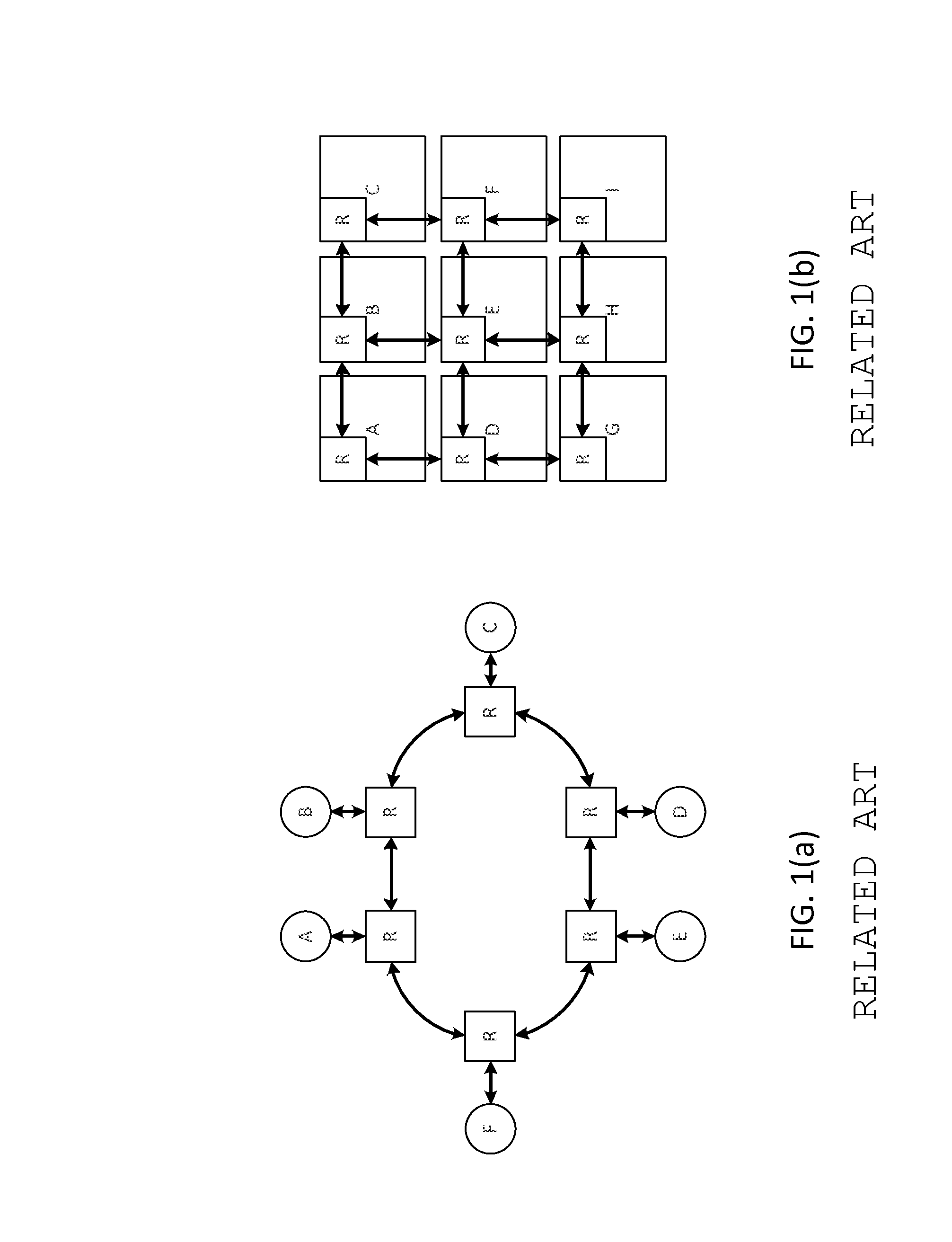

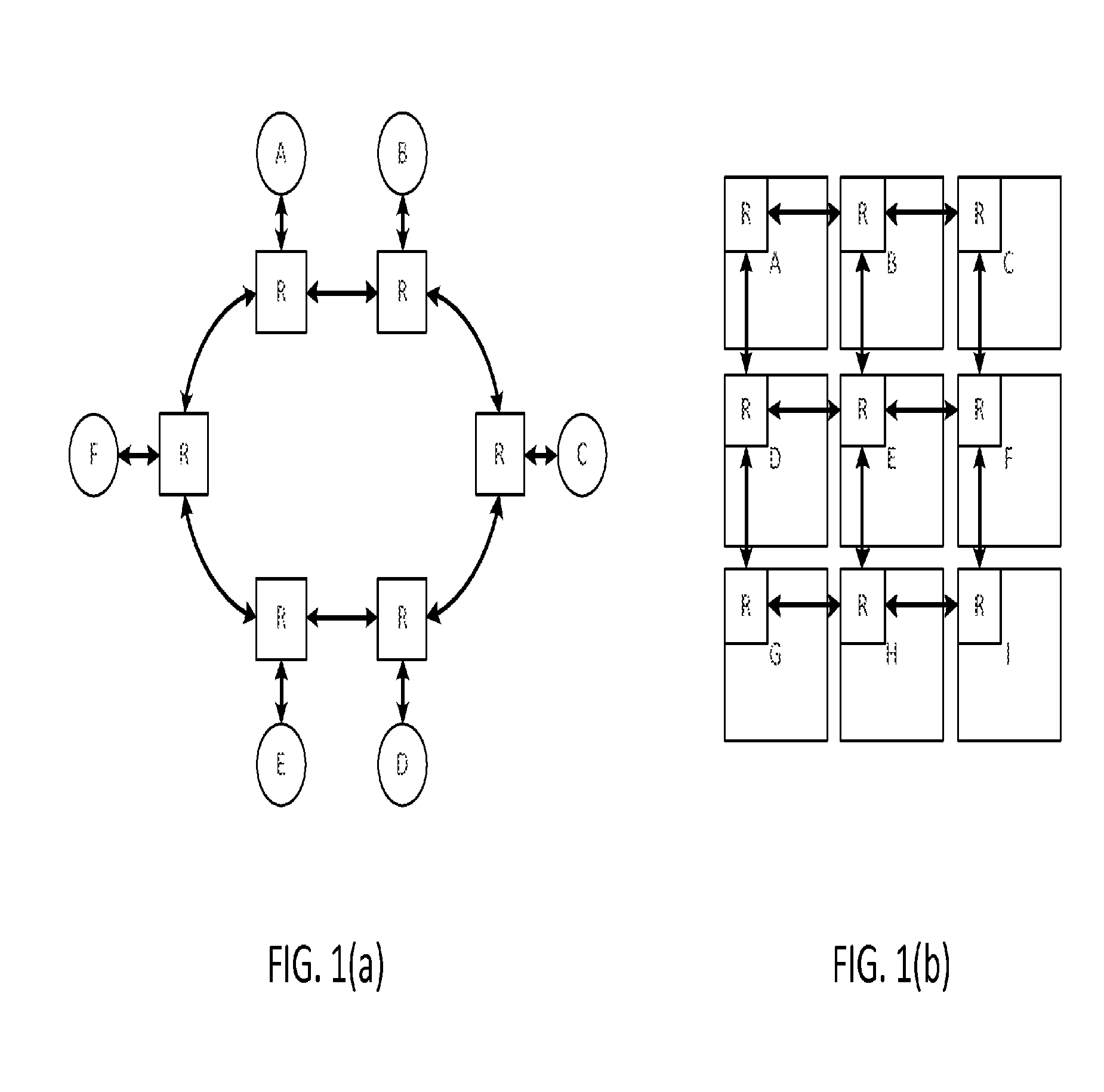

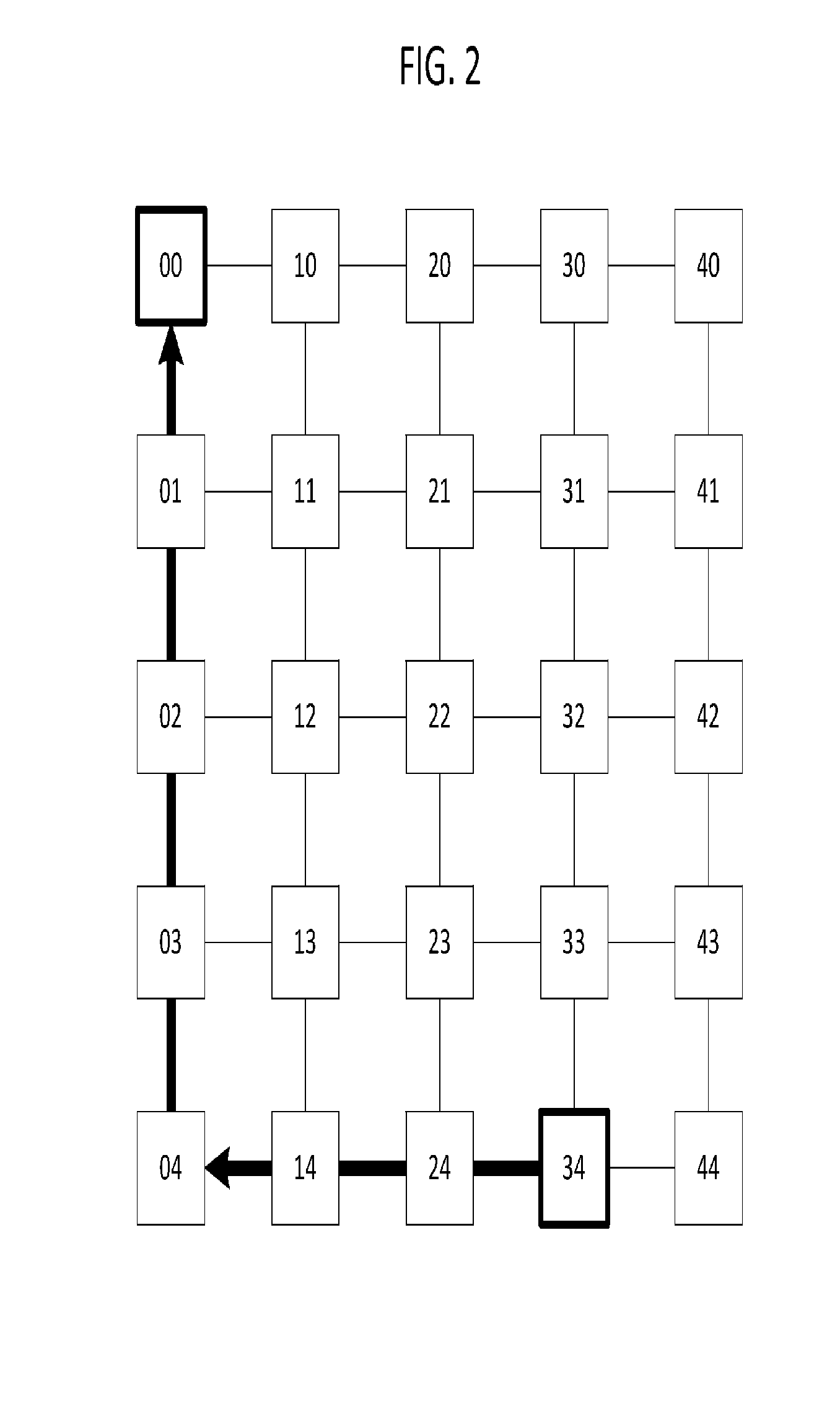

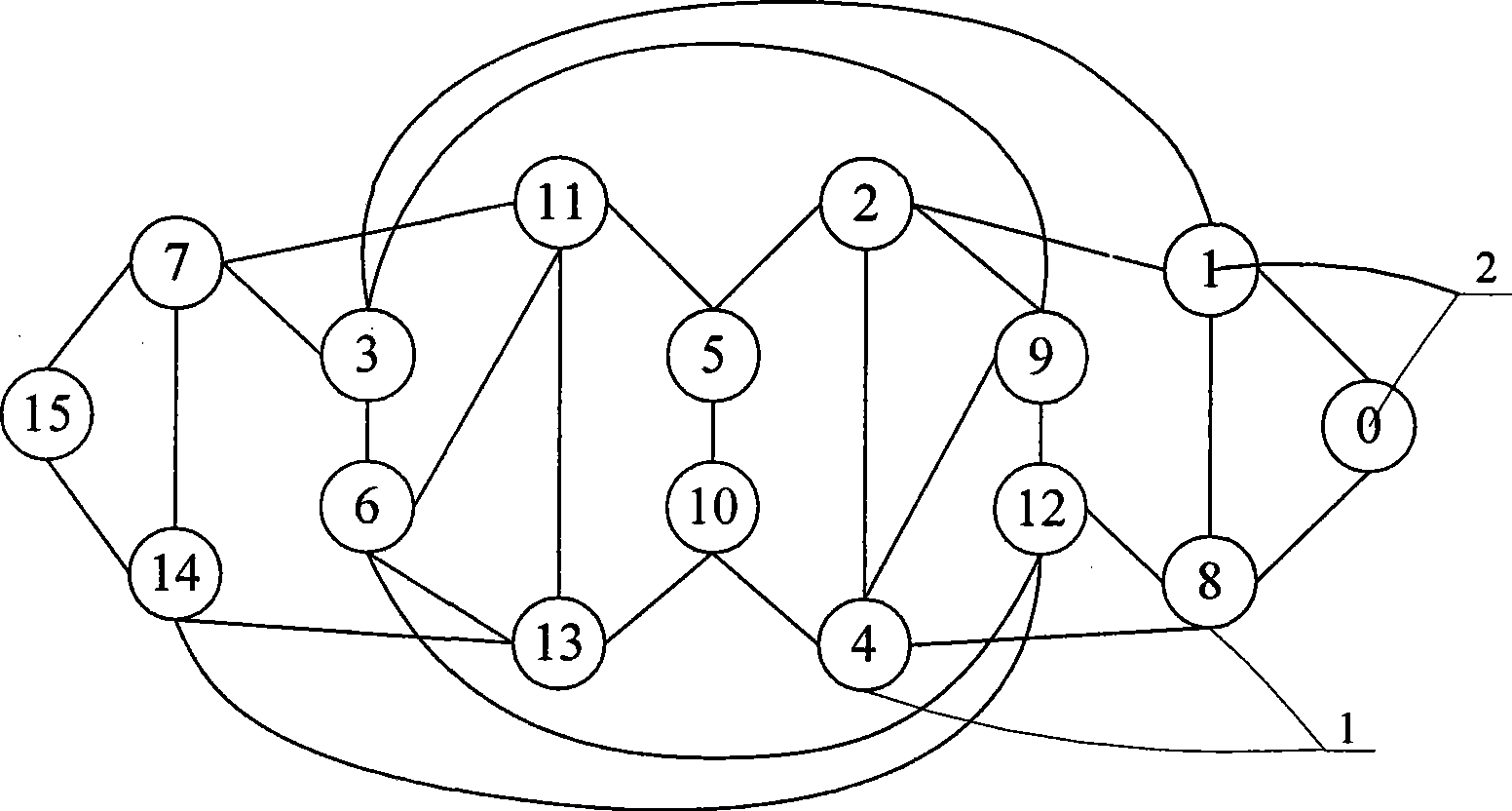

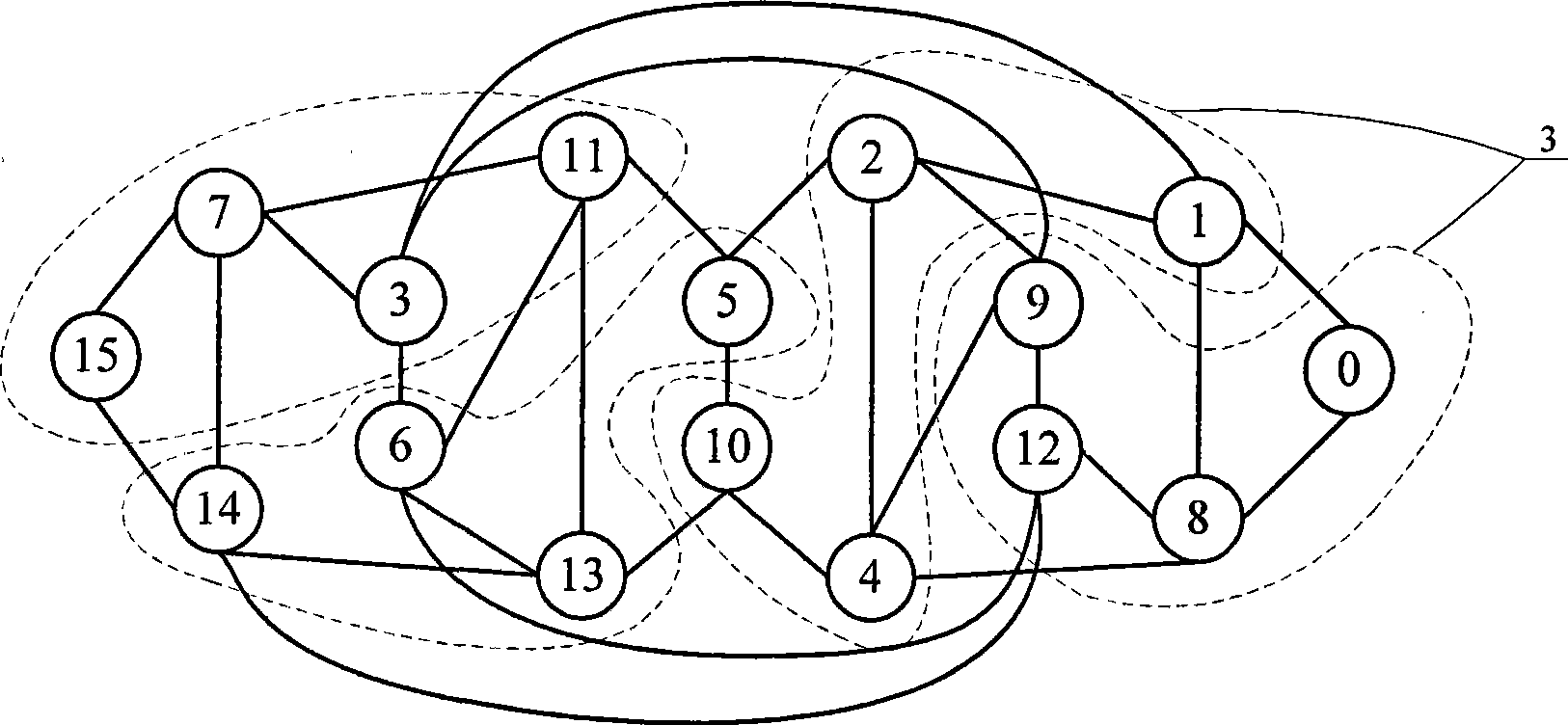

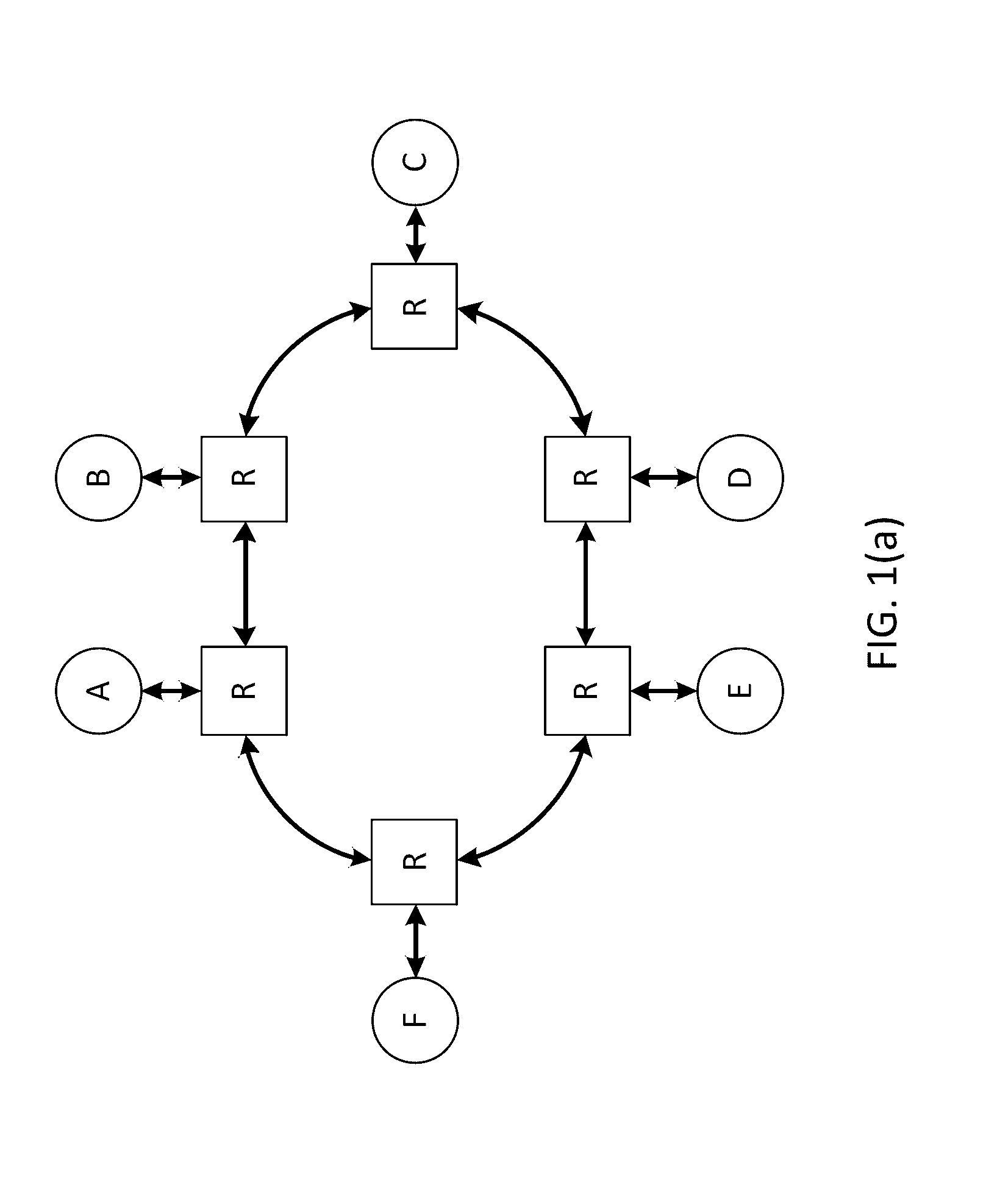

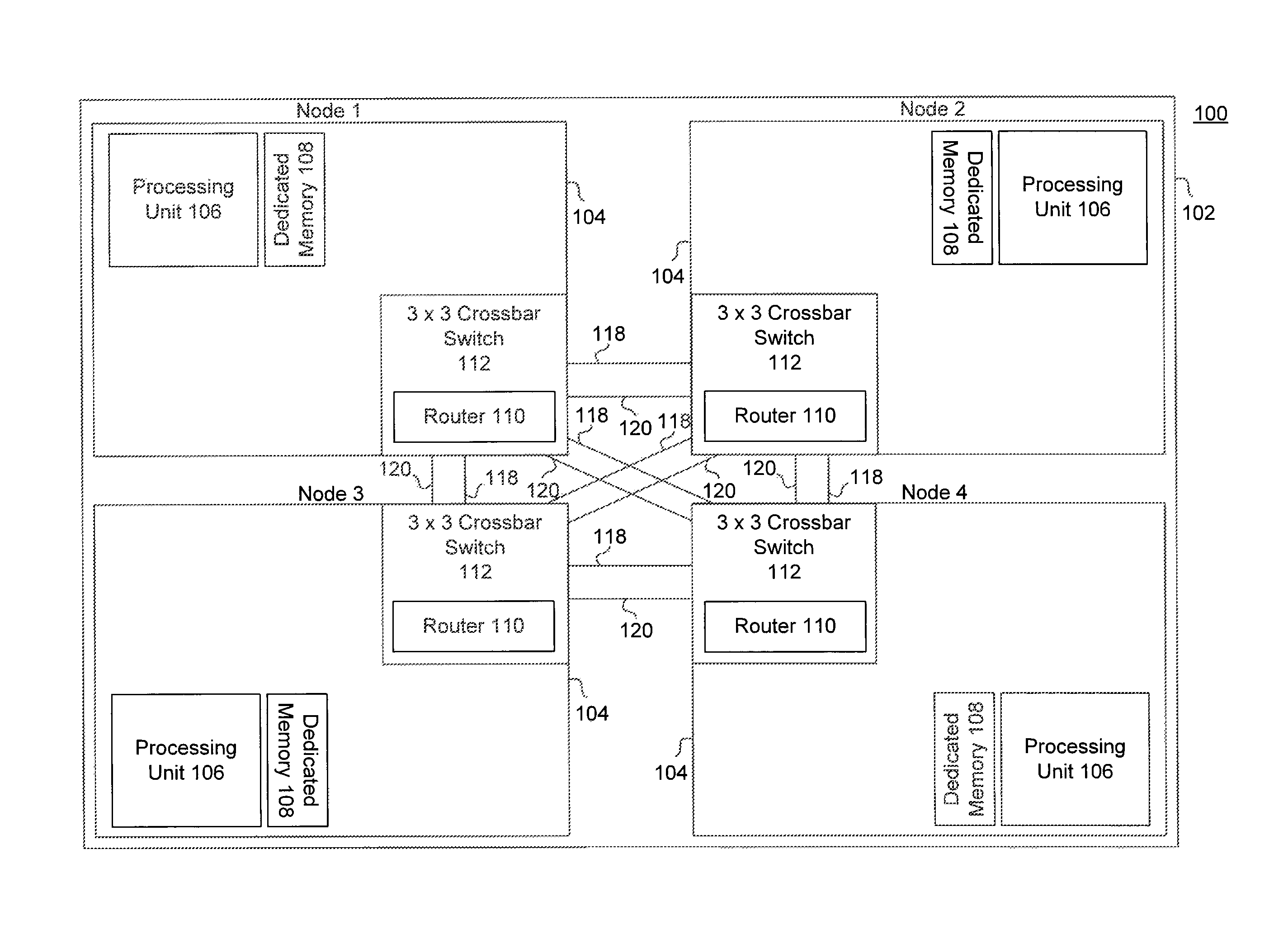

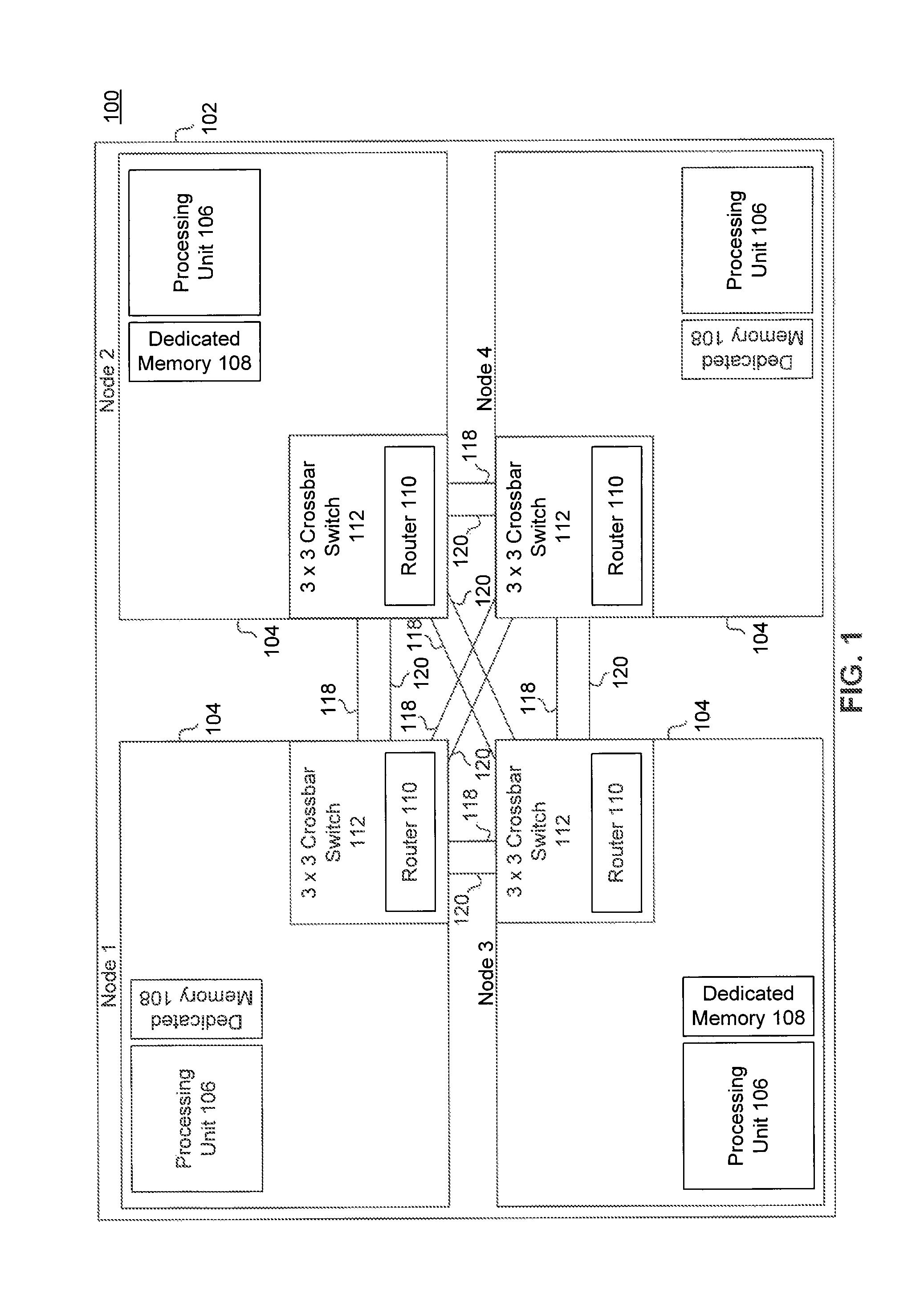

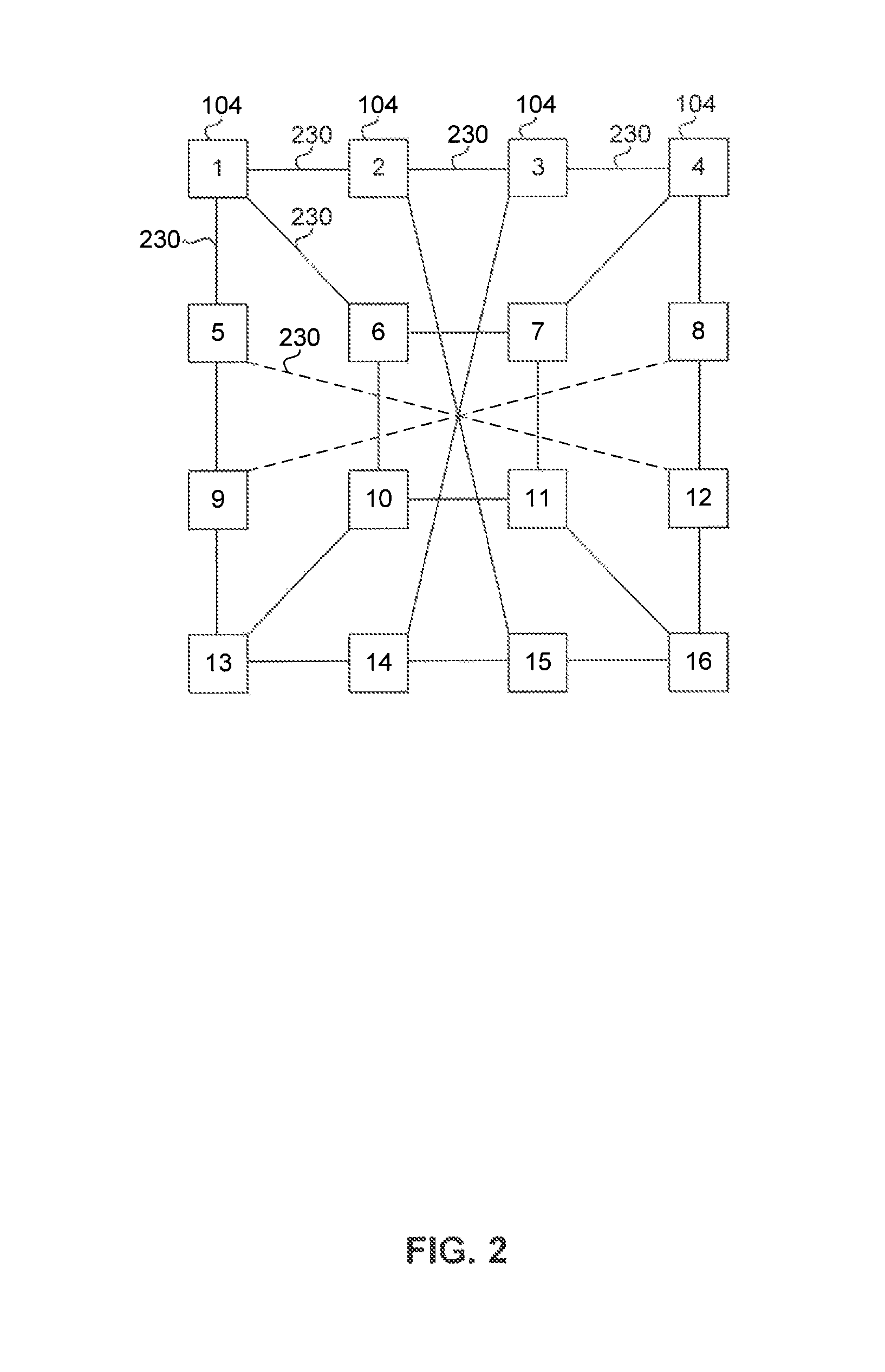

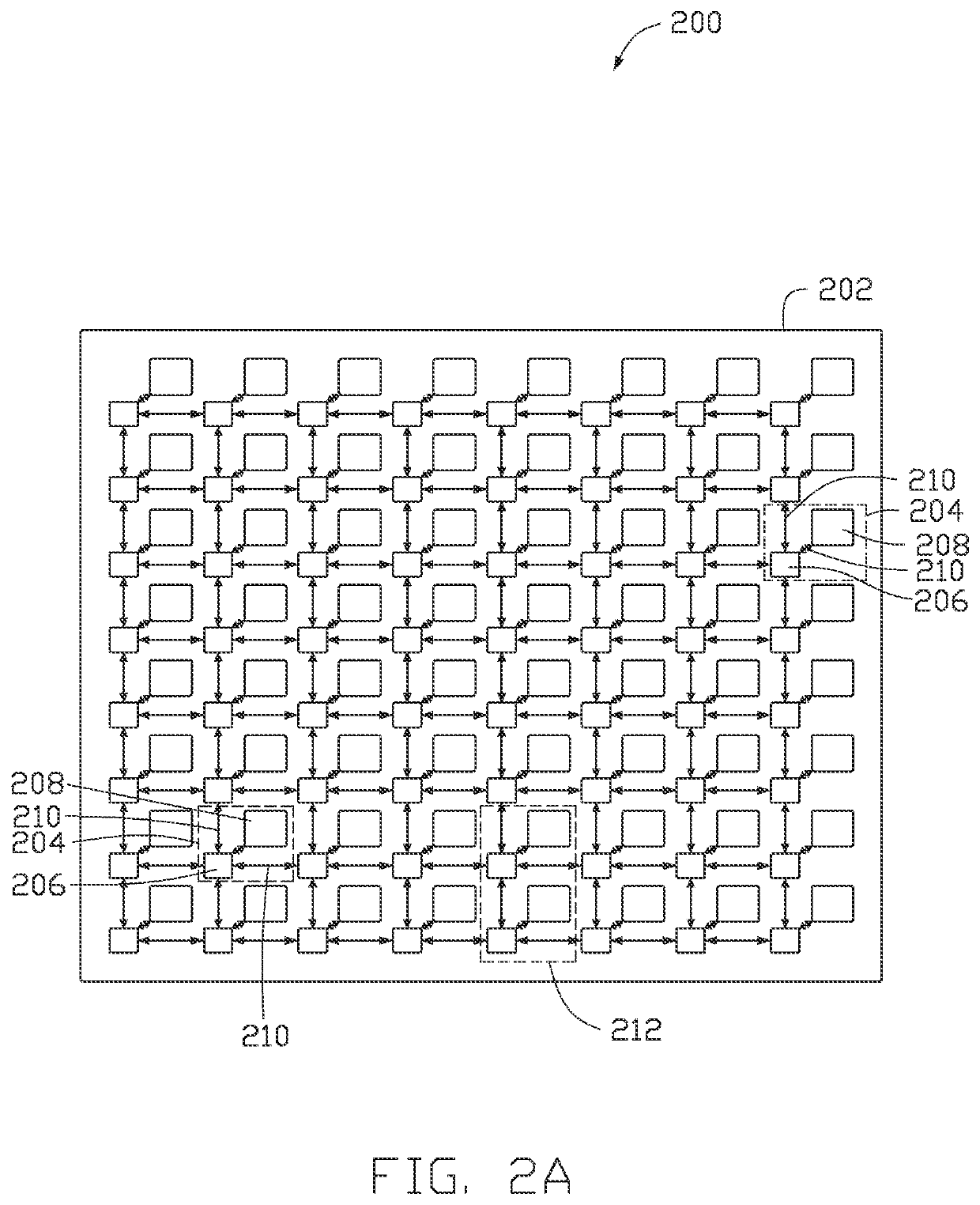

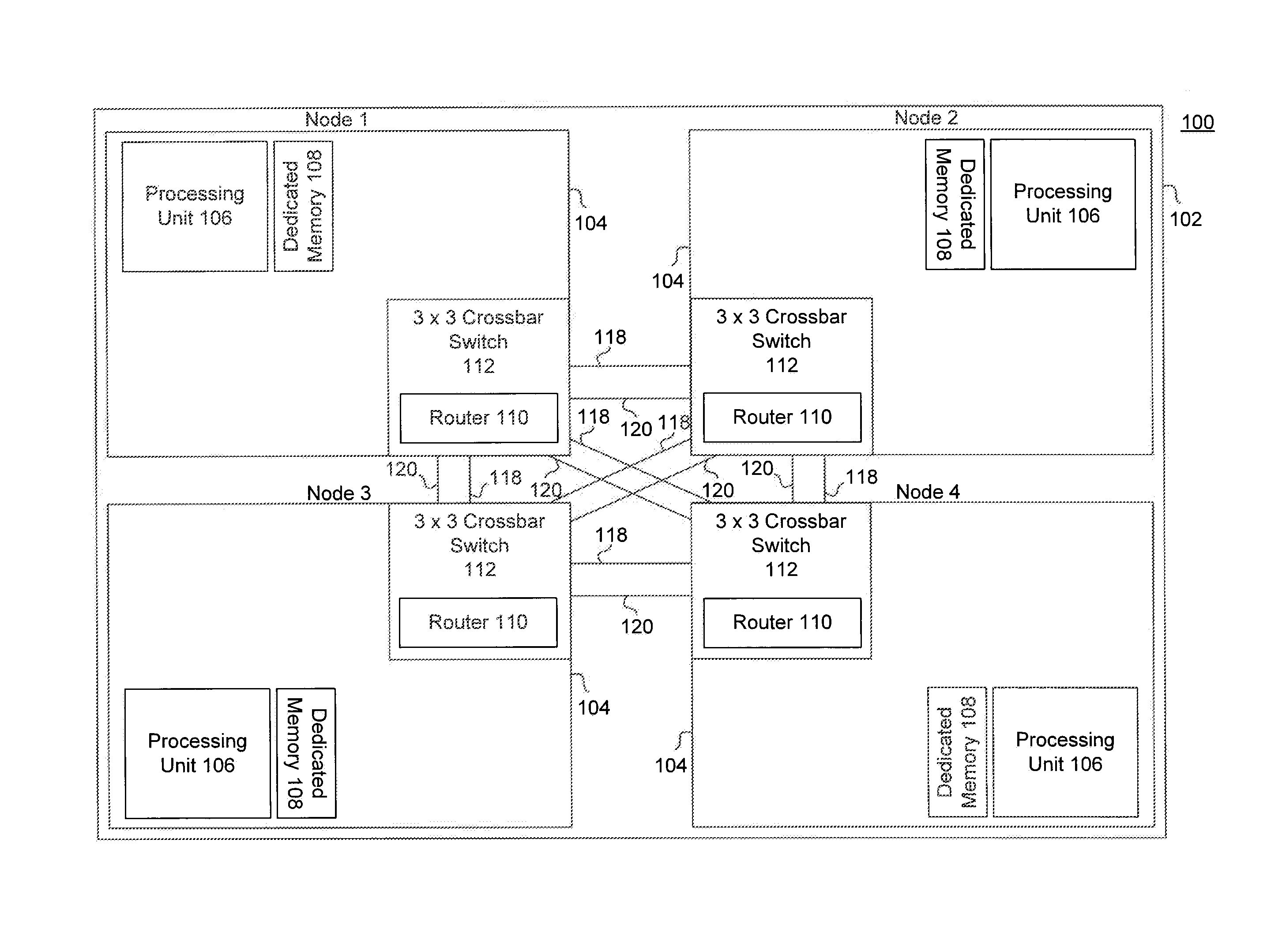

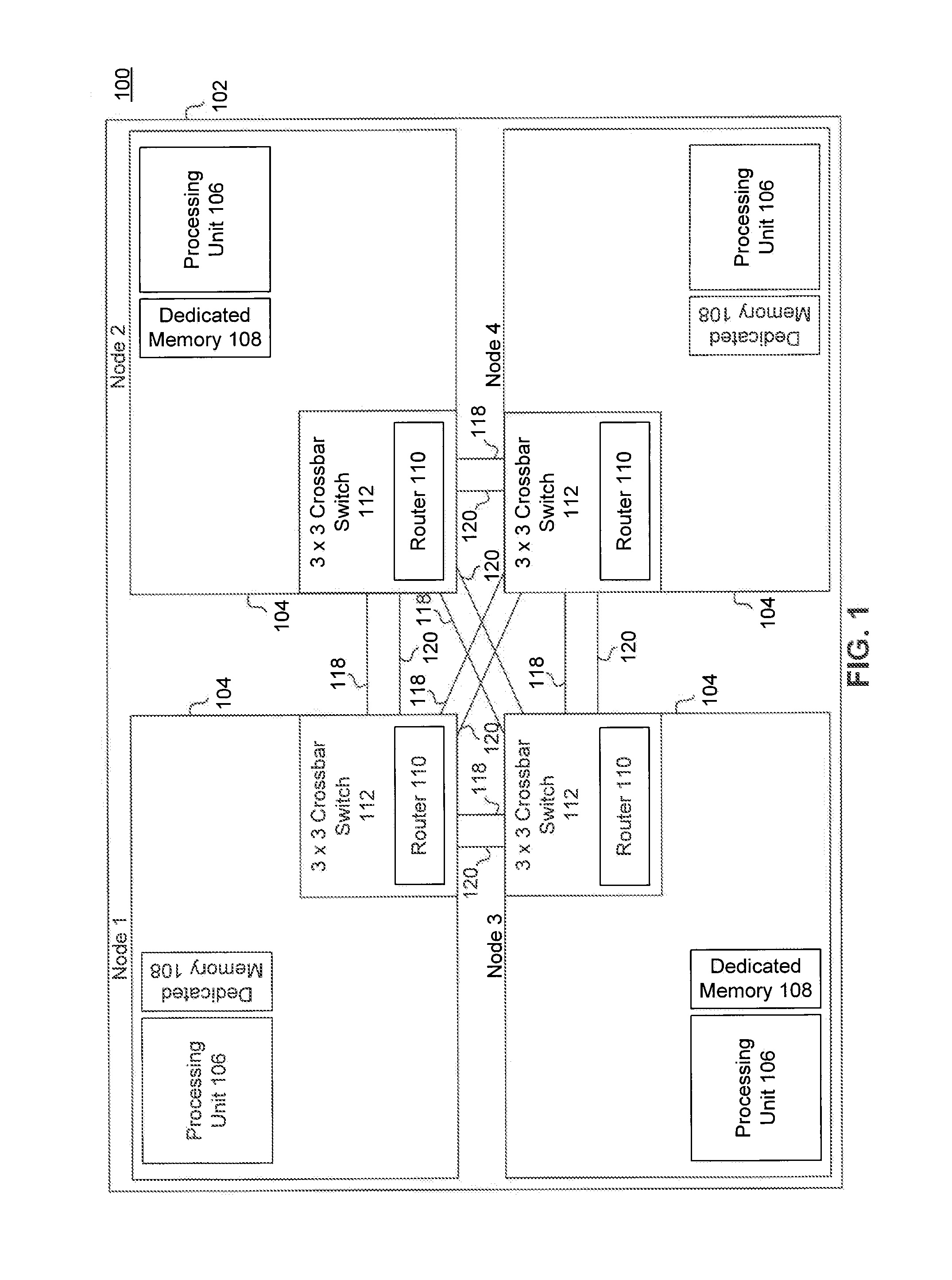

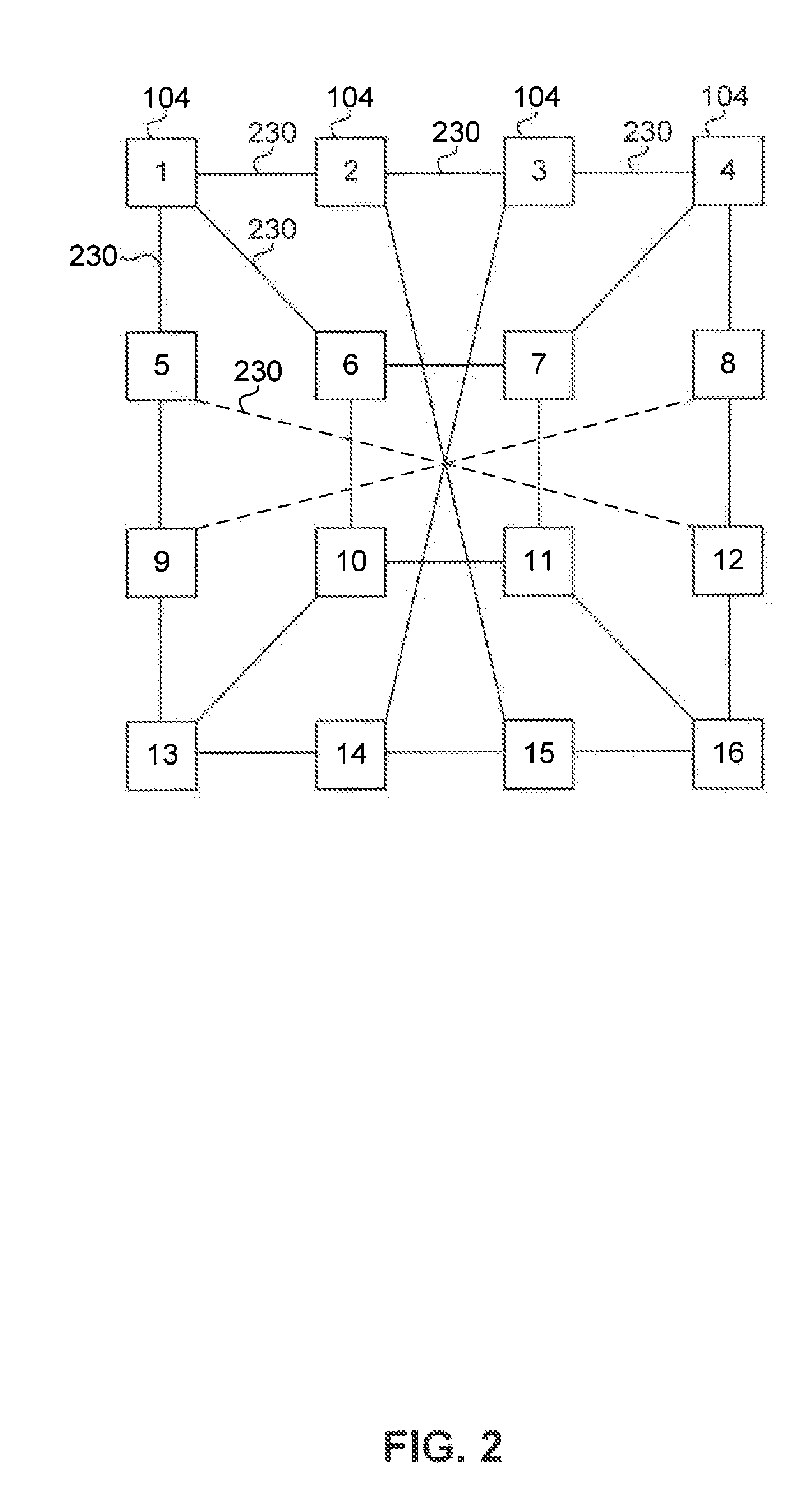

Network-on-chip architecture for multi-processor SoC designs

ActiveUS9436637B2Digital computer detailsElectric digital data processingMulti processorNetworks on chip

A system and method embodying some aspects for communicating between nodes in a network-on-chip are provided. The system comprises a microprocessing chip and a plurality of connection paths. The microprocessing chip comprises sixteen processing nodes disposed on the chip. The plurality of connection paths are configured such that each is at most three hops away from any other node. Each node also has connection paths to at most three other nodes.

Owner:ADVANCED MICRO DEVICES INC

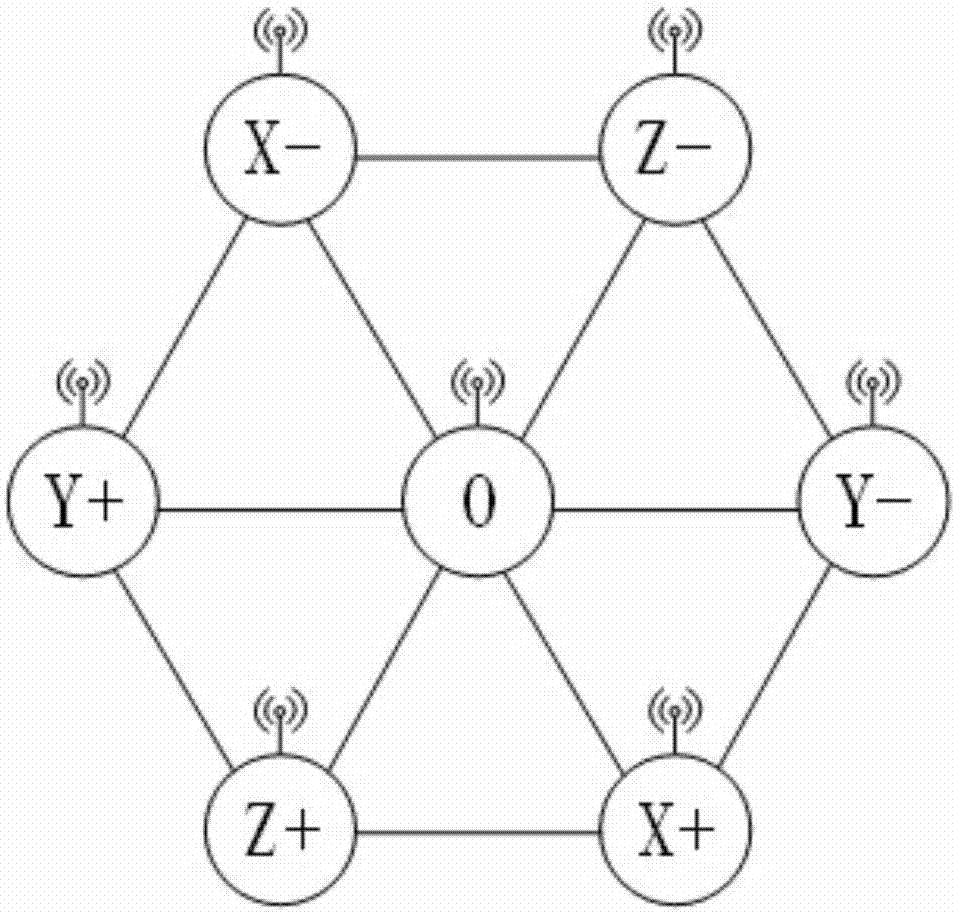

Wireless on-chip network structuring method

InactiveCN103124420ALower latencyImprove throughputHigh level techniquesWireless communicationHigh bandwidthEngineering

The invention discloses a wireless on-chip network structuring method. The wireless on-chip network structuring method comprises the steps of: 1) building a wireless interconnection structure; 2) allocating all the wireless sub-channels to wireless links in the wireless interconnection structure, wherein each wireless link includes at least a wireless sub-channel; and then dynamically adjusting the wireless sub-channels of the wireless links based on combined parameters of the wireless links; and 3) realizing transmission of data packets through unicast routing and multicast routing. The wireless on-chip network structuring method can adjust the wireless sub-channels allocated to the wireless links based on a congestion degree of the wireless links, and has a high bandwidth utilization rate for data transmission, low network delay, low power consumption and a high throughput rate.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

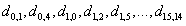

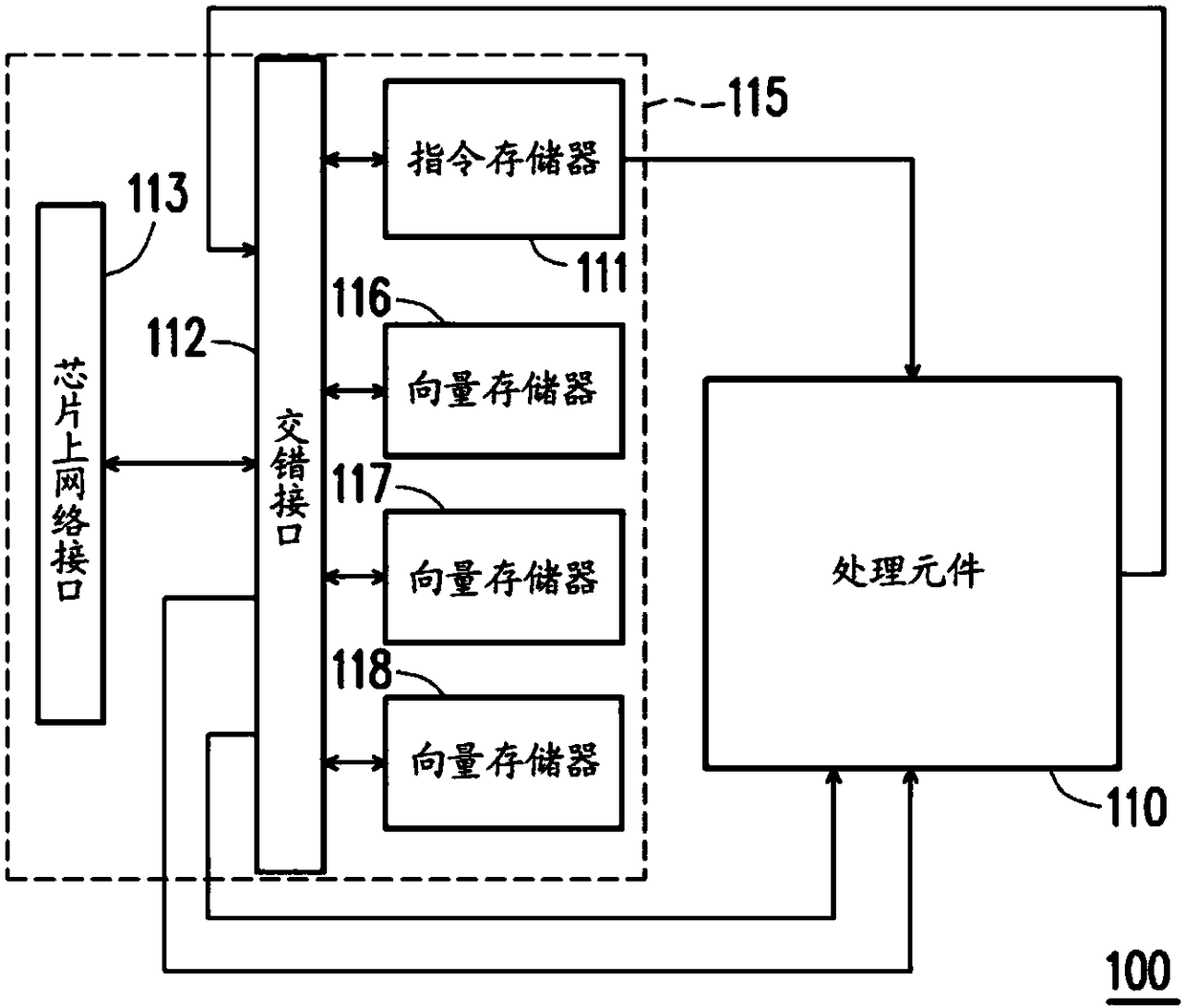

Processing circuit and neural network operating method thereof

ActiveCN108470009AEasy to handleHigh bandwidth transmissionNeural architecturesPhysical realisationComputer moduleParallel computing

The invention provides a processing circuit and a neural network operating method thereof. The processing circuit comprises a plurality of processing elements, a plurality of accessory memories, a system memory and a configuration module, wherein the processing elements are used for performing operation processing; each accessory memory is corresponding to one processing element and is coupled with the other two accessory memories; the system memory is coupled with all the accessory memories and is accessible to the processing elements; the configuration module is coupled with the processing elements and the corresponding accessory memories and the system memory to form a network-on-chip architecture; and the configuration module is capable of statically configuring the operations of the processing elements and the data transmission in the network-on-chip architecture according to neural network operations. Therefore, the neural network operations can be optimized and high operation efficiency is provided.

Owner:VIA ALLIANCE SEMICON CO LTD

System level simulation in network on chip architecture

ActiveUS20150032437A1Digital computer detailsDesign optimisation/simulationSystem-level simulationParallel computing

Systems and methods for performing multi-message transaction based performance simulations of SoC IP cores within a Network on Chip (NoC) interconnect architecture by accurately imitating full SoC behavior are described. The example implementations involve simulations to evaluate and detect NoC behavior based on execution of multiple transactions at different rates / times / intervals, wherein each transaction can contain one or more messages, with each message being associated with a source agent and a destination agent. Each message can also be associated with multiple parameters such as rate, size, value, latency, among other like parameters that can be configured to indicate the execution of the transaction by a simulator to simulate a real-time scenario for generating performance reports for the NoC interconnect.

Owner:INTEL CORP

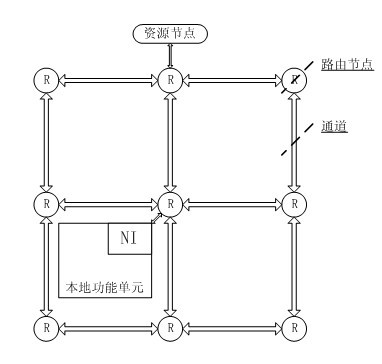

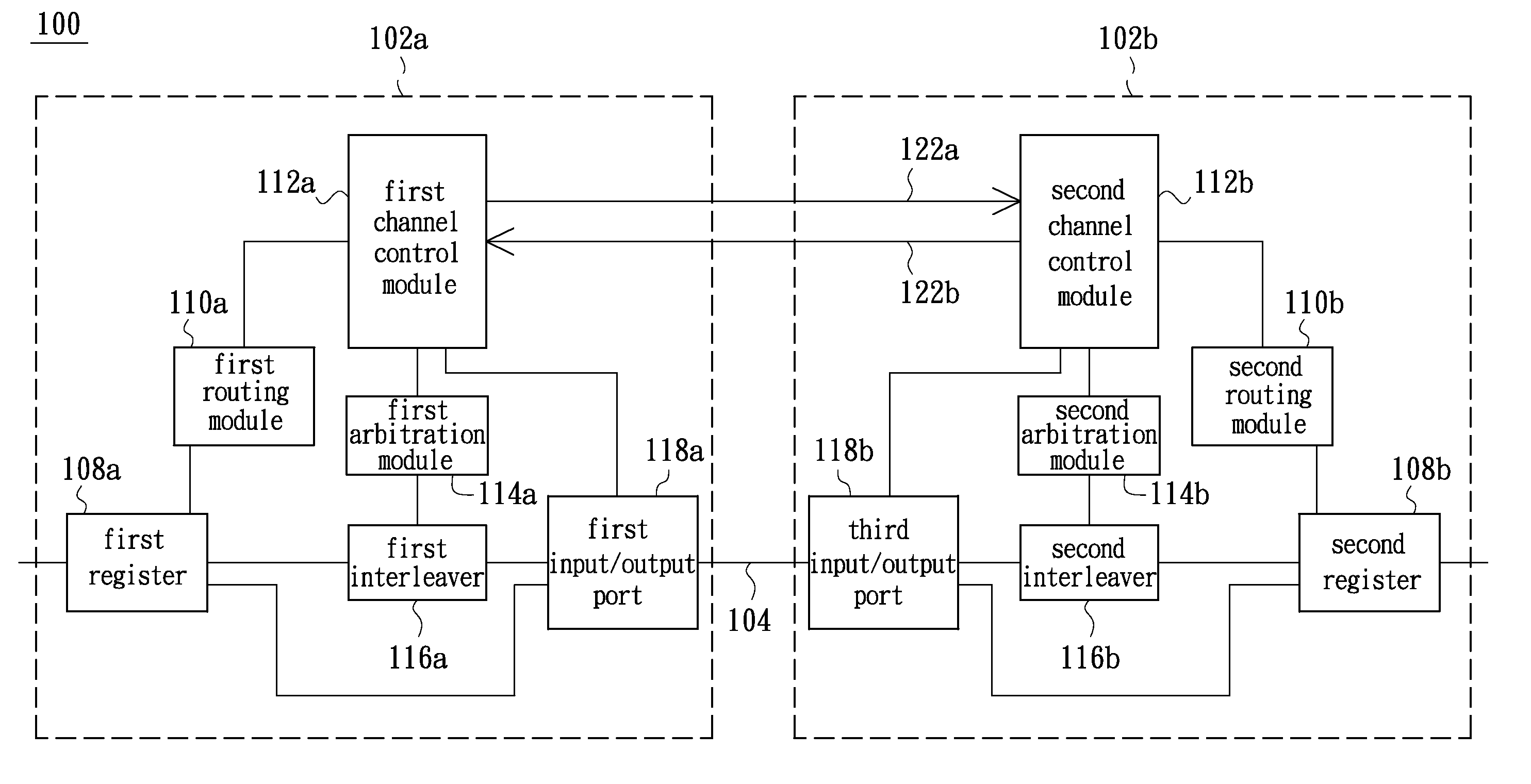

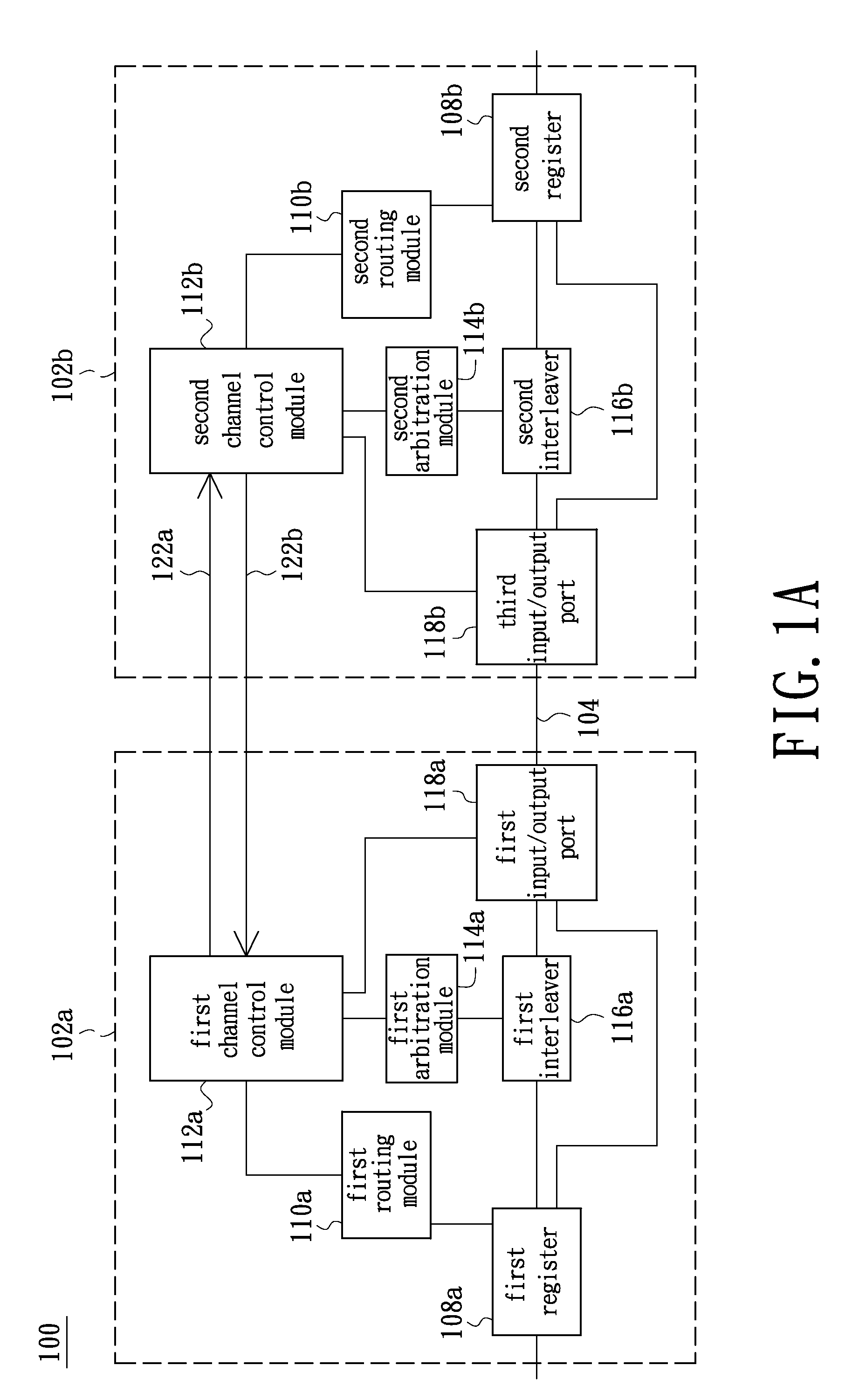

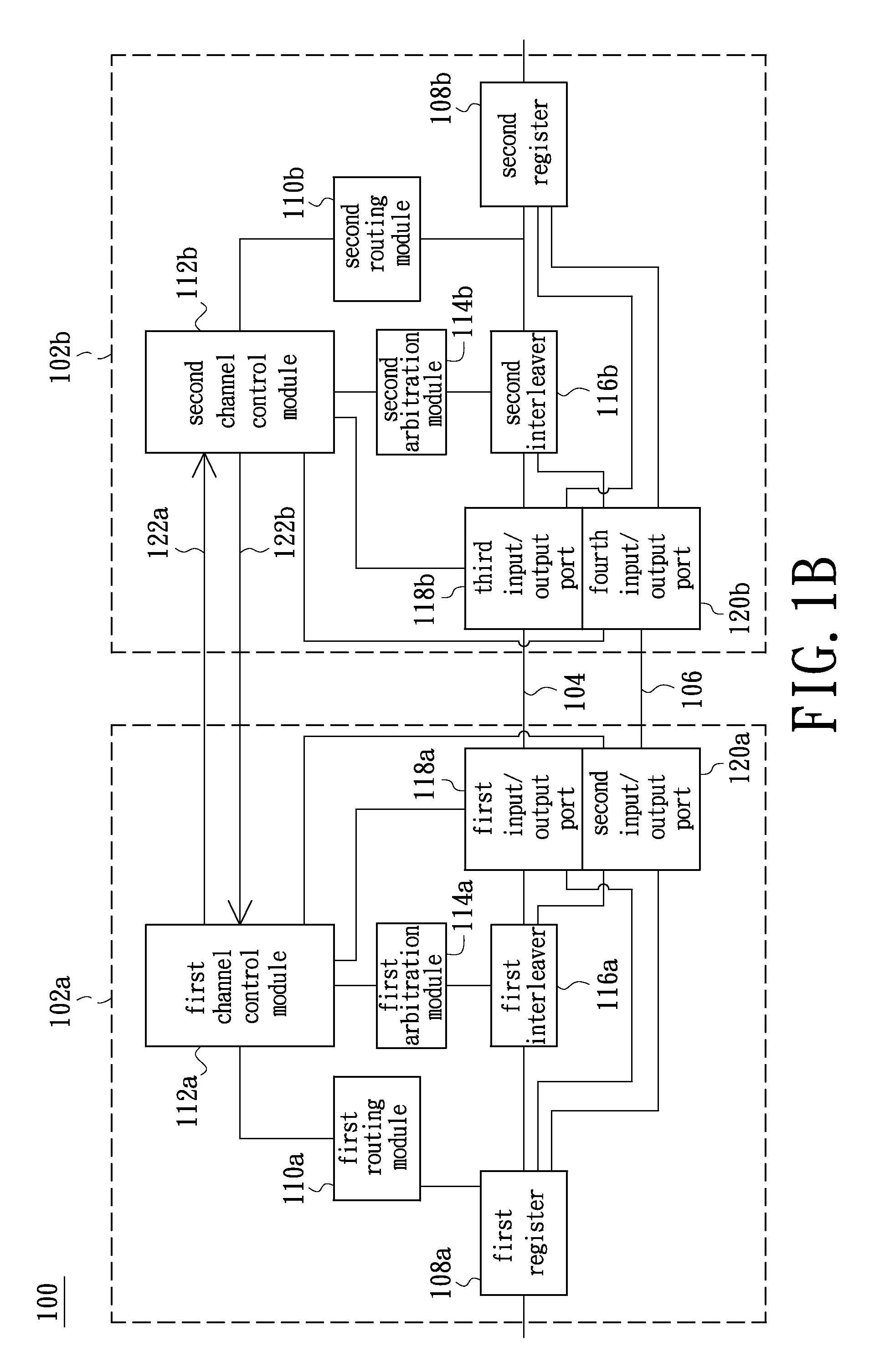

Method for Dynamical Adjusting Channel Direction and Network-on-Chip Architecture thereof

InactiveUS20110064087A1Reduce latencyHigh package transmission efficiencyData switching by path configurationStructure of Management InformationNetwork on chip architecture

A method for dynamical adjusting channel direction and Network-on-Chip architecture thereof are provided. The Network-on-Chip architecture of dynamical adjusting channel direction comprises a first channel, a first router and a second router. The first channel has a first transmission direction. The first router generates and outputs a first output request when receiving a first data. The second router is coupled to the first router through the first channel. The second router receives the first data through the first channel when receiving the first output request.

Owner:NAT TAIWAN UNIV

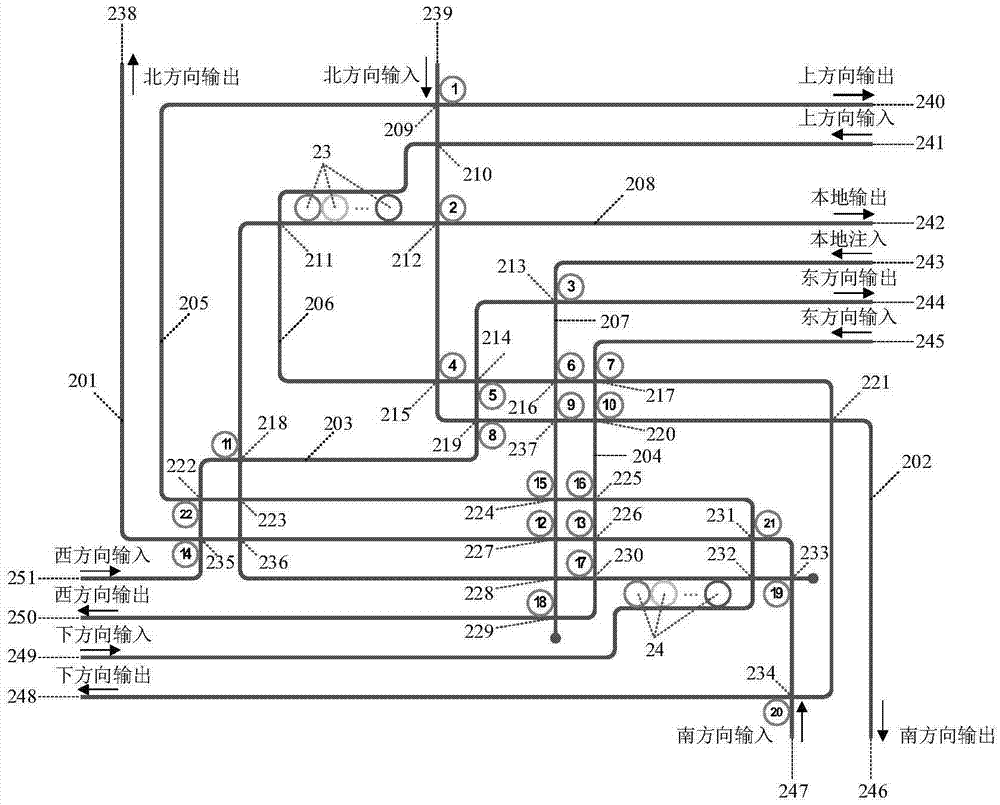

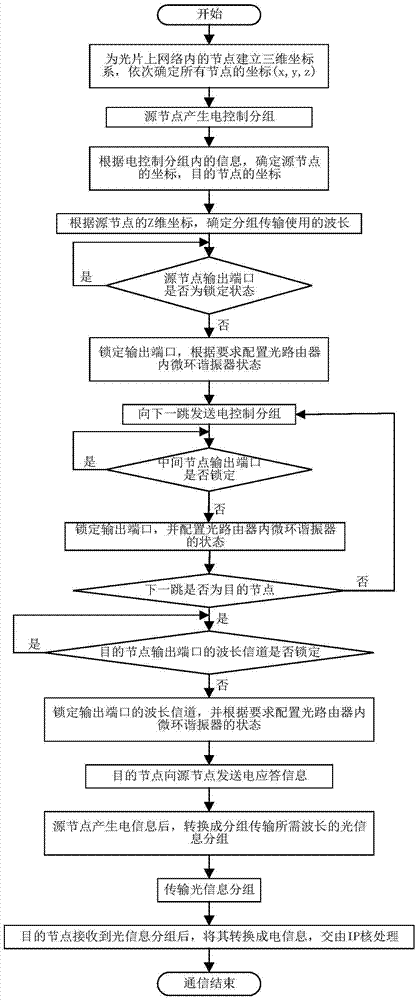

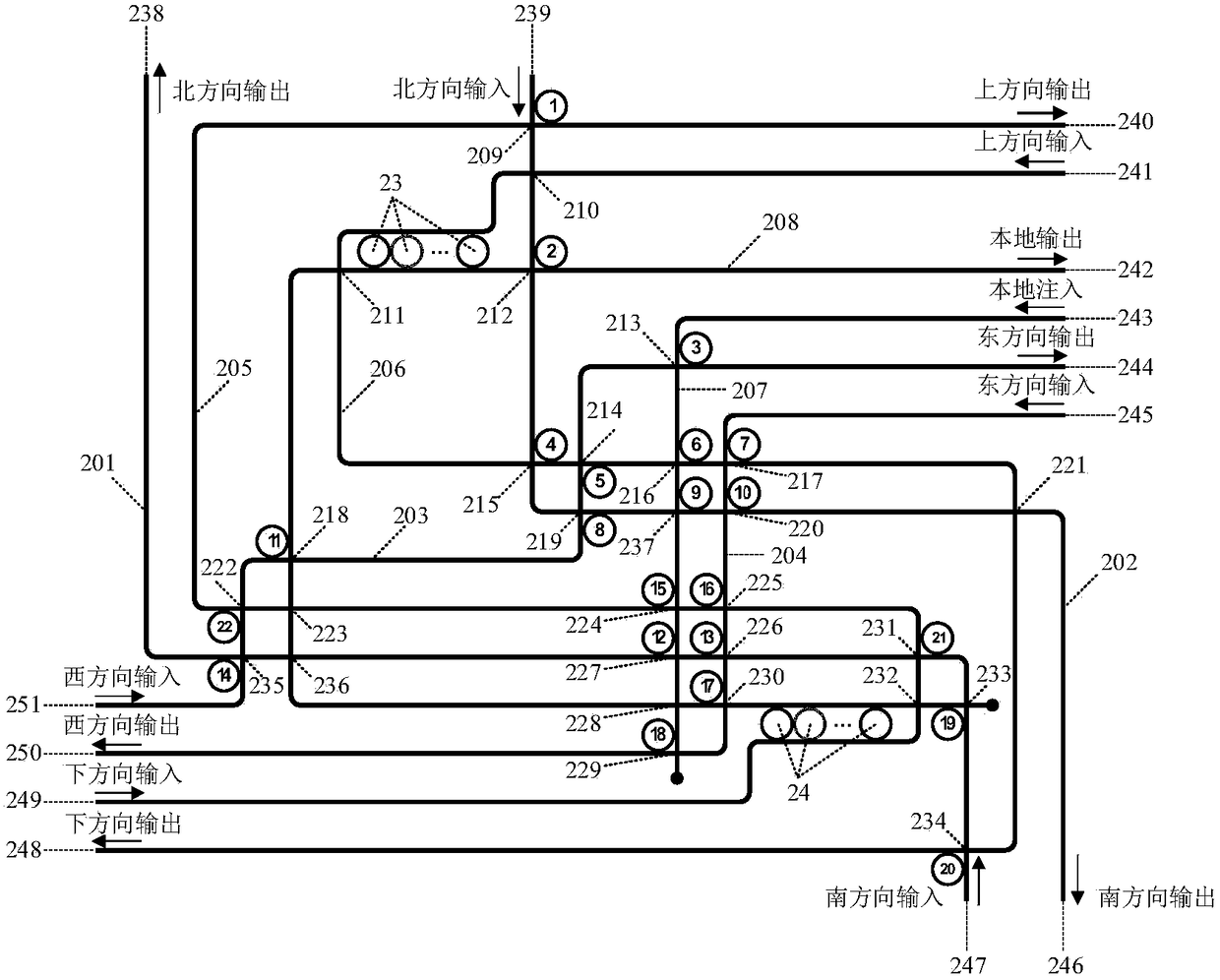

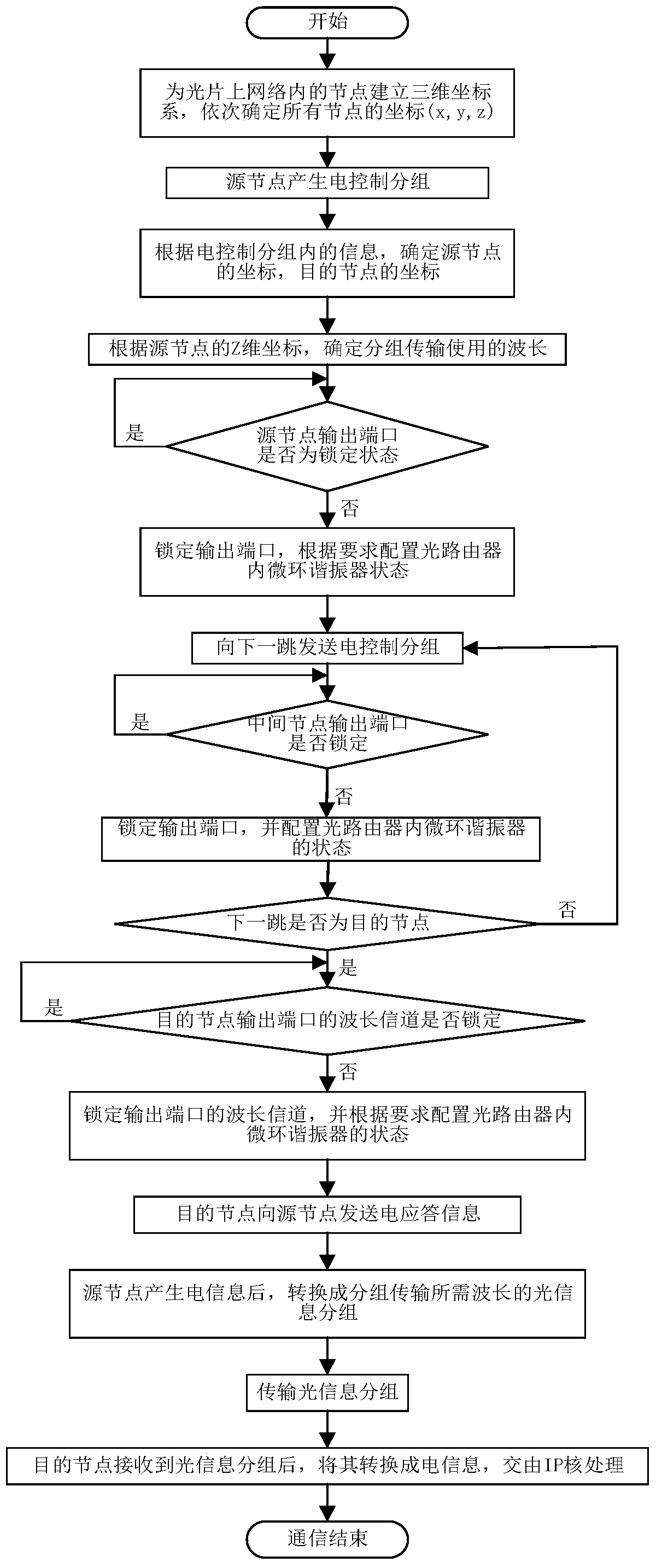

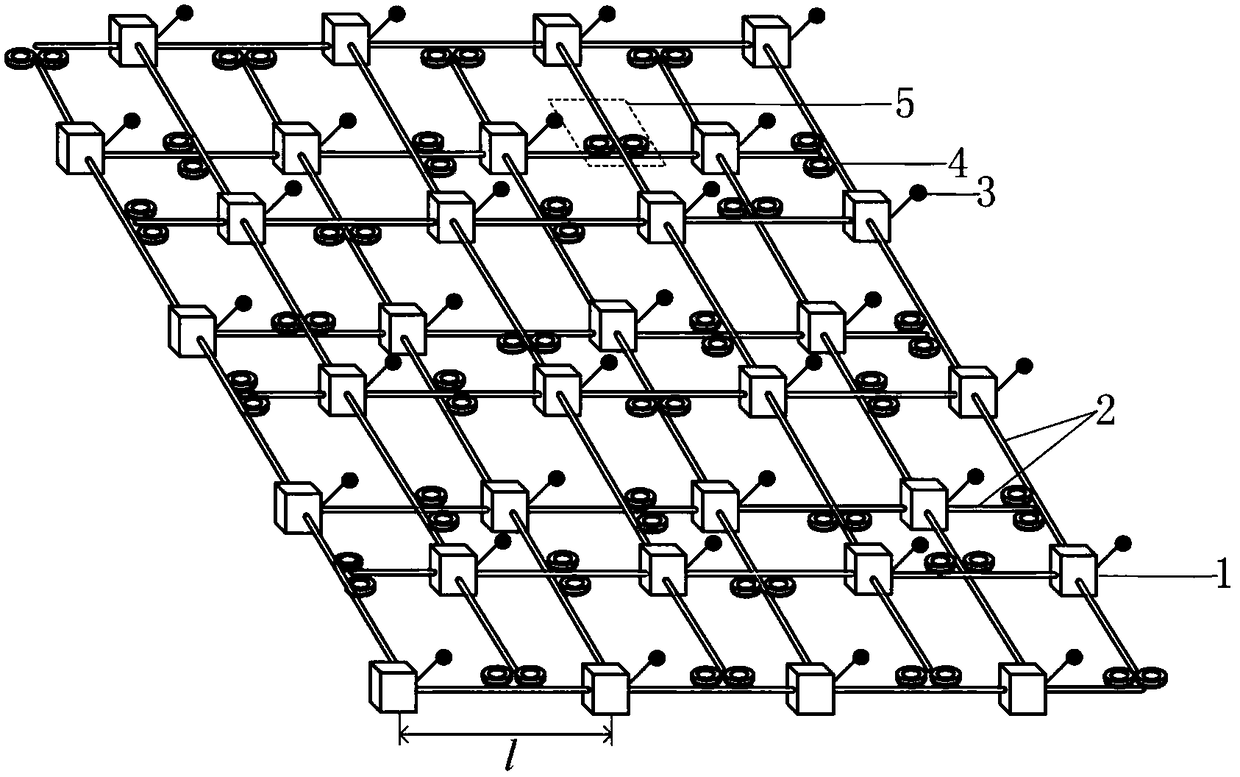

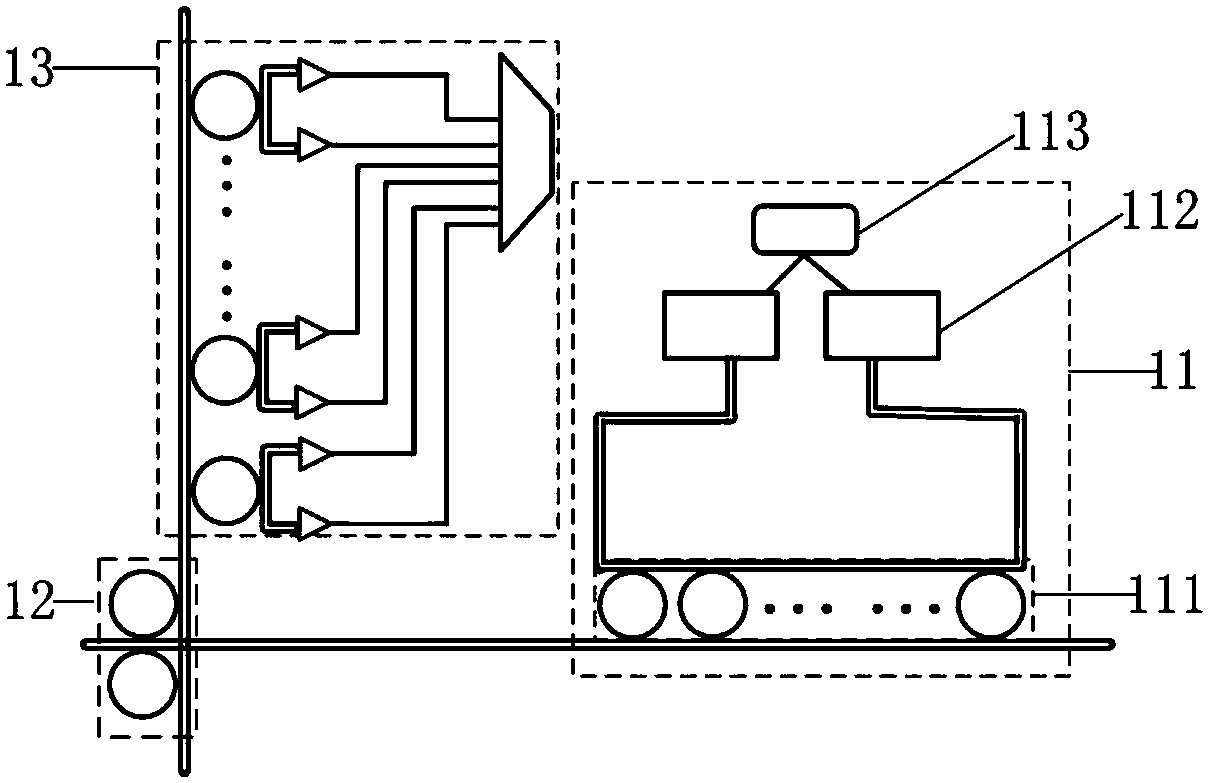

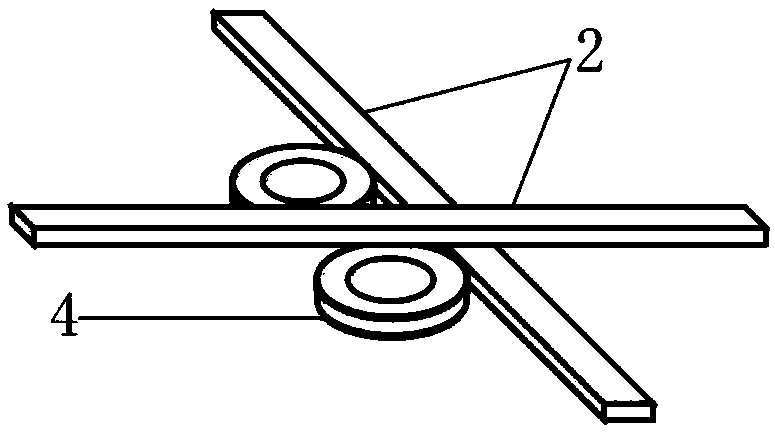

Wavelength-allocation-based three-dimensional optical on-chip network router communication system and method

ActiveCN105451103AOvercoming blockageOvercoming utilizationMultiplex system selection arrangementsData switching networksStructure of Management InformationNetwork architecture

The invention relates to a wavelength-allocation-based three-dimensional optical on-chip network router communication system and method. The communication system employs a photoelectric mixing type 3D mesh network topological structure and a novel seven-port clog-free optical router capable of realizing multi-wavelength communication; and when the system is applied to a three-dimensional optical on-chip network, no wavelength conversion is needed. Because of utilization of the optical router, the consumed number of optical devices like micro ring resonators and waveguides and the like is reduced. Besides, according to the communication method, when a node of each layer sends out an optical signal, the employed wavelengths are identical; and optical signals with all wavelengths can be received at all layers, so that problems of severe network congestion, low link utilization rate, and limited expansibility due to utilization of single wavelength communication by the existing optical on-chip network architecture can be solved. Therefore, with the system and method, the network congestion probability can be reduced; the communication delay can be reduced; and the throughput capacity and network saturation point can be improved.

Owner:XIDIAN UNIV

Method of creating core-tile-switch mapping architecture in on-chip bus and computer-readable medium for recording the method

There are provided a method of creating an optimized core-tile-switch mapping architecture in an on-chip bus and a computer-readable recording medium for recording the method. The core-tile-switch mapping architecture creating method includes: creating a core communication graph representing the connection relationship between arbitrary cores; creating a Network-on-chip (NOC) architecture including a plurality of switches, a plurality of tiles, and a plurality of links interconnecting the plurality of switches; and mapping the cores to the tiles using a predetermined optimized mapping method to thereby create the optimized core-tile-switch mapping architecture. The optimized mapping method includes first, second, and third calculating steps. According to the optimized core-tile-switch mapping architecture creating method and the computer-readable recording medium for recording the method, since the hop distance between cores is minimized, it is possible to minimize energy consumption and communication delay time in an on-chip bus. Furthermore, the optimized mapping architecture presents a standard for comparing the optimization of other mapping architectures.

Owner:SAMSUNG ELECTRONICS CO LTD

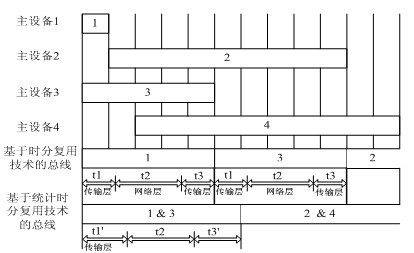

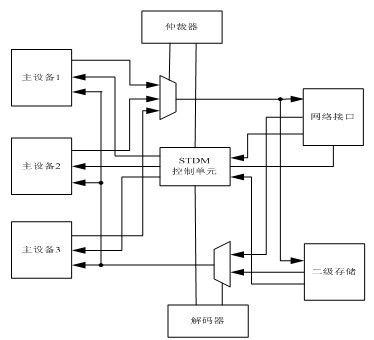

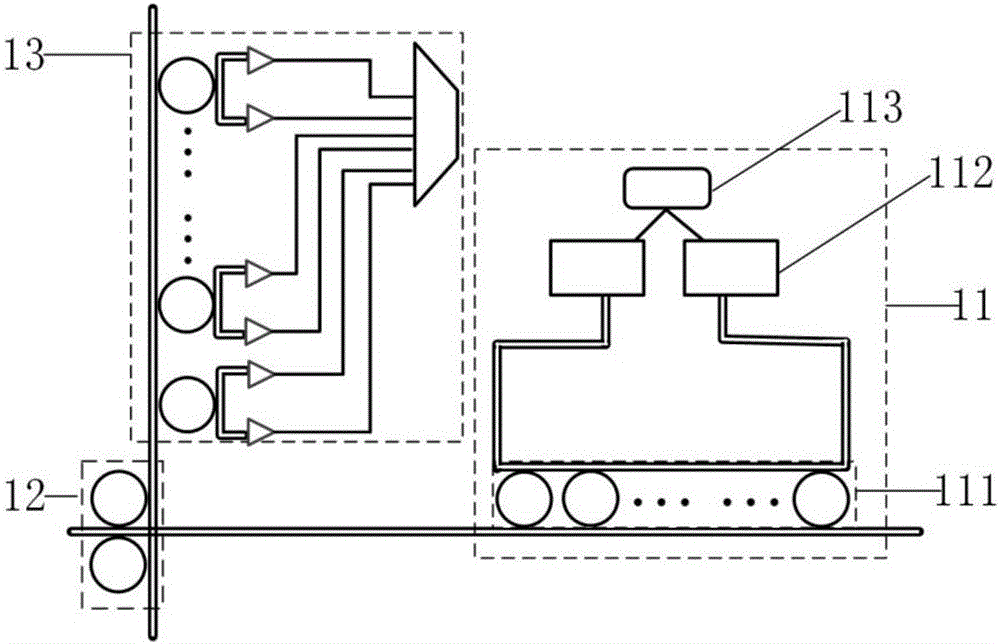

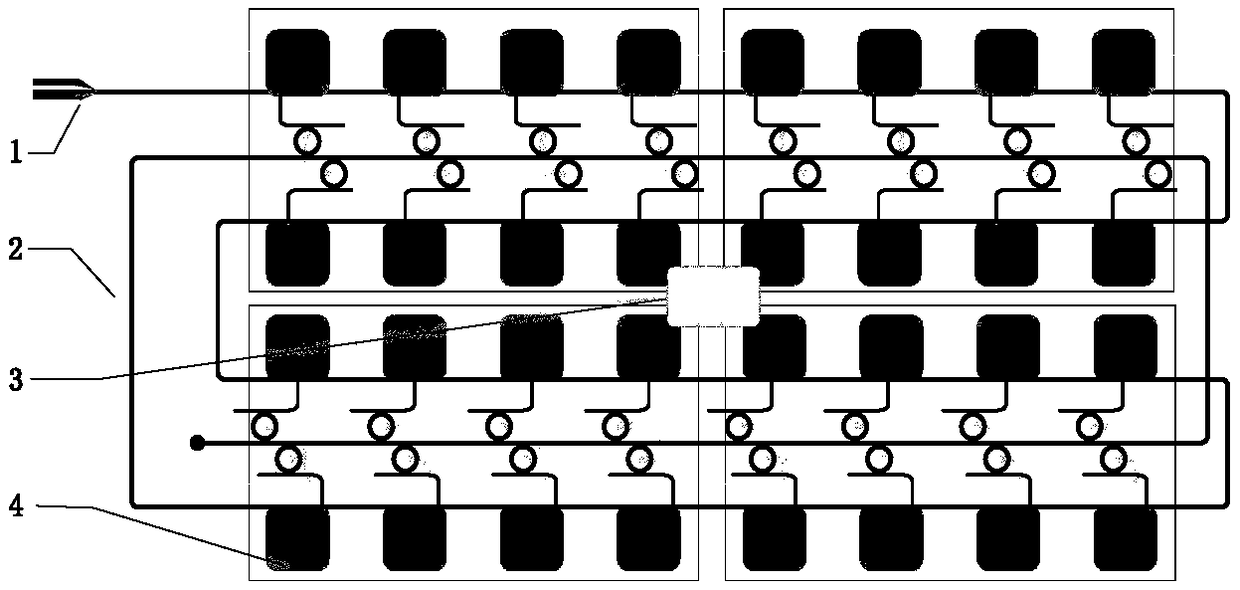

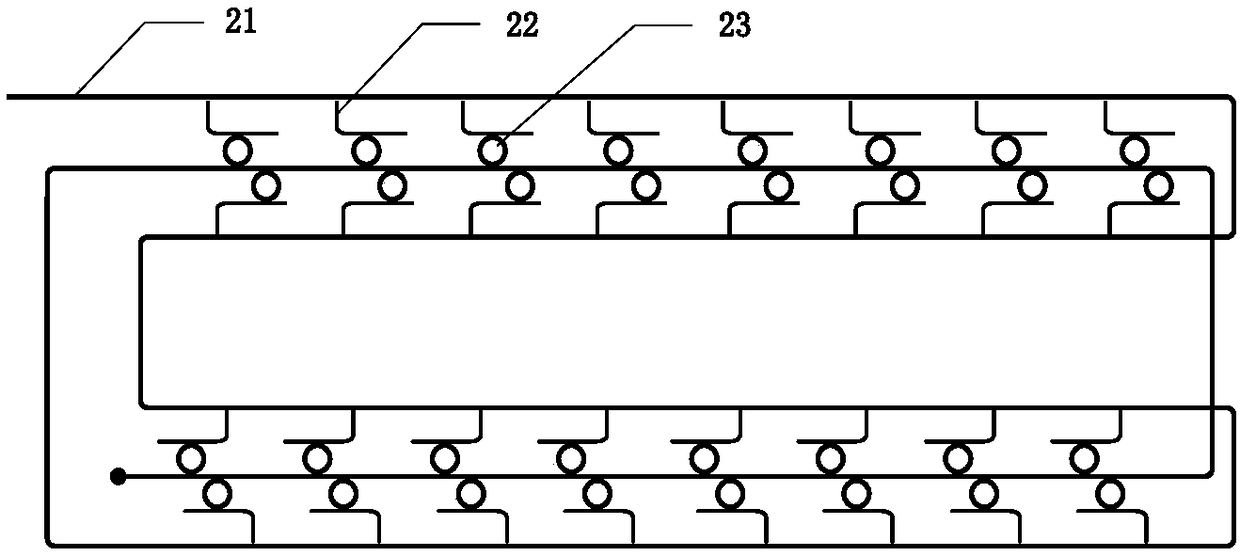

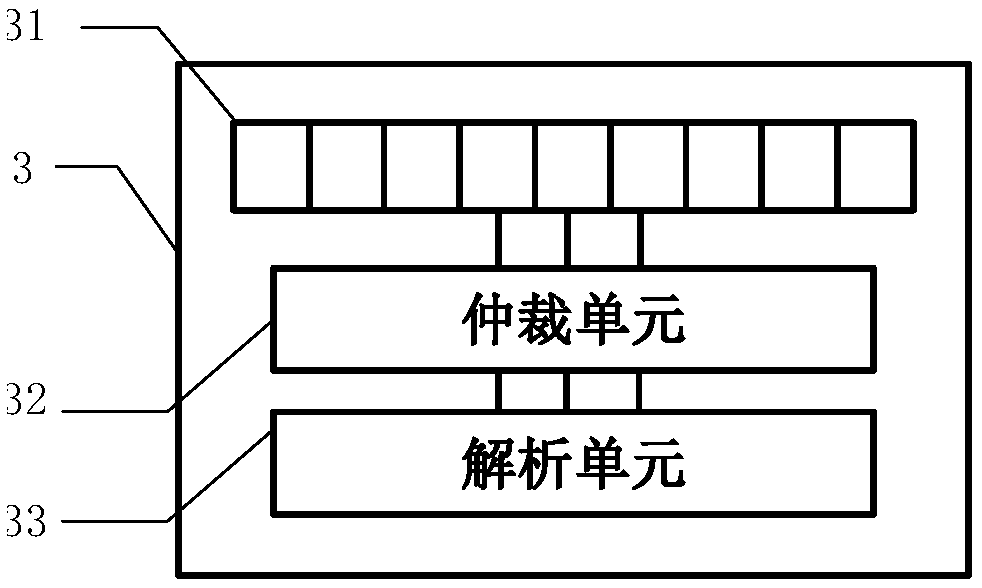

Multi-cluster network-on-chip architecture based on statistic time division multiplexing technology

ActiveCN102158380AReduce communication differencesReduce loadTime-division multiplexBus networksStructure of Management InformationTime-division multiplexing

The invention discloses a multi-cluster network-on-chip architecture based on a statistic time division multiplexing technology. In the architecture, a bus structure based on the statistic time division multiplexing technology is adopted in clusters; master equipment, slave equipment, a bus component and a statistic time division multiplexing control unit are arranged on a bus; the statistic timedivision multiplexing control unit is connected with the master equipment, the slave equipment and the bus component, wherein the slave equipment comprises a memory and a network interface with a waiting mechanism; the bus component comprises an arbitrator, a decoder and a multipath selector; the statistic time division multiplexing control unit unifiedly controls the master equipment and the slave equipment on the bus to realize the statistic time division multiplexing mechanism; and the network interface with the waiting mechanism receives a data transmission request initiated by the masterequipment on the bus and triggers the transmission under the condition of satisfying the triggering conditions. The multi-cluster network-on-chip architecture disclosed by the invention can effectively reduce the network load and the communication relay and further improves the whole performance of a network-on-chip system, thereby having favorable application value and wide application prospect.

Owner:江苏南大显示技术有限公司

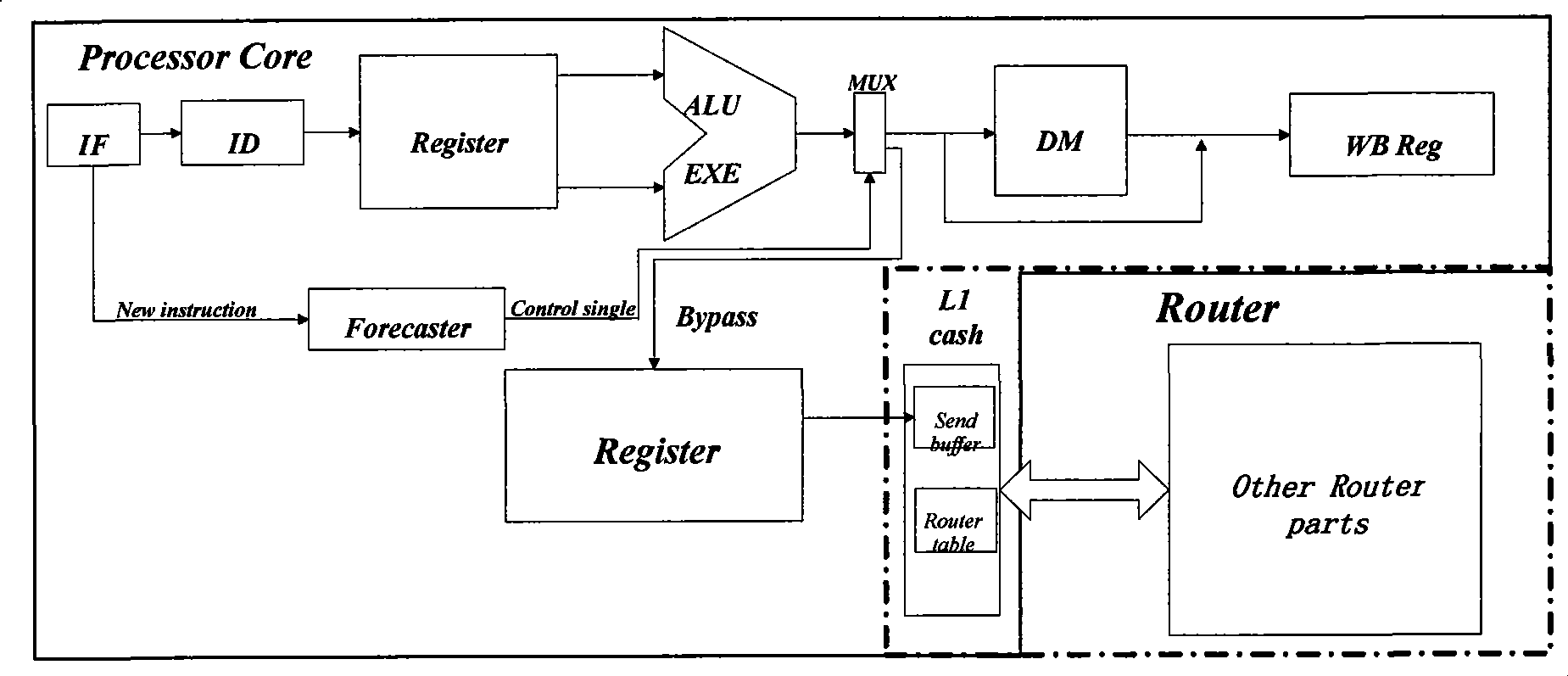

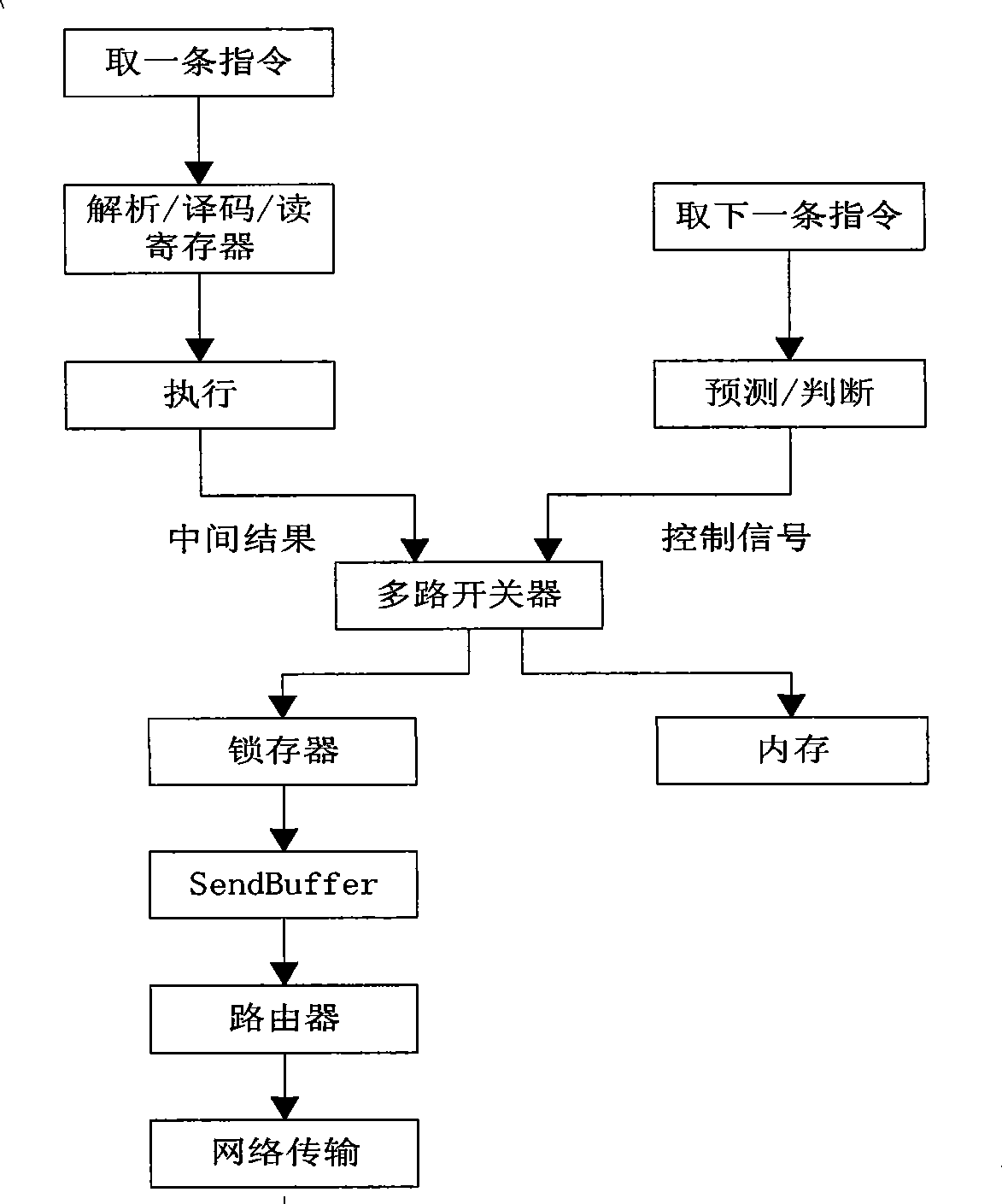

Method for optimizing on-chip network structure by adding bypass in processor

InactiveCN101534251AReduce energy consumptionReduce sizeConcurrent instruction executionData switching networksNetwork structureNetwork on

The invention discloses a method for optimizing the on-chip network structure by adding a bypass in a processor. In the invention, the bypass is added in the processor and the auxiliary module is added to support the lower delayed on-chip network structure. In the invention, the processor can be used for not only transmitting the treated result, but also transmitting the intermediate result temporarily stored in the treatment process, for the other node processor, the more data can be obtained, the treating function of the network on the whole chip can be extended. For the thread with the higher data dependence, a large number of data treatment and transmission can be performed between the threads, the execution efficiency is higher. The invention can improve the processor to better support the on-chip network structure and performing the on-chip network advantages.

Owner:ZHEJIANG UNIV

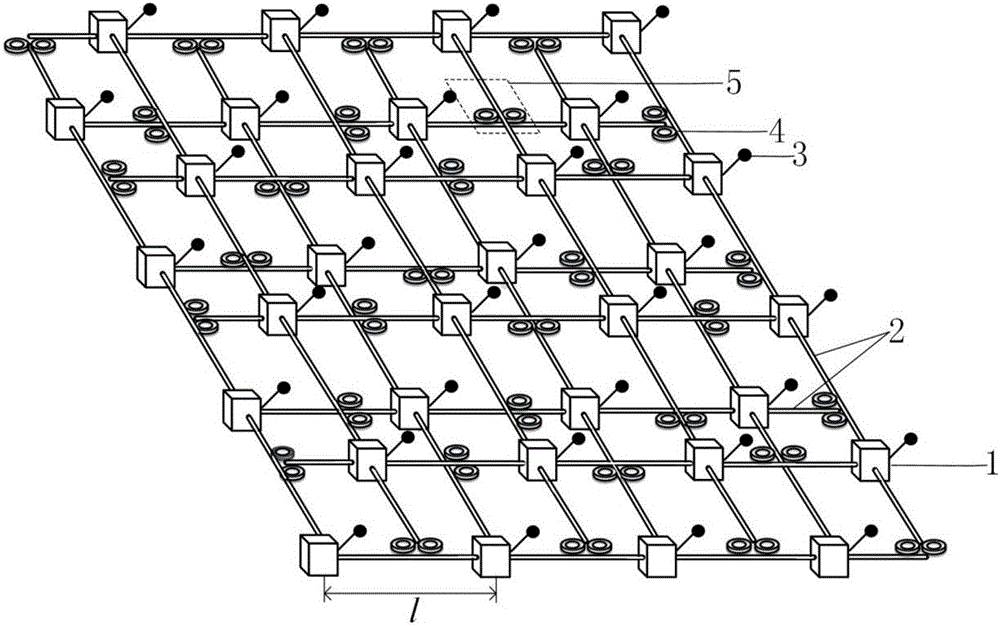

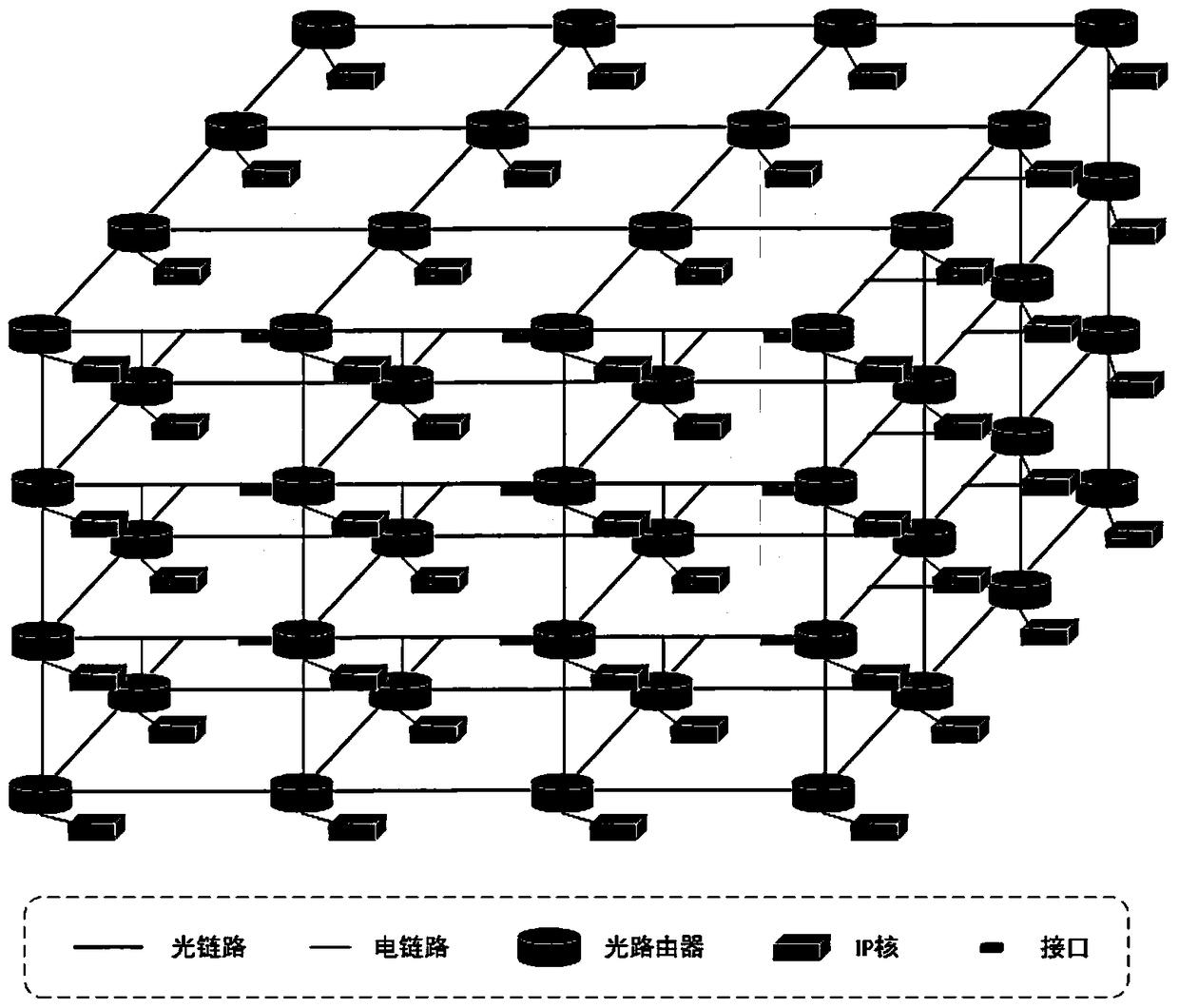

Topological structure based on staggered three-dimensional light network-on-chip and wavelength distribution method

ActiveCN106126471AReduce the numberReduce blocking rateMultiplex system selection arrangementsArchitecture with single central processing unitDistribution methodDiagonal

The invention provides a topological structure based on a staggered three-dimensional light network-on-chip and a wavelength distribution method, and aims to solve the technical problems of serious blockage in the network and high loss in the prior art. The topological structure comprises two layers of 2D-Mesh light networks-on-chip and an interlaminar router; the light networks-on-chip comprise NxN routers connected through optical waveguides; each router is connected with an IP core; the two layers of light networks-on-chip are staggered from each other along the corresponding diagonals, and optical waveguides are added into the light networks-on-chip corresponding to gaps in four single-layer parts on the staggering edges along the optical waveguide directions in the light networks-on-chip; and the interlaminar router is arranged at a position perpendicular to the space where the optical waveguides of the different layer are positioned. The wavelength distribution method of the topological structure comprises the following steps: firstly establishing a three-dimensional coordinate system, and selecting wavelength values; secondly, distributing the wavelength values to all nodes; and finally, configuring a working offset state and temperature of an exchange microring resonator or an interlaminar microring coupler according to the wavelength values distributed to all the nodes.

Owner:XIDIAN UNIV

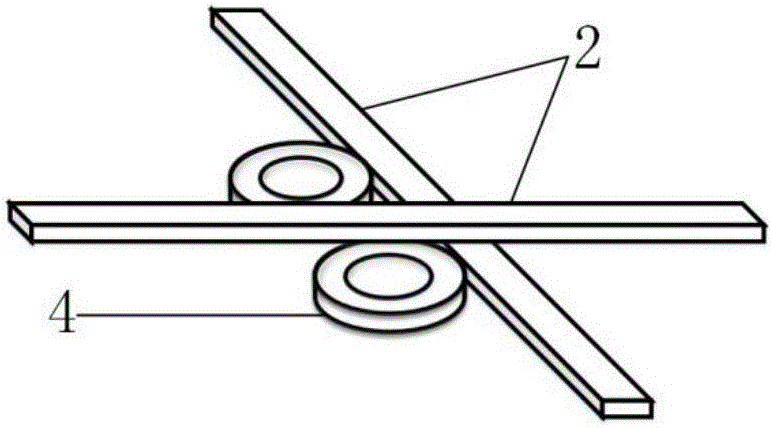

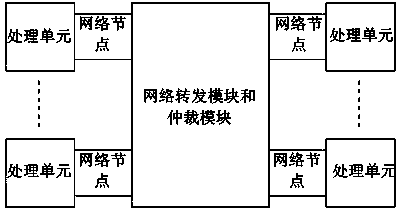

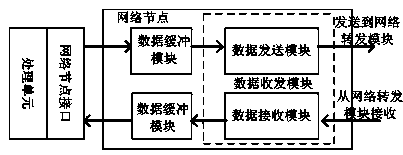

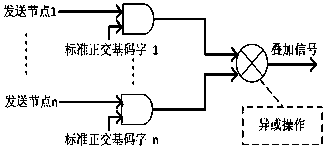

CDMA (code division multiple access) on-chip network architecture based on standard orthonormal basis and realization method of CDMA on-chip network architecture

InactiveCN103389962ASolve UtilizationSolve resource problemsDigital computer detailsElectric digital data processingTime division multiple accessCode division multiple access

The invention discloses a CDMA (code division multiple access) on-chip network architecture based on a standard orthonormal basis and a realization method of the CDMA on-chip network architecture. The CDMA on-chip network architecture and the method mainly solve the problem that in the prior art, the on-chip network architecture cannot reduce the resource waste or reduce the power consumption while ensuring the transmission quality and the transmission efficiency. The CDMA on-chip network architecture based on the standard orthonormal basis comprises a network transmitting module, an arbitration module and more than two processing units, wherein the network transmitting module and the arbitration module are integrated, and the processing units are connected with the network transmitting module and the arbitration module respectively through network nodes. Through the scheme, the CDMA on-chip network architecture and the method have the advantages that the goals that the transmission quality and the transmission efficiency are high, in addition, the resource waste and the power consumption are low are reached, and high practical value and popularization value are realized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

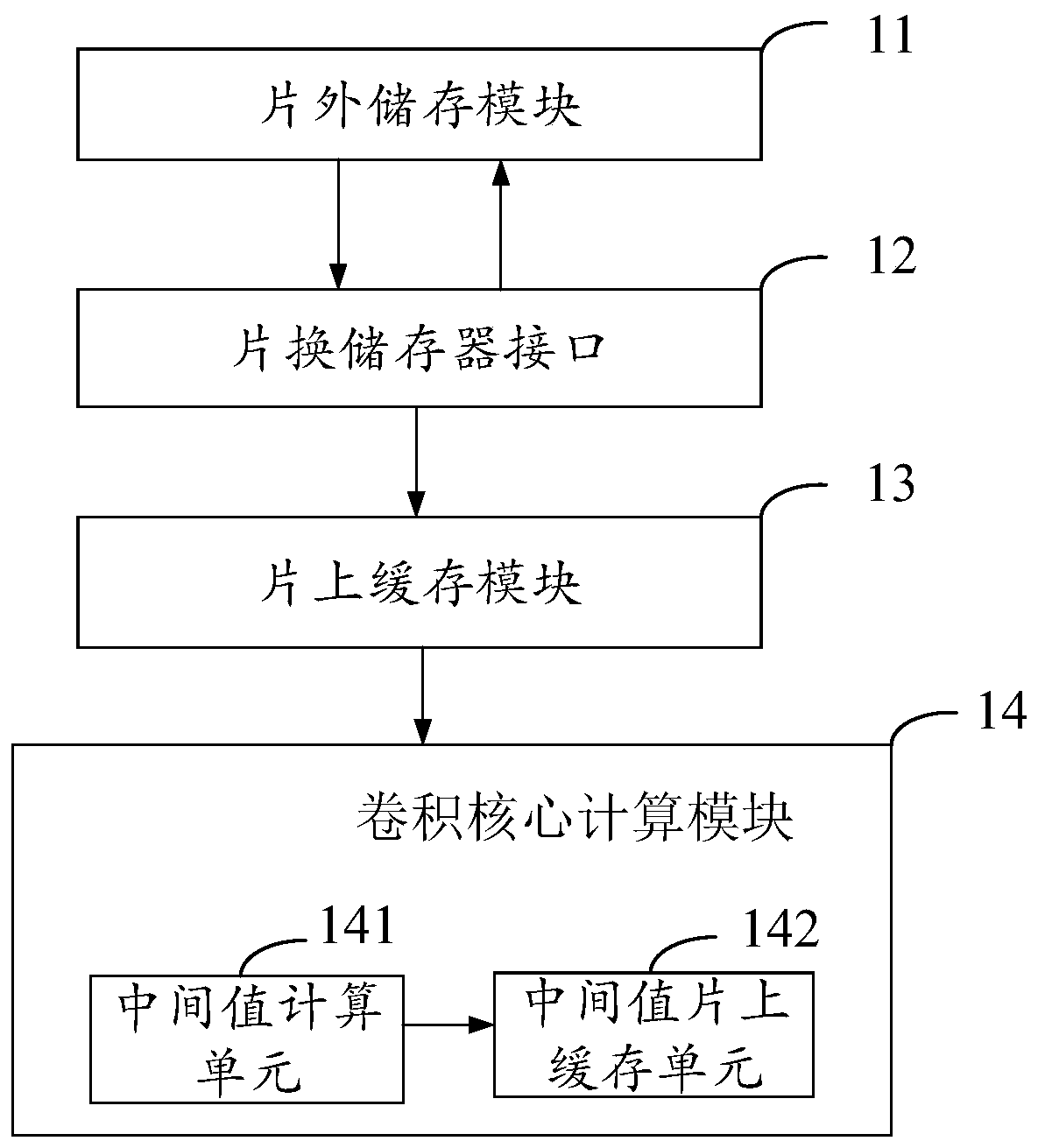

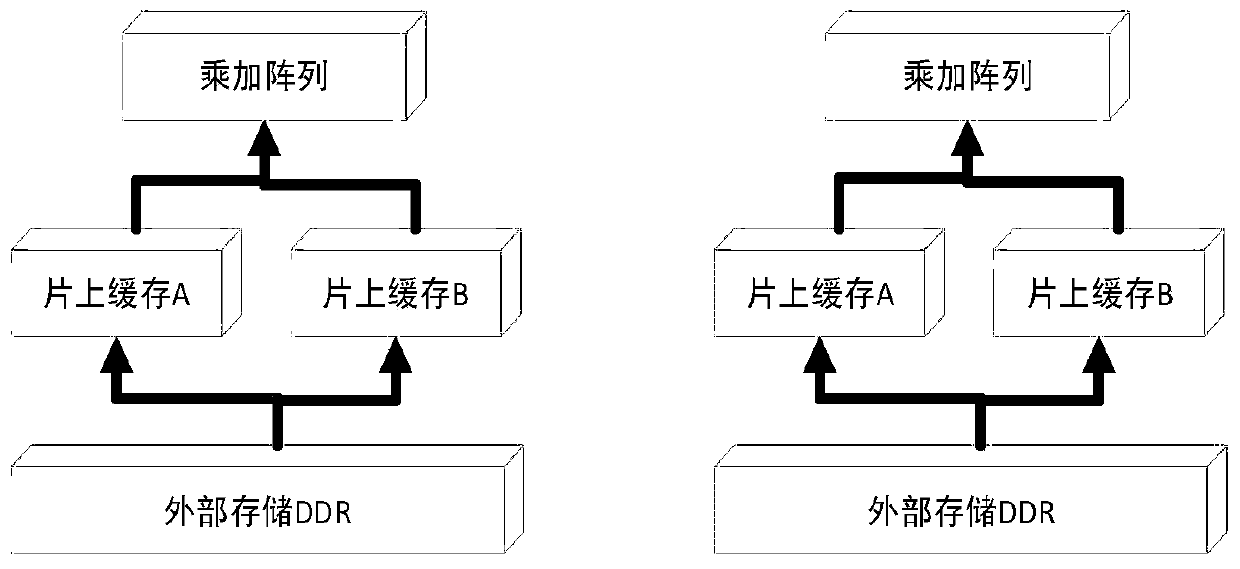

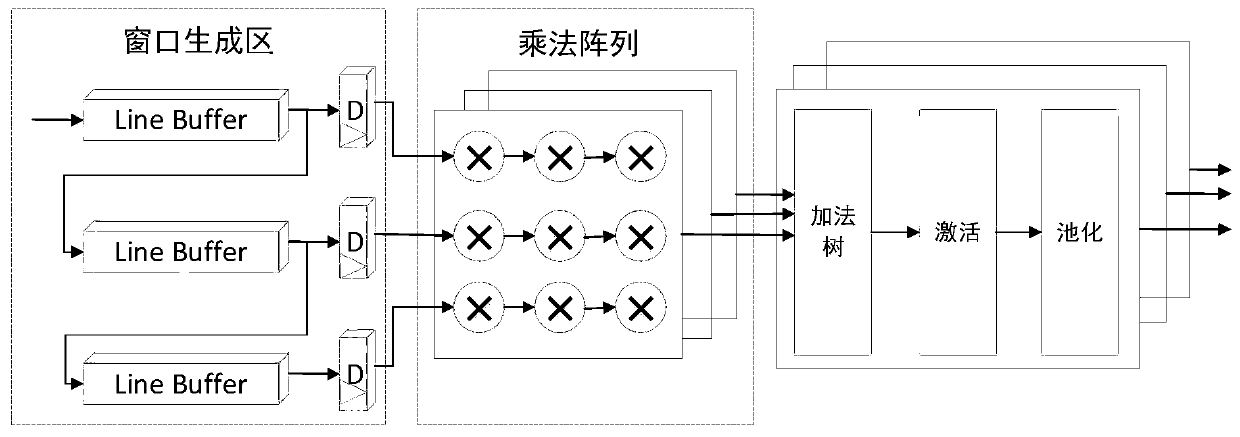

Convolutional neural network acceleration processing system and method based on FPGA, and terminal

ActiveCN111582465AImprove efficiencyImprove throughputDigital data processing detailsProcessor architectures/configurationTerm memoryNetwork on chip architecture

The invention provides a convolutional neural network acceleration processing system and method based on an FPGA, and a terminal. The problems that in the prior art, the inherent computing characteristics of a convolutional neural network are mismatched with a network-on-chip architecture, the hardware acceleration efficiency is low, the parallelism difference of a network layer in different dimensions is large, and the memory access characteristics of different network layers are different are solved. The acceleration efficiency, the data throughput rate and the calculation energy efficiencyof the convolutional neural network on the FPGA are improved through an assembly line architecture, a customized multistage memory access strategy and convolutional parallel optimization.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

Fabric interconnection for memory banks based on network-on-chip methodology

ActiveUS11165717B2Lower latencyHigh densityInput/output to record carriersData switching networksComputer architectureEngineering

Embodiments disclosed herein generally relate to the use of Network-on-Chip architecture for solid state memory structures, both volatile and non-volatile, which provide for the access of memory storage blocks via a router. As such, data may be sent to and / or from the memory storage blocks as data packets on the chip. The Network-on-Chip architecture may further be utilized to interconnect unlimited numbers of memory cell matrices, spread on a die, thus allowing for reduced latencies among matrices, selective power control, unlimited memory density growth without major latency penalties, and reduced parasitic capacitance and resistance. Other benefits may include improved signal integrity, larger die areas available to implement memory arrays, and higher frequency of operation.

Owner:WESTERN DIGITAL TECH INC

Fault-based three-dimensional optical on-chip network architecture, communication method and optical router

ActiveCN107220209ASolve serious blocking problemsSolve the problem of uneven distribution of vertical interconnect linesMultiplex system selection arrangementsArchitecture with single central processing unitElectricityNetwork architecture

The invention provides a fault-based three-dimensional optical on-chip network architecture, a communication method and an optical router, which solve the technical problems of serious blockage in vertical direction, uneven TSV distribution, and big insert loss of a high order optical router in the prior art. The network architecture has seven layers totally, wherein the top layer is an optical network layer and integrated with NXN novel nine-port optical routers; the bottom layer is a pure electric layer and integrated with NXN five-port electric routers; every layer of the middle five layers is integrated with NXNX4 IP cores; the uppermost layer in the middle layers is a reference, and another four layers are staggered along four diagonal line directions respectively to form a fault mechanism; the optical router provides a high-order optical interconnection of the middle layers; the IP internuclear communication includes a node internal part, internal node of layer and interlayer communication; the communication between the inner part of the node and the inside of the layer is carried out through a middle layer optical network; the interlayer communication is realized through a top layer optical network or a bottom layer electric router. The invention solves the problem of serious blockage of vertical direction in a traditional 3D optical on-chip network; the communication between processor cores is high-efficient.

Owner:XIDIAN UNIV

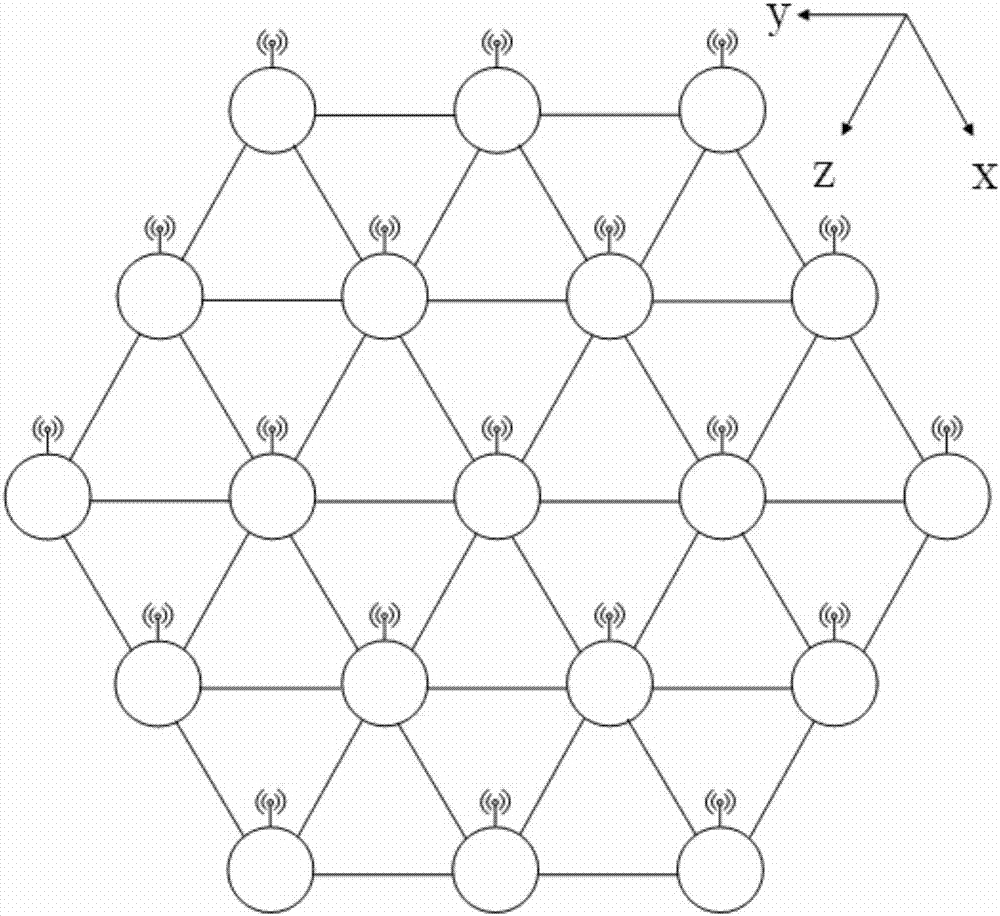

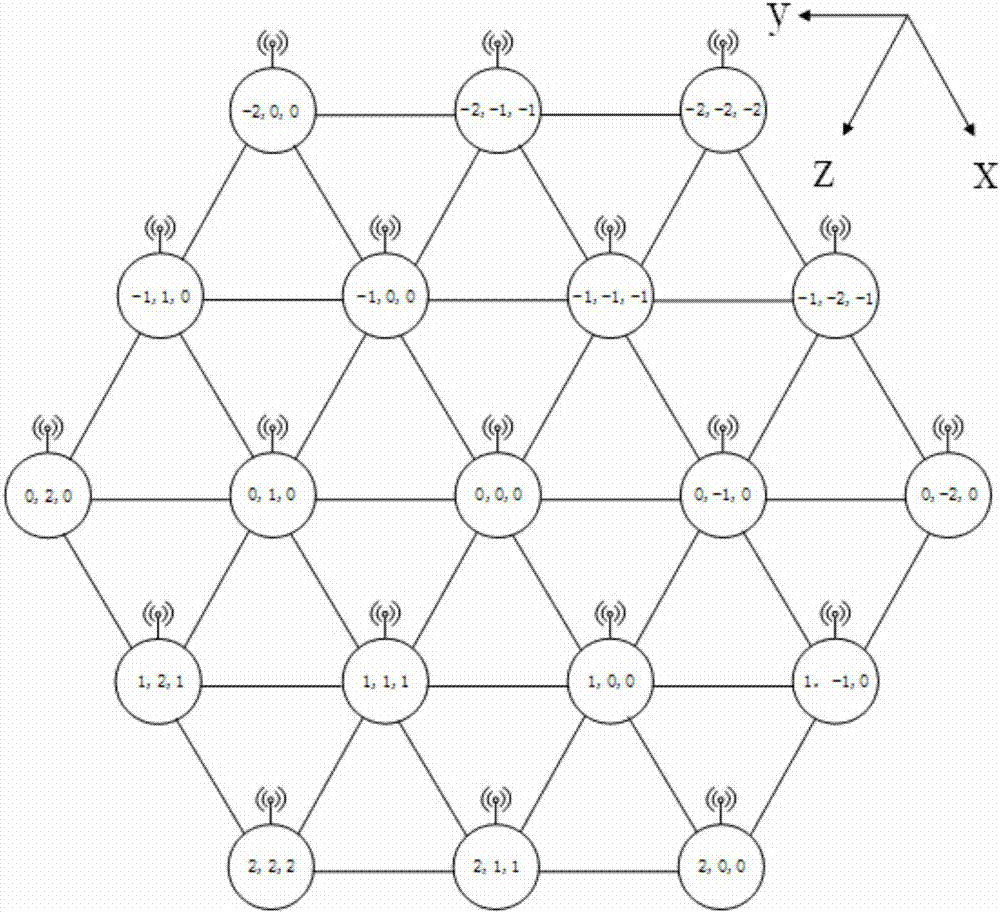

Network-on-chip architecture based on butterfly network coding and shortest path acquiring method of network-on-chip architecture

ActiveCN107517159AShort path routingAvoid deadlockData switching networksIsoetes triquetraCellular topology

The invention relates to the technical field of on-chip communication, in particular to a network-on-chip architecture based on butterfly network coding and a shortest path acquiring method of the network-on-chip architecture. The nodes of the network-on-chip architecture are distributed in a honeycomb manner, and each honeycomb is an equilateral triangle formed by the connecting lines of three adjacent nodes. The network-on-chip architecture has the advantages that the network-on-chip architecture based on butterfly network coding and Z-X-Y shortest-path routing matched with honeycomb topology can avoid deadlock and find out the shortest routing path; compared with traditional topological structures such as mesh topology, the honeycomb topology of the network-on-chip architecture has natural shortcuts and can reduce key link hop count; meanwhile, the network-on-chip architecture uses the butterfly network coding, can greatly eliminate network hot spots and can solve the problem of network congestion; the honeycomb network-on-chip architecture transmits data packets in a wireless manner and transmits control signals in a wired manner, data and the control signals are separated, and high-speed and efficient data transmission can be completed.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Multi-cast broadcast communication perception optical on-chip network architecture and communication method

ActiveCN109246493AReduce usageSmall area overheadMultiplex system selection arrangementsNetwork architectureNetwork communication

The invention proposes a multi-cast broadcast communication perception optical on-chip network architecture and a communication method, and is used for solving technical problems in the prior art thatan optical on-chip network architecture is higher in power consumption and is poorer in extendibility and the technical problems that a communication method is bigger in time delay and power consumption. In the optical on-chip network architecture, a processor module is divided into clusters which are arranged in an array, and each cluster comprises an array which is formed by 2*4 processor modules. Each processor module is coupled to one first active micro-ring resonator through a coupling port. The clusters in the array are connected through a snake-shaped optical waveguide structure, and are in unit extension. Meanwhile, the coupling distance distribution between the first active micro-ring resonator and the optical waveguide is set by a power separation system. In the communication method, a global control unit performs the processing of the communication request of the processor modules, and transmits the obtained control information to a multi-wavelength laser light source to perform the network communication configuration with the first active micro-ring resonator.

Owner:XIDIAN UNIV

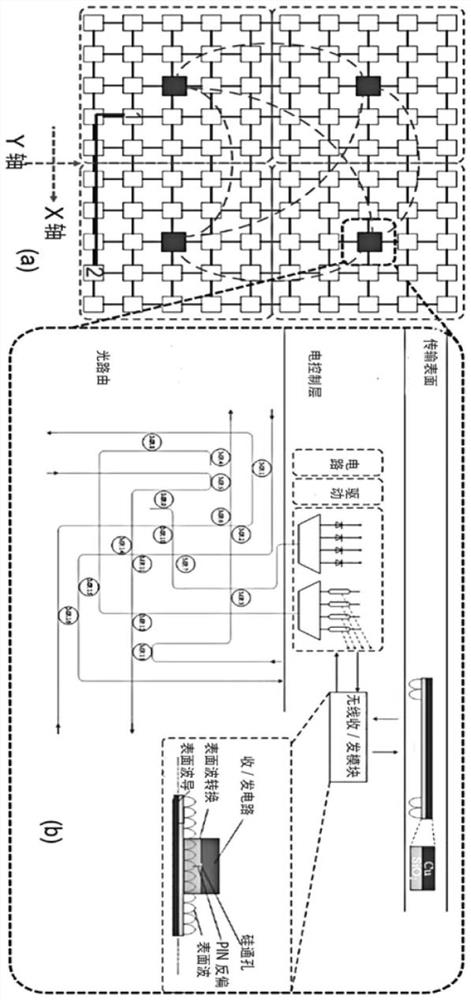

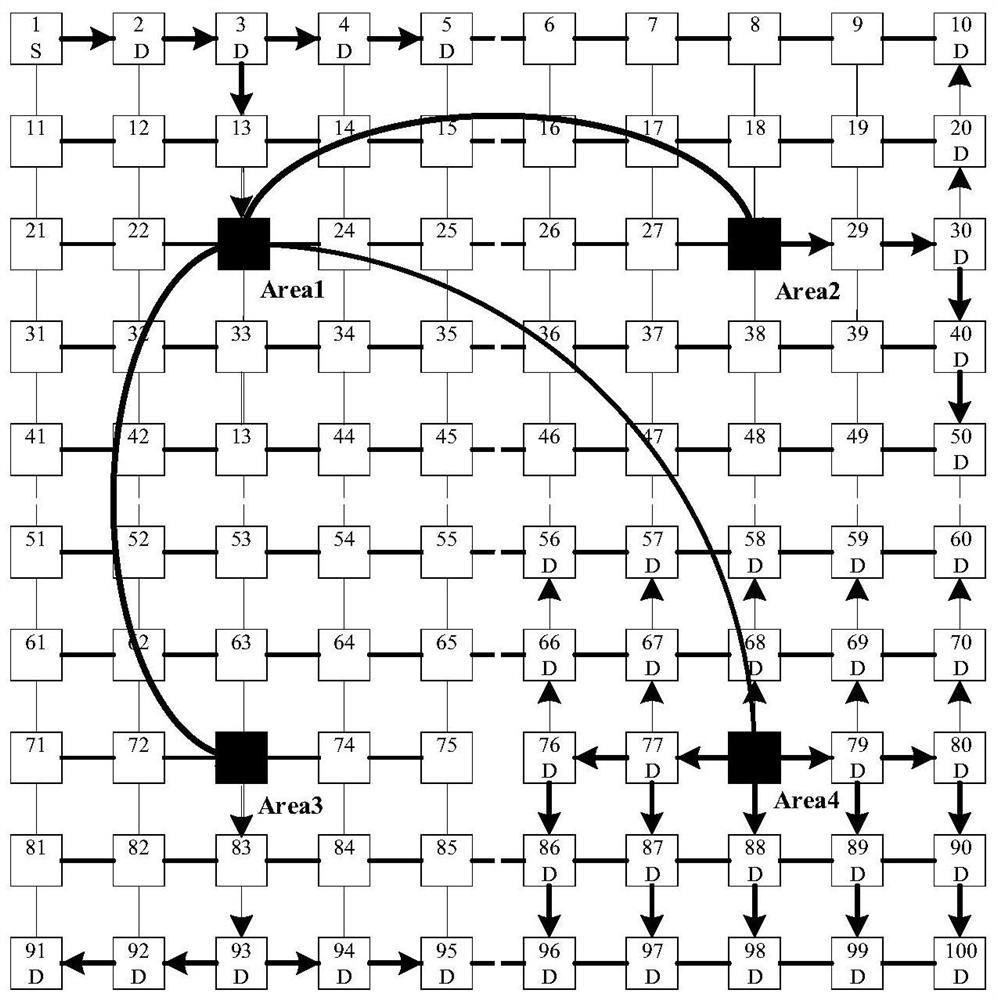

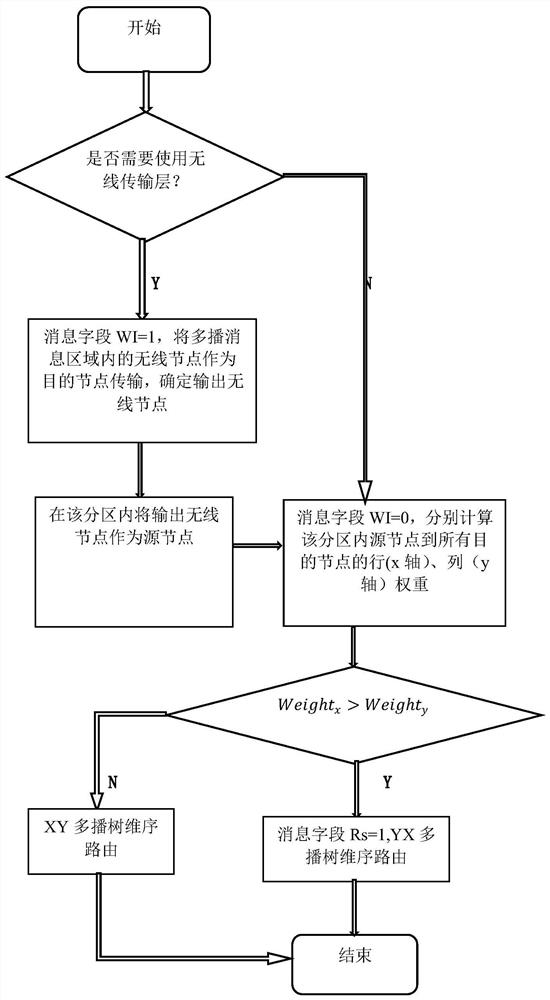

Hybrid wireless optical network-on-chip architecture and multicast routing algorithm thereof

ActiveCN111786911AImprove transmission efficiencyRelieve stressMultiplex system selection arrangementsData switching networksWireless transmissionTransport layer

The invention requests to protect a hybrid wireless optical network-on-chip architecture and a multicast routing algorithm thereof, and the hybrid wireless optical network-on-chip architecture comprises an optical transmission layer, an electric control layer and a wireless transmission layer, and adopts a waveguide structure suitable for Zenneck surface wave transmission and a Walsh coding technology. The corresponding multicast routing algorithm comprises a flexible allocation mechanism of the wireless transmission layer and the optical transmission layer and a multicast routing mechanism based on node distribution in a partition. Compared with a traditional ONoC multicast routing method, the algorithm provided by the invention has better performance in the aspects of average hop count (average time delay) and the like.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Network-on-chip architecture for multi-processor soc designs

ActiveUS20140344501A1Digital computer detailsElectric digital data processingTelecommunicationsMulti processor

A system and method embodying some aspects for communicating between nodes in a network-on-chip are provided. The system comprises a microprocessing chip and a plurality of connection paths. The microprocessing chip comprises sixteen processing nodes disposed on the chip. The plurality of connection paths are configured such that each is at most three hops away front any other node. Each node also has connection paths to at most three other nodes.

Owner:ADVANCED MICRO DEVICES INC

Three-dimensional optical network-on-chip router communication system and method based on wavelength allocation

ActiveCN105451103BReduce usageReduce blocking rateMultiplex system selection arrangementsData switching networksNetwork architectureNetwork on chip architecture

The invention relates to a wavelength-allocation-based three-dimensional optical on-chip network router communication system and method. The communication system employs a photoelectric mixing type 3D mesh network topological structure and a novel seven-port clog-free optical router capable of realizing multi-wavelength communication; and when the system is applied to a three-dimensional optical on-chip network, no wavelength conversion is needed. Because of utilization of the optical router, the consumed number of optical devices like micro ring resonators and waveguides and the like is reduced. Besides, according to the communication method, when a node of each layer sends out an optical signal, the employed wavelengths are identical; and optical signals with all wavelengths can be received at all layers, so that problems of severe network congestion, low link utilization rate, and limited expansibility due to utilization of single wavelength communication by the existing optical on-chip network architecture can be solved. Therefore, with the system and method, the network congestion probability can be reduced; the communication delay can be reduced; and the throughput capacity and network saturation point can be improved.

Owner:XIDIAN UNIV

Topology structure and wavelength allocation method of staggered-layer 3D optical-on-chip network

ActiveCN106126471BReduce the numberReduce blocking rateMultiplex system selection arrangementsArchitecture with single central processing unitDistribution methodDiagonal

The invention provides a topological structure based on a staggered three-dimensional light network-on-chip and a wavelength distribution method, and aims to solve the technical problems of serious blockage in the network and high loss in the prior art. The topological structure comprises two layers of 2D-Mesh light networks-on-chip and an interlaminar router; the light networks-on-chip comprise NxN routers connected through optical waveguides; each router is connected with an IP core; the two layers of light networks-on-chip are staggered from each other along the corresponding diagonals, and optical waveguides are added into the light networks-on-chip corresponding to gaps in four single-layer parts on the staggering edges along the optical waveguide directions in the light networks-on-chip; and the interlaminar router is arranged at a position perpendicular to the space where the optical waveguides of the different layer are positioned. The wavelength distribution method of the topological structure comprises the following steps: firstly establishing a three-dimensional coordinate system, and selecting wavelength values; secondly, distributing the wavelength values to all nodes; and finally, configuring a working offset state and temperature of an exchange microring resonator or an interlaminar microring coupler according to the wavelength values distributed to all the nodes.

Owner:XIDIAN UNIV

Intensive operation-oriented hierarchical heterogeneous multi-core on-chip network architecture

ActiveCN102497411BTake full advantage of parallel communication performanceGuaranteed transmission speedTransmissionCommunication interfaceDirect memory access

The invention discloses an intensive operation-oriented hierarchical heterogeneous multi-core on-chip network architecture. The top layer of the architecture is integrated with multiple operation clusters, a transposition cluster, a communication interface and a global sharing storage unit by use of a two-dimensional grid on-chip network; a bus architecture is adopted in the operation clusters and the transposition cluster on the bottom layer; the internal bus of each operation cluster is integrated with various operation units and direct memory access, a network interface and an in-cluster sharing storage unit; and the internal bus of the transposition cluster is integrated with a processor core, direct memory access, a network interface and an in-cluster sharing storage unit. The architecture disclosed by the invention can support multiple groups of global sharing storage units which are independent from each other; each global sharing storage unit can be integrated to the on-chip network through multiple network interfaces; the in-cluster sharing storage units are distributed in the operation clusters and the transposition cluster; and the sharing storage units in the operation clusters are divided into multiple groups independent from each other. According to the invention, the communication performance, data processing capability and access bandwidth of the system can be effectively improved through the hierarchical multi-level architecture and multi-channel access.

Owner:NANJING UNIV

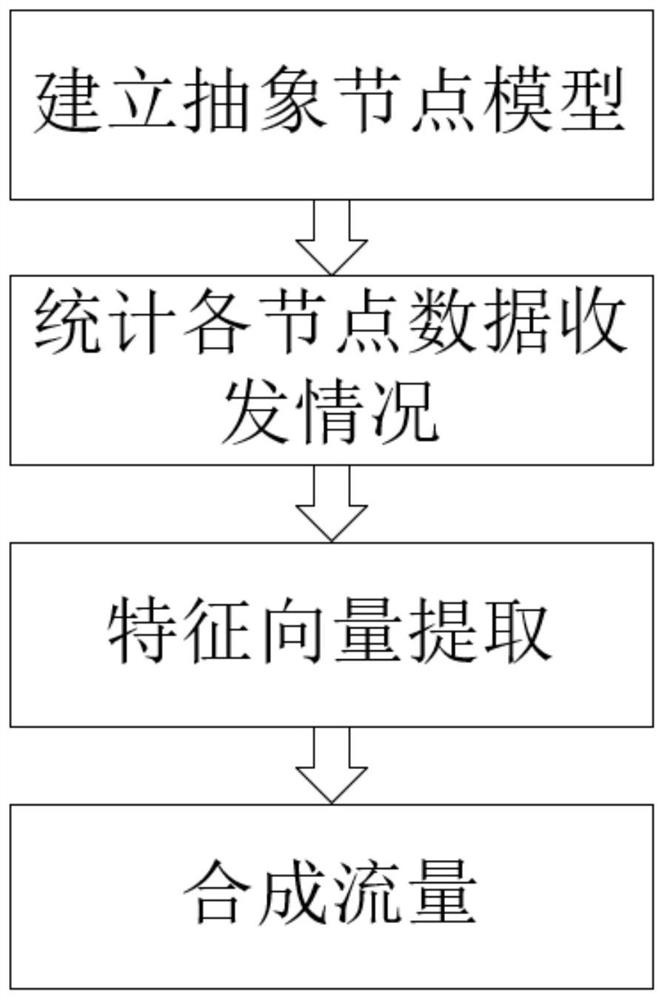

A Cache-Coherent Behavior-Based On-Chip Network Traffic Synthesis Method

ActiveCN108694156BAccelerate the discovery processShorten the timeDesign optimisation/simulationArchitecture with single central processing unitData packInternet traffic

The invention discloses an on-chip network traffic composition method based on cache consistency behavior. The steps are to abstract the CPU, cache, and directory into a node model; through the whole system simulation, count the sending and receiving of routing node data packets generated by the cache consistency constraints in the network-on-chip architecture; extract and reflect the time distribution characteristics and spatial distribution characteristics of application traffic The eigenvectors of ; based on the eigenvectors, the on-chip network traffic is synthesized using a Markov modulation model. The present invention can quickly provide accurate on-chip network traffic, save the time for the whole system to simulate and collect traffic, and accelerate the exploration process of on-chip network architecture. The network traffic synthesized by this method is consistent with the real network traffic in terms of time distribution and space distribution characteristics, which is enough to assist the design of the network-on-chip architecture.

Owner:SOUTHEAST UNIV +1