Intensive operation-oriented hierarchical heterogeneous multi-core on-chip network architecture

A network-on-chip and heterogeneous multi-core technology, which is applied to electrical components, transmission systems, etc., can solve the problems that the network-on-chip architecture cannot meet practical applications well, and achieve good practical application value, strong data processing capabilities, and improved communication performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

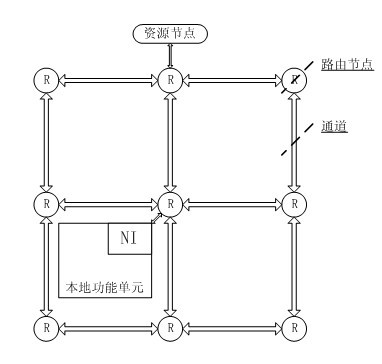

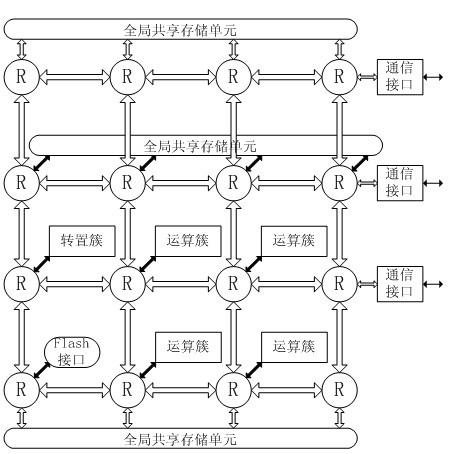

[0025] Such as figure 2 The hierarchical heterogeneous multi-core architecture shown is an example of the present invention. The size of the network-on-chip is 4×4, and the top-level two-dimensional grid network-on-chip integrates 4 computing clusters, 1 transposition cluster, and 3 sets of global Shared storage unit and 3 communication interfaces. The bottom layer uses a bus architecture inside the operation cluster and transpose cluster.

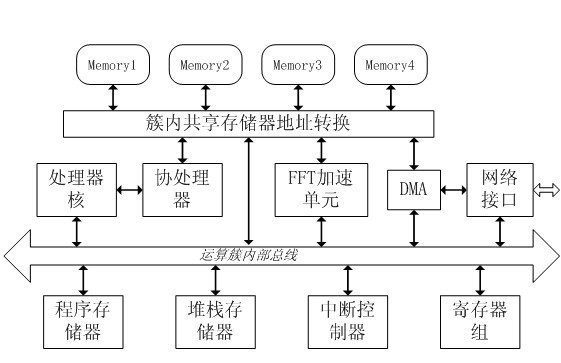

[0026] The specific structure of the operation cluster is as follows image 3 As shown, in addition to the bus, processor core, coprocessor core, FFT acceleration unit, direct memory access (DMA), network interface and shared storage unit in the cluster, 4 memory groups (Memory1, Memory2, Memory3 and Memory4), It also includes program memory, stack memory, interrupt controller, register bank and share...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More