Multi-cluster network-on-chip architecture based on statistic time division multiplexing technology

A time division multiplexing, on-chip network technology, applied in the field of statistical time division multiplexing (Statistical Time Divisio), can solve the problems of affecting the overall performance of the system, consuming a lot of time, waiting for the right to use the bus, etc., so as to reduce communication delay and network load. , the effect of improving system communication capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

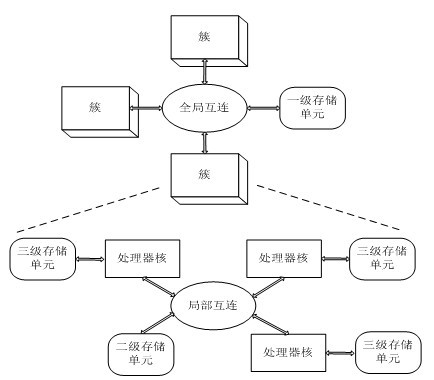

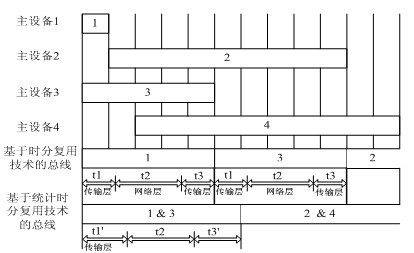

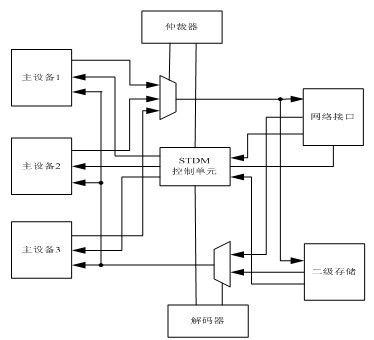

[0046] In order to verify the present invention, a cycle-accurate system-level simulation model based on SystemC language is built. The model uses as Figure 7 The 2D grid architecture shown. Among them, the network size can be parameterized and configured, and the local subsystems are divided into two categories, namely image 3 The computing cluster based on STDM technology and the storage cluster composed of Memory Level 1 are shown, and the number of Masters in the computing cluster can also be parameterized and configured. The structure of each Master in this model is as follows Figure 8 shown.

[0047] In this experiment, the upper limit of the number of Master applications (n_max) that can be recorded in the STDM Controller is set to 4, and the upper limit of the waiting time is set to 30 clock cycles.

[0048] In this embodiment, we mainly focus on the impact of the present invention on network load and execution time.

[0049] (1) Network load

[0050] Such as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More