A Cache-Coherent Behavior-Based On-Chip Network Traffic Synthesis Method

A network-on-chip and synthesis method technology, which is applied to general-purpose stored program computers, architectures with a single central processing unit, instruments, etc., can solve problems such as low accuracy, increased time-consuming architecture evaluation, poor flexibility, etc., to save time , saving simulation time and speeding up the exploration process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings.

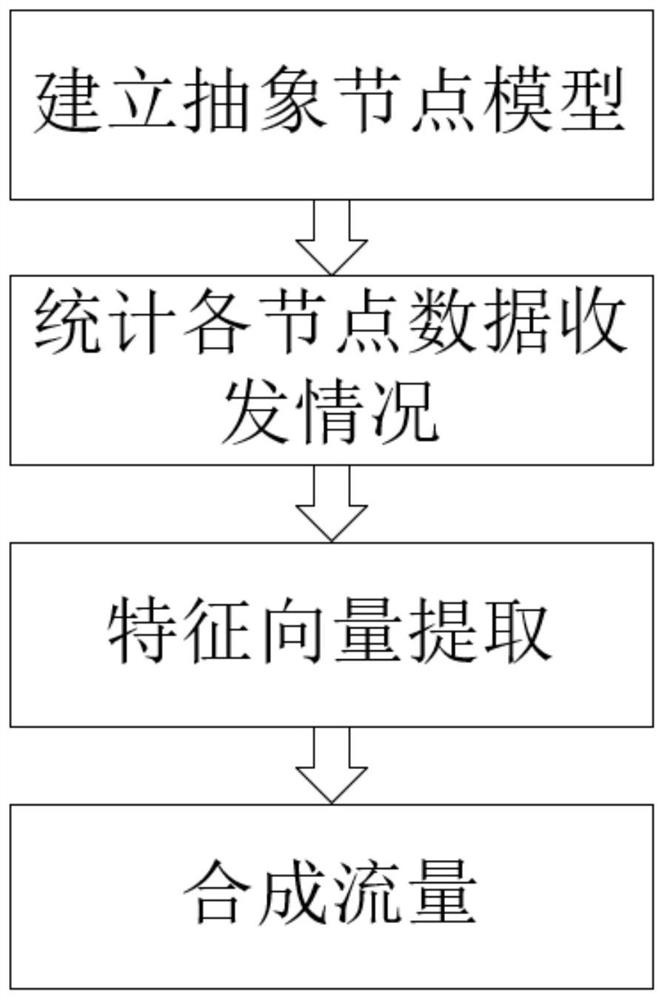

[0046] The present invention designs an on-chip network traffic composition method based on cache consistency behavior, such as figure 1 As shown, the steps are as follows.

[0047] Step 1: Abstract CPU, cache and directory into a node model.

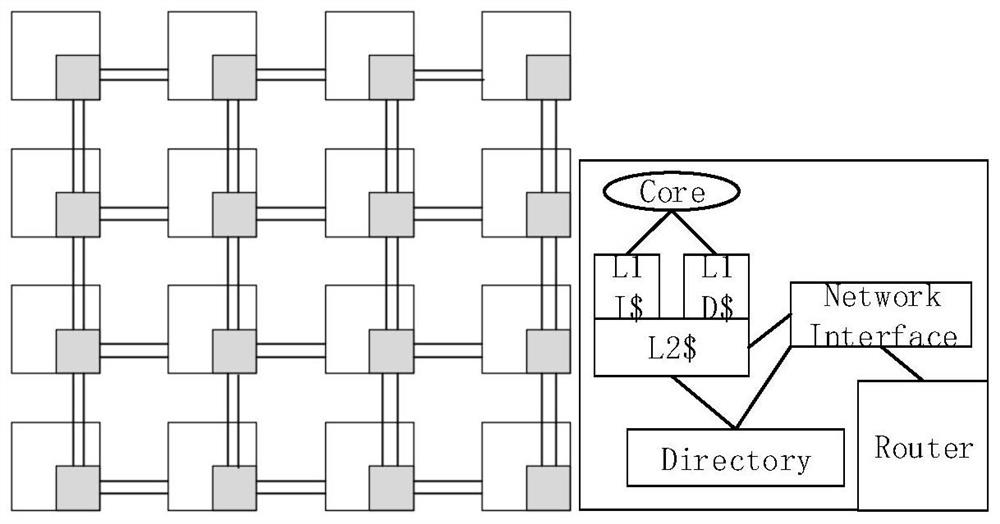

[0048] Ignoring the detailed differences between the CPU core, L1 cache and L2 cache, the CPU, cache and directory are respectively abstracted into node models in the network architecture. Nodes are connected to form a homogeneous multi-core SoC. Such as figure 2 As shown, the large squares in the figure represent the abstract node models of CPU, cache and directory respectively, the small squares represent routing nodes, and the lines between the small squares represent the channels for transferring data between routing nodes. figure 2 The right side represents an abstract node model including...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More