Network-on-chip architecture based on butterfly network coding and shortest path acquiring method of network-on-chip architecture

A butterfly network and network-on-chip technology, which is applied in data exchange networks, digital transmission systems, electrical components, etc., can solve the problems of power consumption and interconnection speed that cannot meet the requirements of on-chip communication, wireless interface transmission distance inconsistency, subnet high delay and Reduce the transmission rate and other issues, achieve the effect of shortening the number of key link hops, solving network congestion, and high-speed and efficient data transmission

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

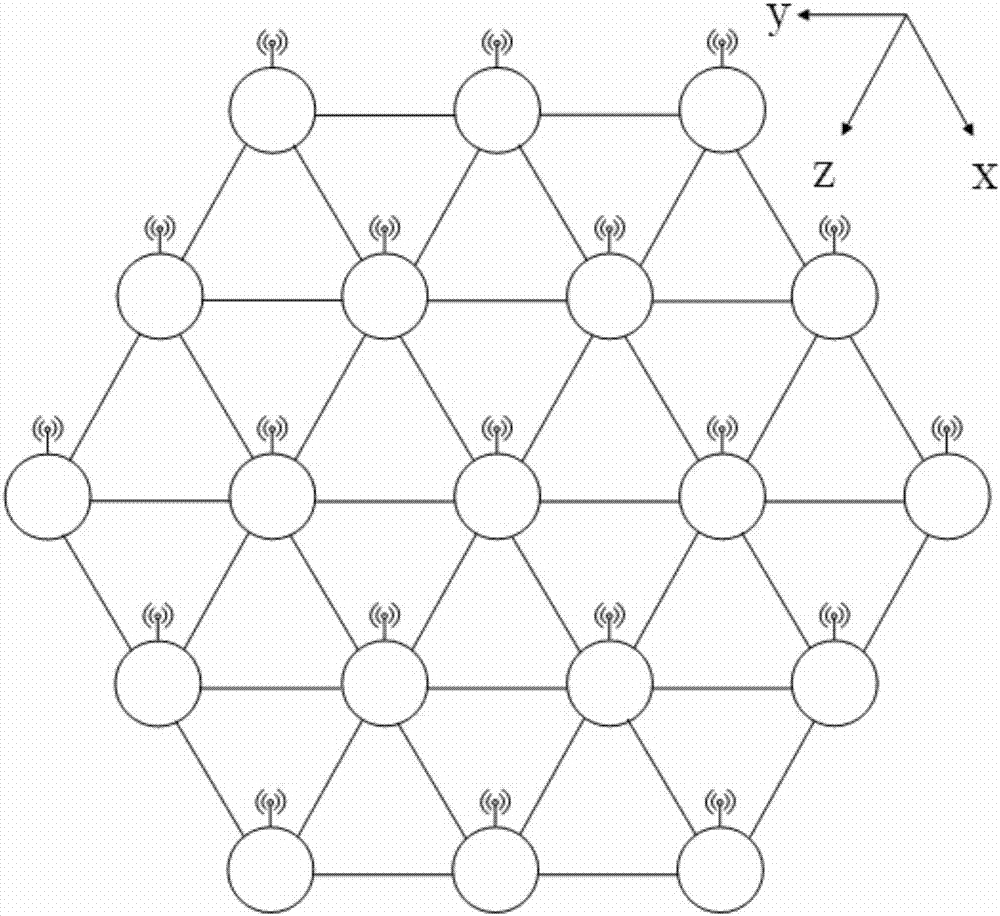

[0043] Embodiment 1: This embodiment provides an on-chip network architecture based on butterfly network coding, each node is distributed in a honeycomb shape, and each cell is an equilateral triangle formed by the connection lines of three adjacent nodes. In this architecture, control signals are transmitted in a wired manner; at the same time, data is transmitted in a wireless manner. figure 1 An illustration of this network-on-chip architecture with 19 nodes is given.

[0044]The state of the node includes idle state, sending state, direct forwarding state, encoding forwarding state and auxiliary state; among them, the node in the idle state does not process any data packets; the node in the sending state is sending data packets as the sending node; directly The node in the forwarding state is receiving the data packet sent by the sending node, and directly forwards the data packet without network coding; the node in the coding forwarding state is receiving data packets fro...

Embodiment 2

[0079] Embodiment 2: The present invention also provides a method for obtaining the shortest path between any two nodes when applying the above-mentioned network-on-chip architecture based on butterfly network coding, using one of any two nodes as the source node, The other serves as the destination node.

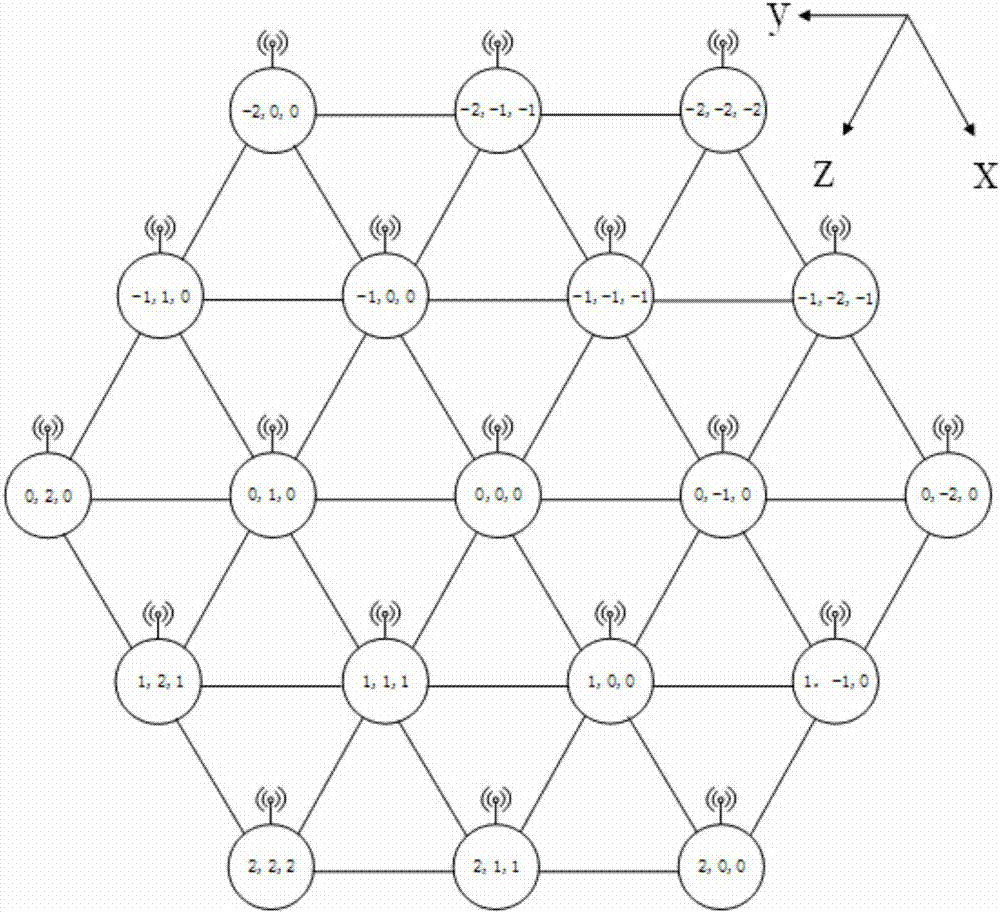

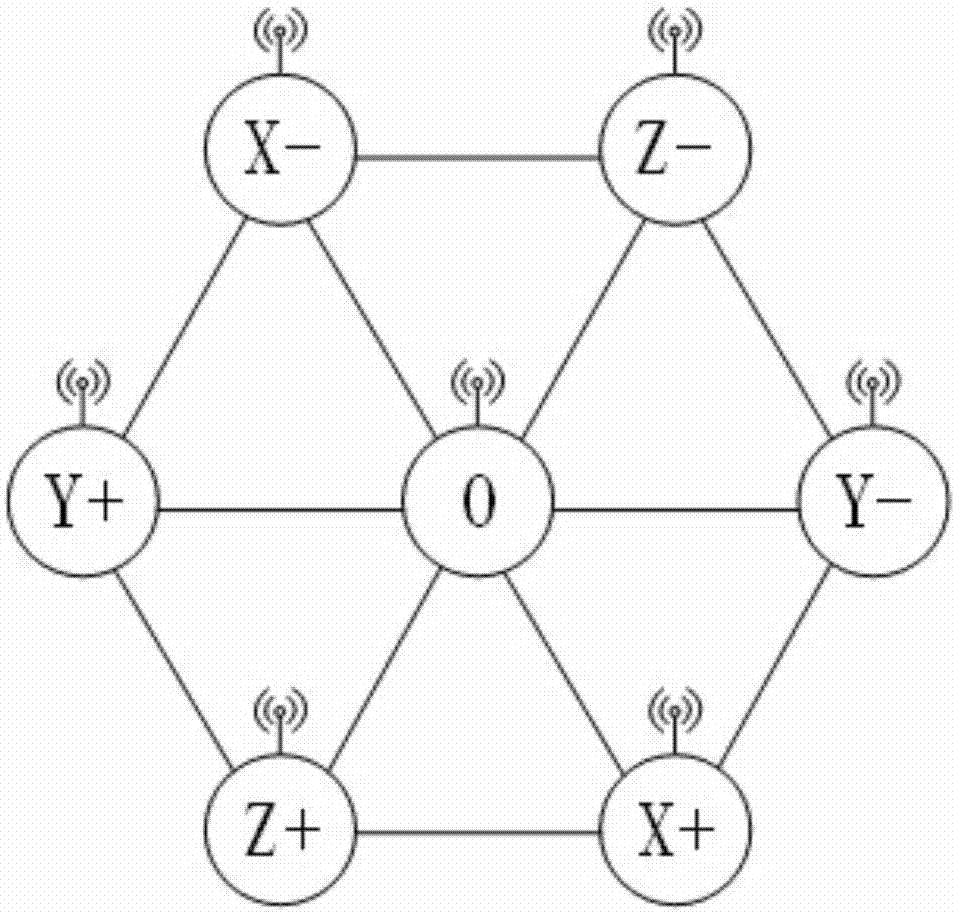

[0080] Set any node in the architecture as the original node, and set the coordinates of the original node as (0, 0, 0); set any connection between the original node and other nodes as the first connection, and set the Set the extension direction of a link as the positive direction of the x-axis, set the link obtained by rotating the original node 60 degrees with the first link as the second link, and set the extension direction of the second link is the positive direction of the z-axis, and the connection obtained by rotating the original node and the first connection by 120 degrees is named the third connection, and the extension direction of the third connection is set a...

example 1

[0091] Example 1: Get the manual figure 2 The node whose coordinates are (-1,1,0) is used as the source node, and the node whose coordinates are (2,0,0) is used as the destination node; the following process is used to calculate the shortest path between any two nodes:

[0092] Get the coordinates of the source node relative to the original node (x 1 ,y 1 ,z 1 )=(-1,1,0), to obtain the coordinates of the destination node relative to the original node (x 2 ,y 2 ,z 2 )=(2,0,0).

[0093] (1) Calculate the first relative number (x', y', z'), where x'=x 2 -x 1 =2-(-1)=3; y'=y 2 -y 1 =0-1=-1; z'=z 2 -z 1 =0-0=0.

[0094] (2) Judging whether p=x'*y'=-3 in the first relative number is greater than 0; if yes, enter step (3), otherwise enter step (5).

[0095] (3) by formula d z =min{|x'|,|y'|,|z'|} Calculate the distance d between the source node and the destination node on the z axis Z , min{} is the minimum value function; if z′>0, move the distance d in the positive ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More