Method for optimizing on-chip network structure by adding bypass in processor

An on-chip network and processor technology, applied in data exchange networks, machine execution devices, digital transmission systems, etc., can solve problems such as network inoperability, delay, deadlock, etc., and achieve function expansion, high efficiency, and reduced energy consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be further described below in conjunction with drawings and embodiments.

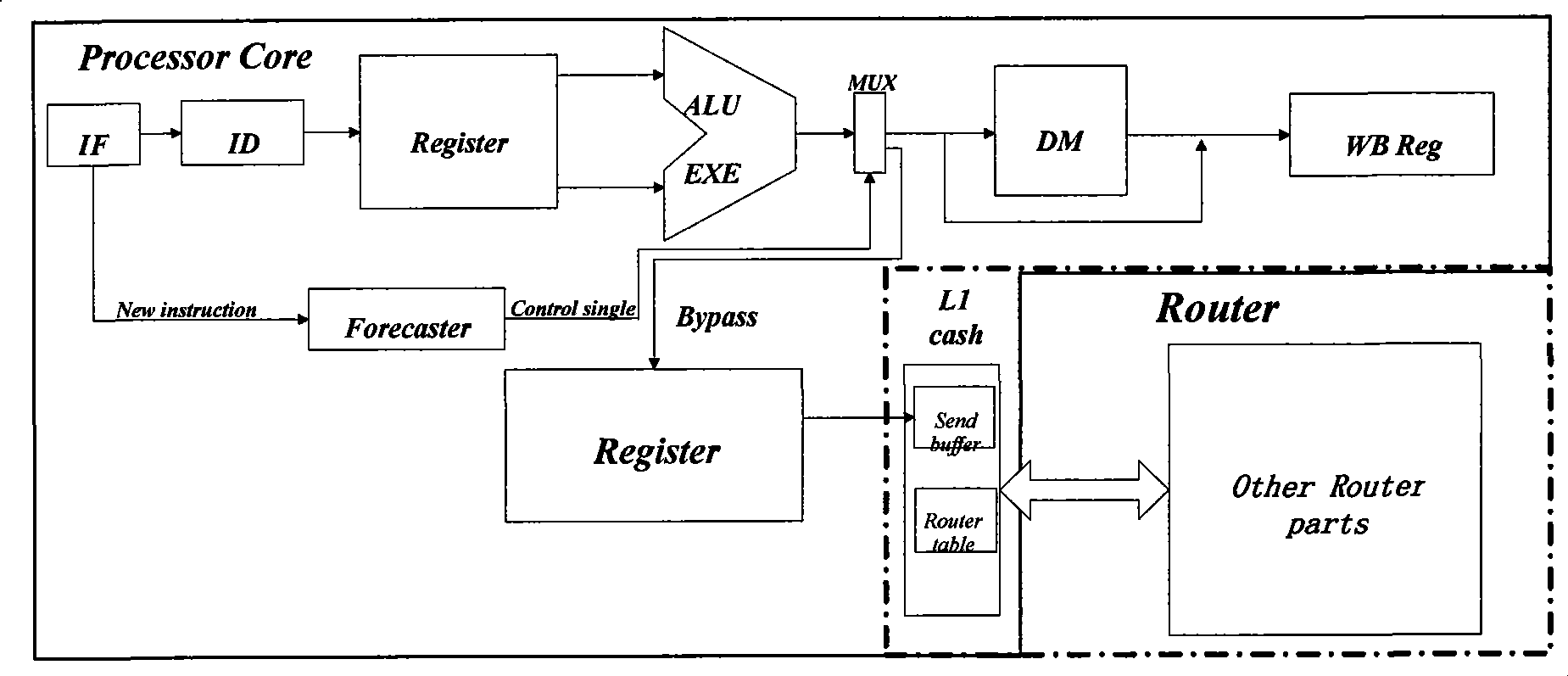

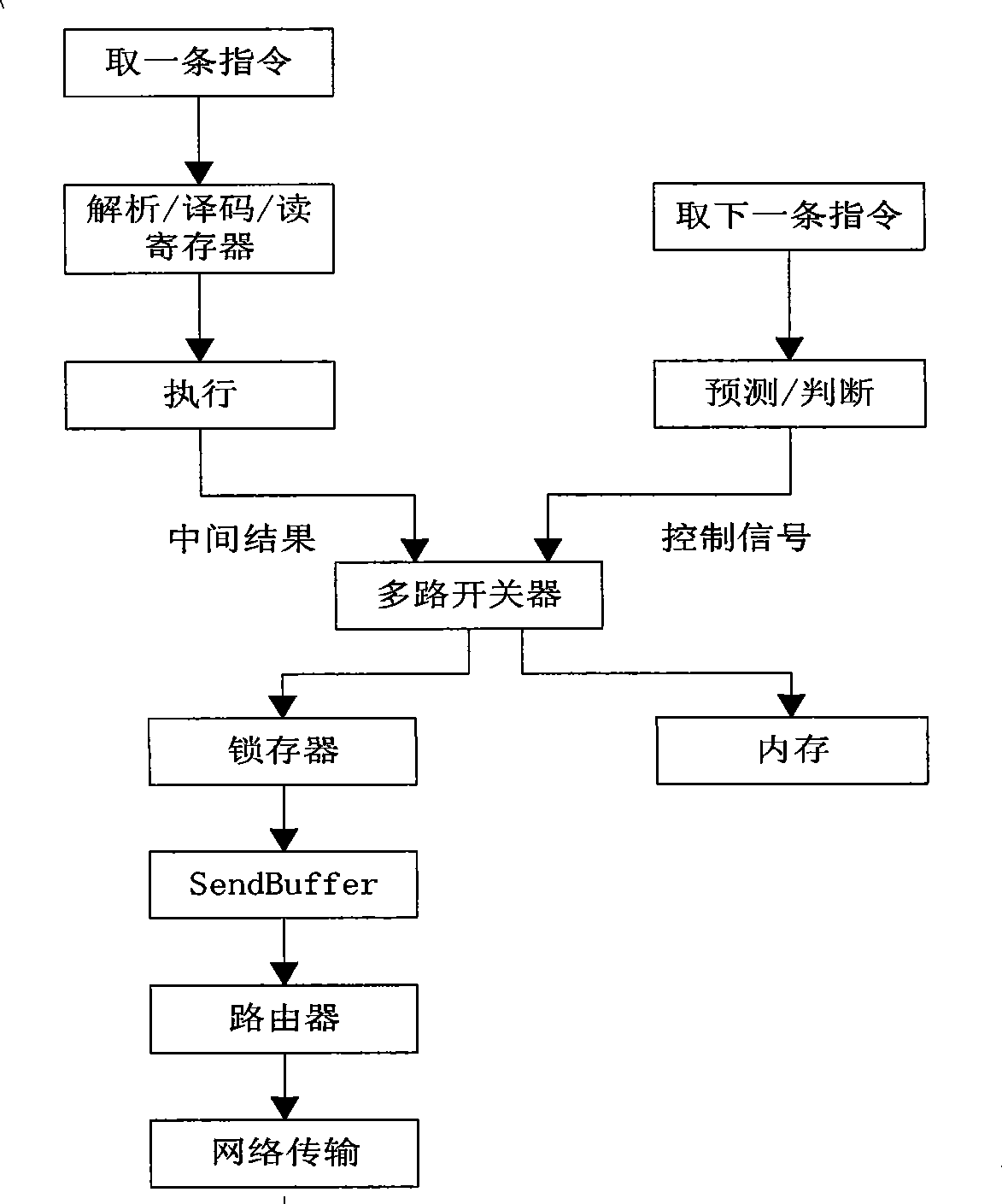

[0023] Processor core improvement and system-on-chip integration architecture can be divided into three modules: the improved processor module, the router module of the network on chip, and other modules of the network on chip. Since this method is optimized from the perspective of the processor and has no connection with other modules of the network on chip, only the first two modules are discussed below.

[0024] The improved processor module divides the processor into two parts: the processor part and the added module part. The processor module is in figure 1 Including IF (instruction fetching module), ID (instruction analysis / read register cycle), EXE (execution cycle), MEM (write back memory), WB (write back cycle), L1Cache module. The added modules mainly include Forecaster (prediction module), Register (latch module), including bypass and connected wires.

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More