Topology structure and wavelength allocation method of staggered-layer 3D optical-on-chip network

An optical on-chip network and topology technology, applied in the architecture with a single central processing unit, the selection device of the multiplexing system, the selection device, etc., can solve the problems of many cross nodes, blocking loss, large loss, etc. The effect of alleviating the blocking of chain building, reducing the blocking probability, and reducing the number of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Below in conjunction with accompanying drawing and embodiment, the present invention is described in further detail:

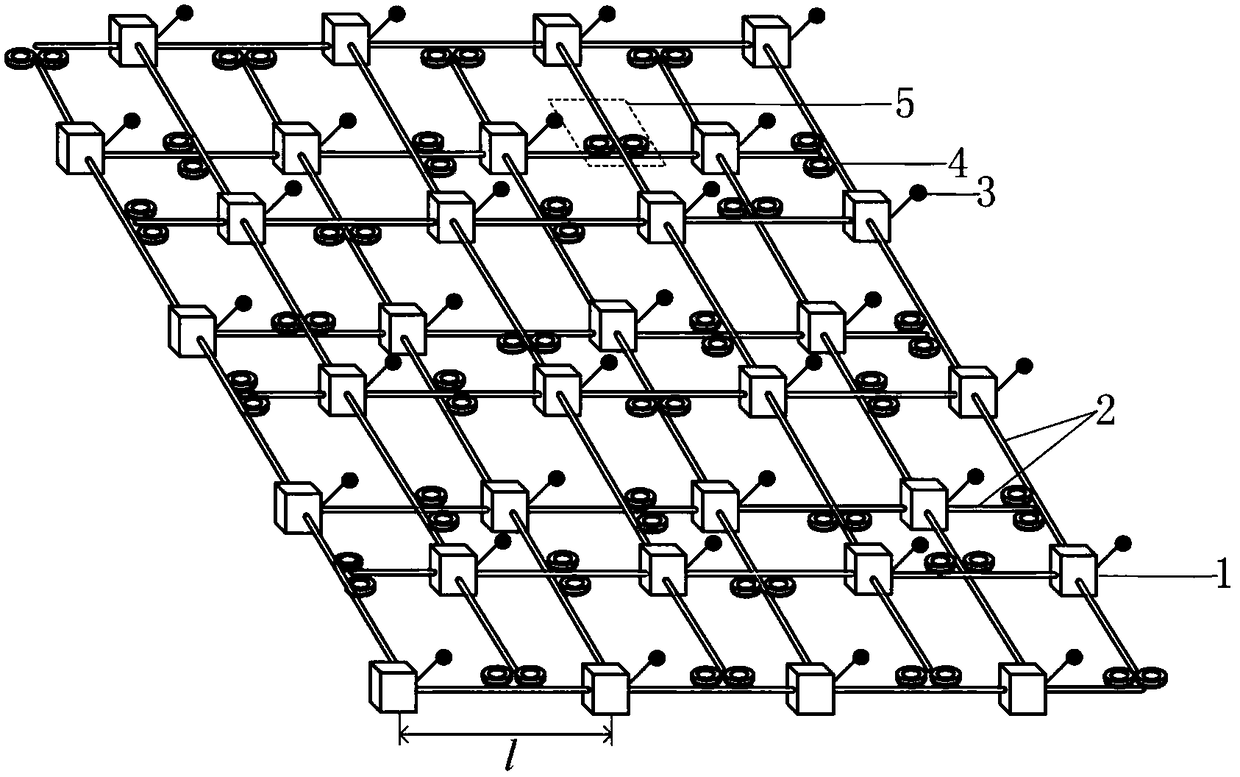

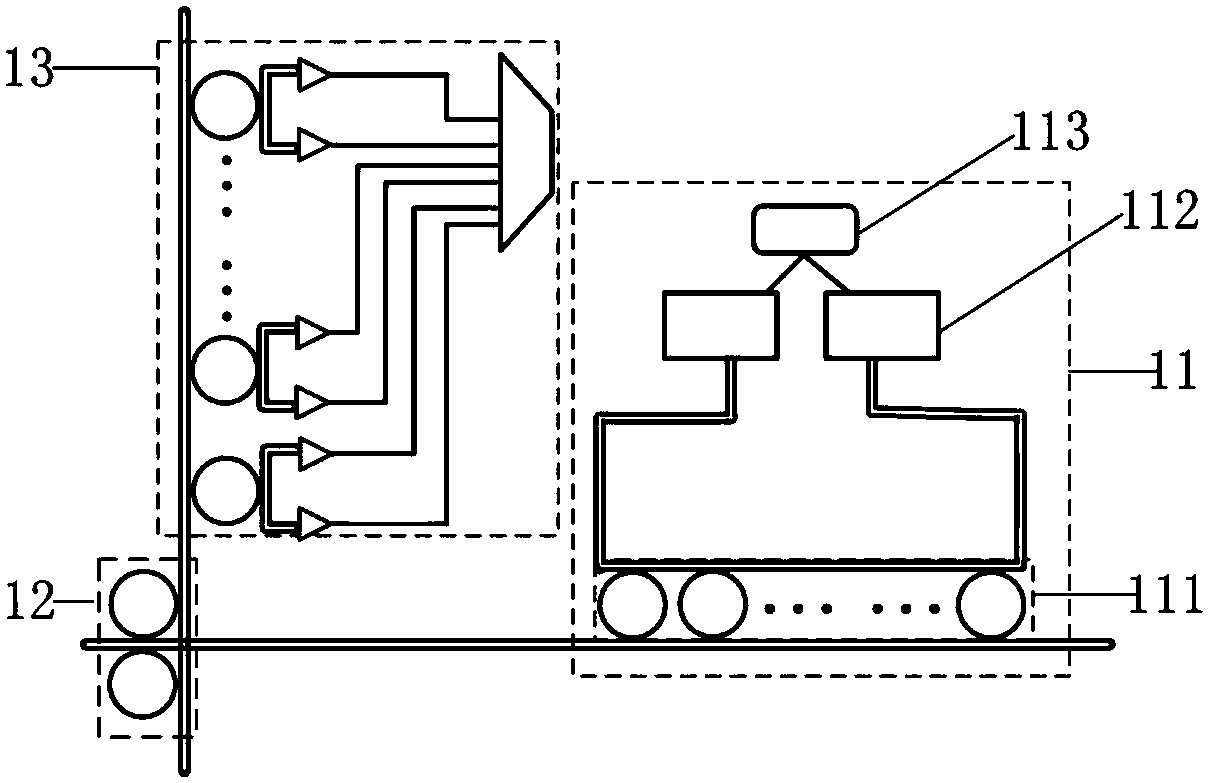

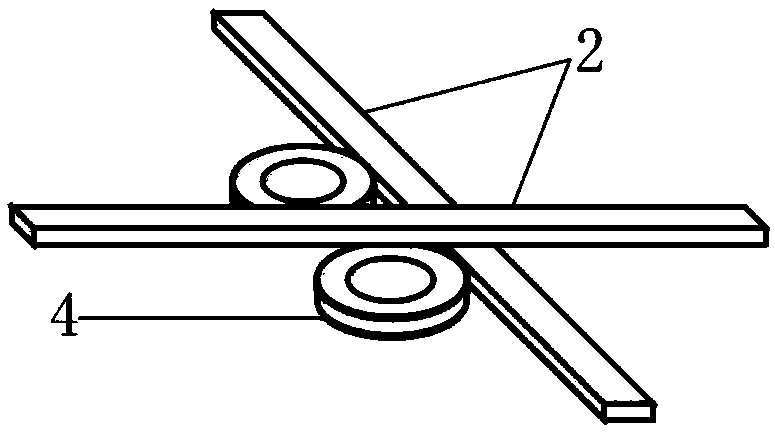

[0032] refer to figure 1 , a topological structure based on a staggered three-dimensional optical network on chip, including upper and lower layers of optical network on chip, each layer of optical network on chip includes a 2D-Mesh topology composed of 4×4 routers 1, where the structure of router 1 Such as figure 2 As shown, adjacent routers 1 are connected through optical waveguides 2, and each router 1 is connected to an IP core 3 through electrical wires. For the relative positional relationship between layers, in the vertical direction, an interlayer micro-ring coupler 4 is built between the upper optical-chip network and the lower optical-chip network; where l represents the distance between adjacent routers 1 in the 2D-Mesh topology. In the optical-on-chip network corresponding to the vacancies of the four single-layer parts at the edge of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More