data serialization circuit

A serialization, data technology, applied in parallel/serial conversion, electrical components, generation of electrical pulses, etc., can solve problems such as data quality degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

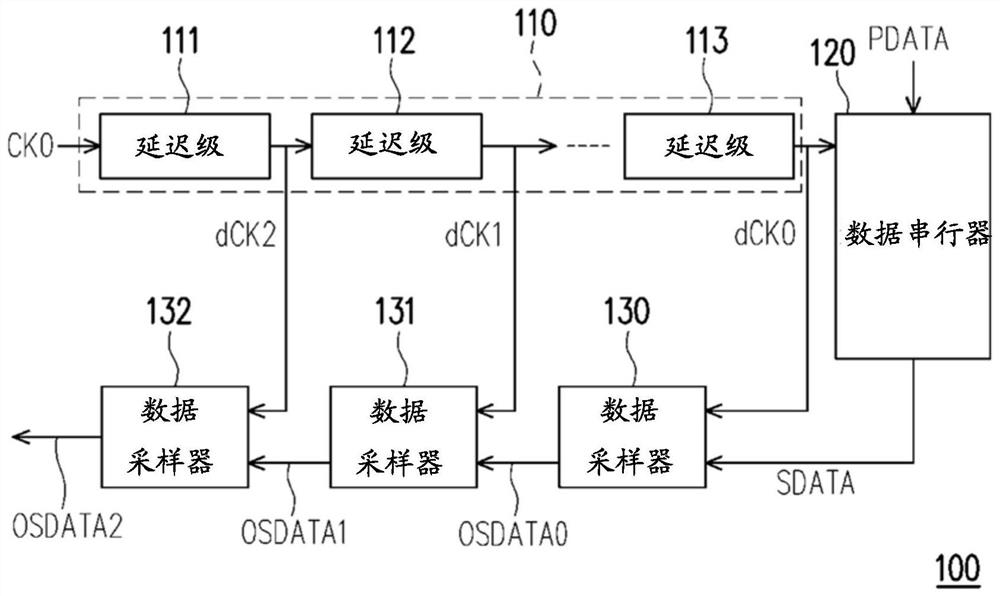

[0041] see figure 1 , figure 1 A schematic diagram illustrating a data serialization circuit 100 according to an embodiment of the present invention. The data serialization circuit 100 includes a delay circuit 110, a data serializer 120, and data samplers 130-132. The delay circuit 110 receives the input clock signal CK0 and generates a plurality of delayed clock signals dCK2-dCK0 by sequentially delaying the input clock signal CK0. Delay circuit 110 includes a plurality of delay stages, such as in figure 1 The three delay stages 111-113 are shown in . The delay stages 111-113 are coupled in series and generate delayed clock signals dCK2-dCK0 respectively. In this embodiment, the delayed clock signal dCK2 precedes the delayed clock signal dCK1, and the delayed clock signal dCK1 precedes the delayed clock signal dCK0. The delay stage 113 is the final delay stage, and the delayed clock signal dCK0 is the final stage delayed clock signal.

[0042] It can be seen that becaus...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More