Fan-out type package structure and preparation method thereof

A packaging structure, fan-out technology, used in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problem that the semiconductor chip is prone to shaking, affects the performance of the package structure, and the semiconductor chip has poor contact with the rewiring layer, etc. problem, to achieve the effect of increased adhesion, good contact, and guaranteed performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

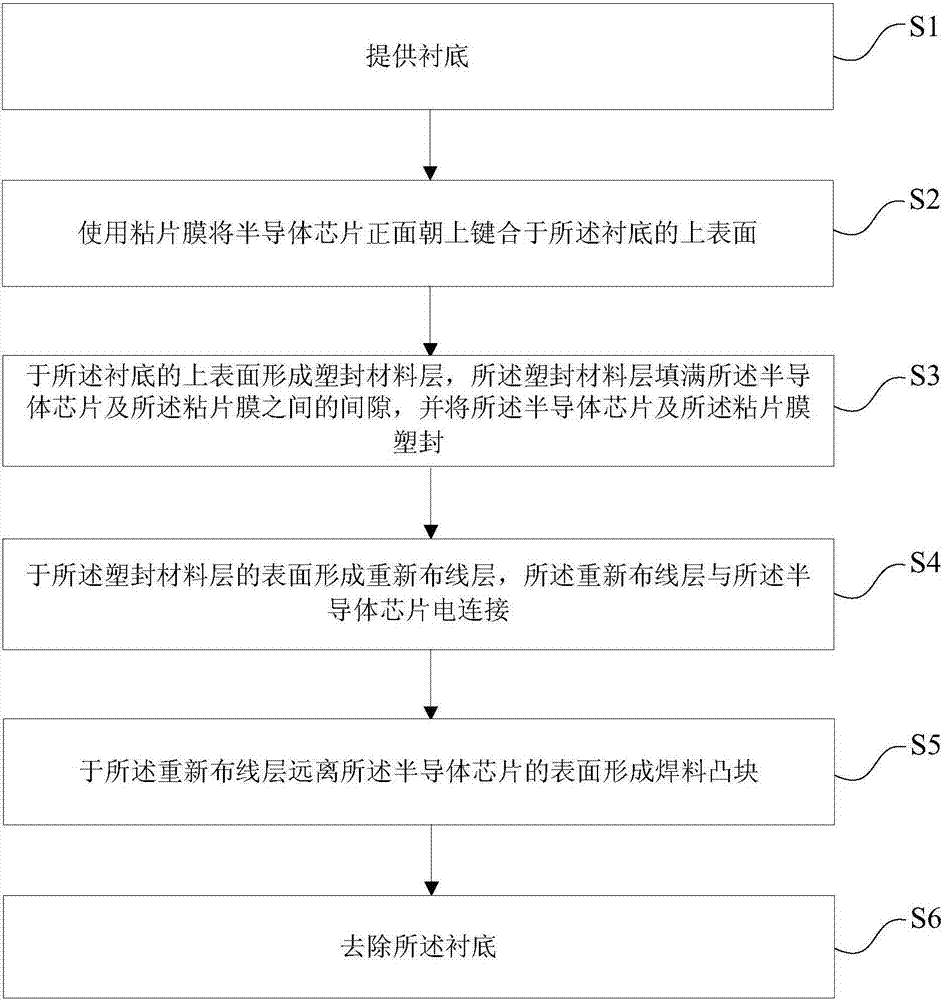

[0060] see figure 1 , this embodiment provides a method for preparing a fan-out packaging structure, the method for preparing a fan-out packaging structure includes the following steps:

[0061] 1) Provide the substrate;

[0062] 2) Bonding the semiconductor chip face up to the upper surface of the substrate using an adhesive film;

[0063] 3) forming a plastic sealing material layer on the upper surface of the substrate, the plastic sealing material layer fills the gap between the semiconductor chip and the adhesive film, and plastic seals the semiconductor chip and the adhesive film ;

[0064] 4) forming a rewiring layer on the surface of the plastic packaging material layer, the rewiring layer is electrically connected to the semiconductor chip;

[0065] 5) forming solder bumps on the surface of the rewiring layer away from the semiconductor chip;

[0066] 6) The substrate is removed.

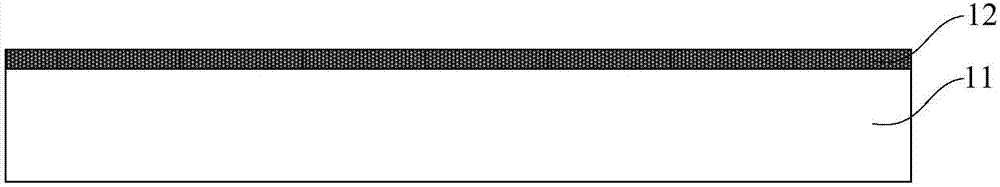

[0067] In step 1), see figure 1 Step S1 in and figure 2 , providing a substrate 11...

Embodiment 2

[0107] read on Figure 9 , this embodiment also provides a fan-out packaging structure, the fan-out packaging structure is prepared by the preparation method described in the first embodiment, the fan-out packaging structure includes: a rewiring layer 16, the The rewiring layer 16 includes opposite first surfaces and second surfaces; a semiconductor chip 13, the semiconductor chip 13 is located on the first surface of the rewiring layer 16, and the front side of the semiconductor chip 13 is connected to the rewiring layer. The layer 16 is electrically connected; the adhesive film 14, the adhesive film 14 is located on the back side of the semiconductor chip 13; the molding material layer 15, the molding material layer 15 is located on the first surface of the rewiring layer 16, the The plastic sealing material layer 15 fills up the gap between the semiconductor chip 13 and the adhesive film 14, and plastics the semiconductor chip 13 and the adhesive film 14; solder bumps 17, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More