Subthreshold SRAM (Static Random Access memory) unit circuit capable of increasing read noise tolerance and writing margin

A technology of memory cell circuit and noise tolerance, applied in the field of sub-threshold SRAM memory cell circuit, can solve the problems of limited improvement of 6T tube read and write ability, influence of memory cell process fluctuation, and decrease of memory cell stability, etc., so as to improve the write margin. high read and write noise tolerance, improved ability to write data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention is described in detail below in conjunction with accompanying drawing

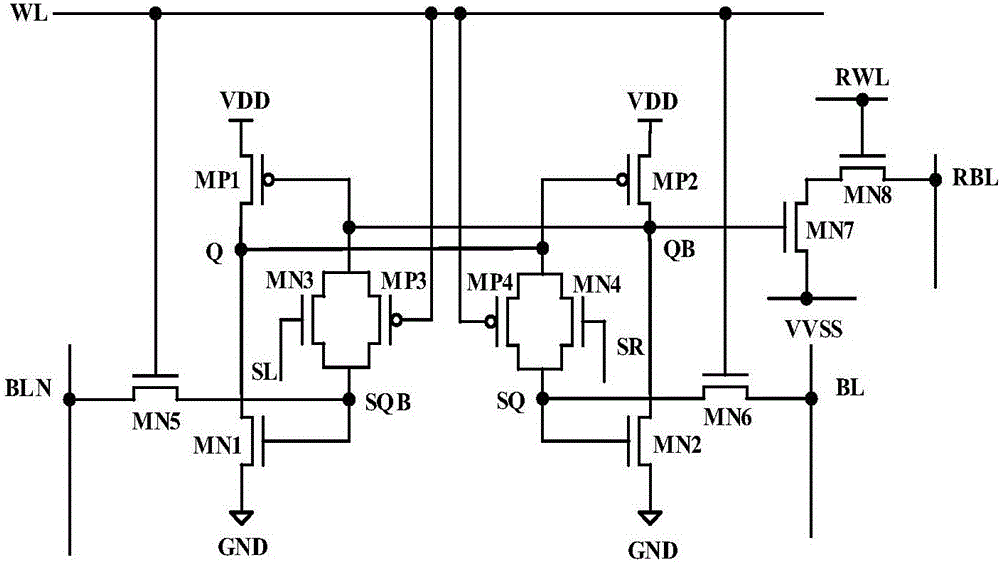

[0019] Such as figure 2 Shown is a schematic structural diagram of a sub-threshold SRAM memory cell circuit provided by the present invention to improve read noise tolerance and write margin, including a first NMOS transistor MN1, a second NMOS transistor MN2, a third NMOS transistor MN3, and a fourth NMOS transistor. Tube MN4, fifth NMOS tube MN5, sixth NMOS tube MN6, seventh NMOS tube MN7, eighth NMOS tube MN8, first PMOS tube MP1, second PMOS tube MP2, third PMOS tube MP3, fourth PMOS tube MP4 , the gates of the fifth NMOS transistor MN5, the sixth NMOS transistor MN6, the third PMOS transistor MP3 and the fourth PMOS transistor MP4 are connected to the word line WL, the drain of the fifth NMOS transistor MN5 is connected to the bit line other than BLN, and its source is connected to The gate of the first NMOS transistor MN1, the source of the third NMOS transistor MN3, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More