CMOS image data training system and image data serialization-deserialization simulation detection method

A technology of image data and training system, which is applied in the parts of TV system, image communication, parts of color TV, etc. It can solve the problems of indeterminate phase relationship and difficult data serial-to-parallel conversion, so as to improve application reliability, The effect of reducing the number of control signals and reducing the load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

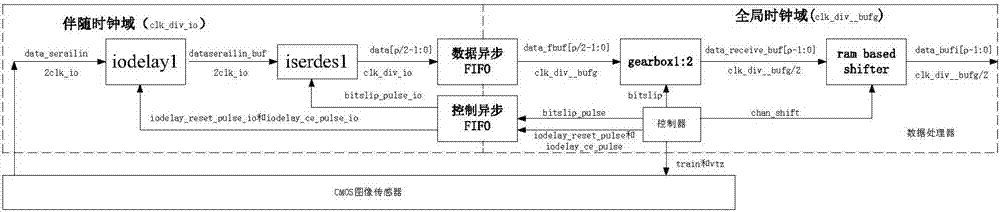

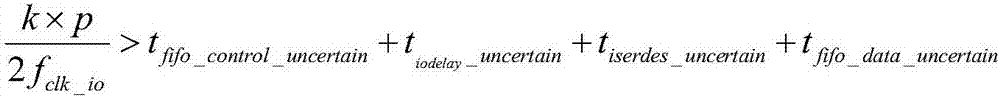

[0032] Specific implementation mode 1. Combination figure 1 and figure 2Illustrating this embodiment, a CMOS image data training system includes a CMOS image sensor and a data processor; the data processor is internally composed of a programmable delay element (iodelay), a dedicated serial-to-parallel converter (iserdes), data asynchronous FIFO, control asynchronous FIFO, The data bit width is doubled and transformed into a module (gearbox), a RAM-based shift register (ram based shifter) and a controller. As the core of the CMOS data training system, the controller controls the coordinated work of each part. Under the control of the controller, the CMOS image sensor outputs serial image data through iodelay, iserdes, data asynchronous FIFO, gearbox, ram based shifter and finally converts it into parallel image data with bit width p. Bit correction process: the input serial image data is firstly delayed in phase controllable by iodelay; the bit correction is controlled by th...

specific Embodiment approach 2

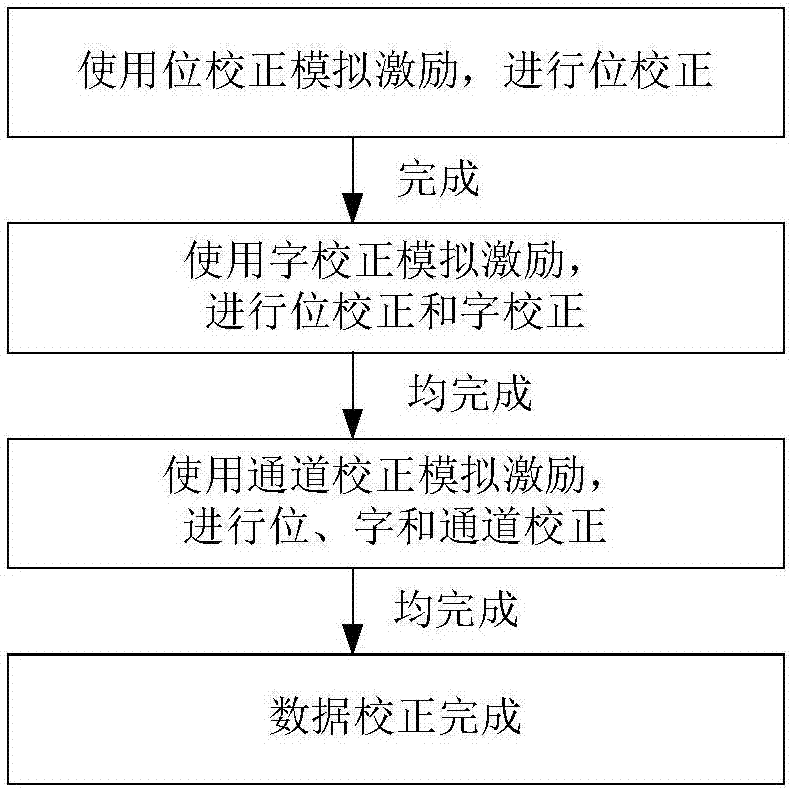

[0038] Specific embodiment 2. Combination figure 2 This embodiment is described. This embodiment is a method for performing simulation detection by using the CMOS image data training system described in Embodiment 1. This method generates different excitation signals in different correction stages, and the specific process is as follows:

[0039] 1. The generation method of the bit correction analog excitation; the purpose of the bit correction is to detect the transition edge position of the data, and find the sampling edge with a long enough stable position (the stable position is not less than 3tap), so as to obtain the optimal sampling eye. Location. Therefore, various transition edge positions should be created (the detection method based on iserdes detects the position of 12 bits at the same time, because it is to judge whether the parallel data is equal, so the transition edge can be inverted, all 0 or 1. );

[0040] The method of simulating data transition edge samp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com