Storage, forming method thereof and semiconductor device

A memory and device technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problems of unfavorable memory size reduction, the influence of capacitor capacitance, and the arrangement method cannot reach the density of capacitor arrangement.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

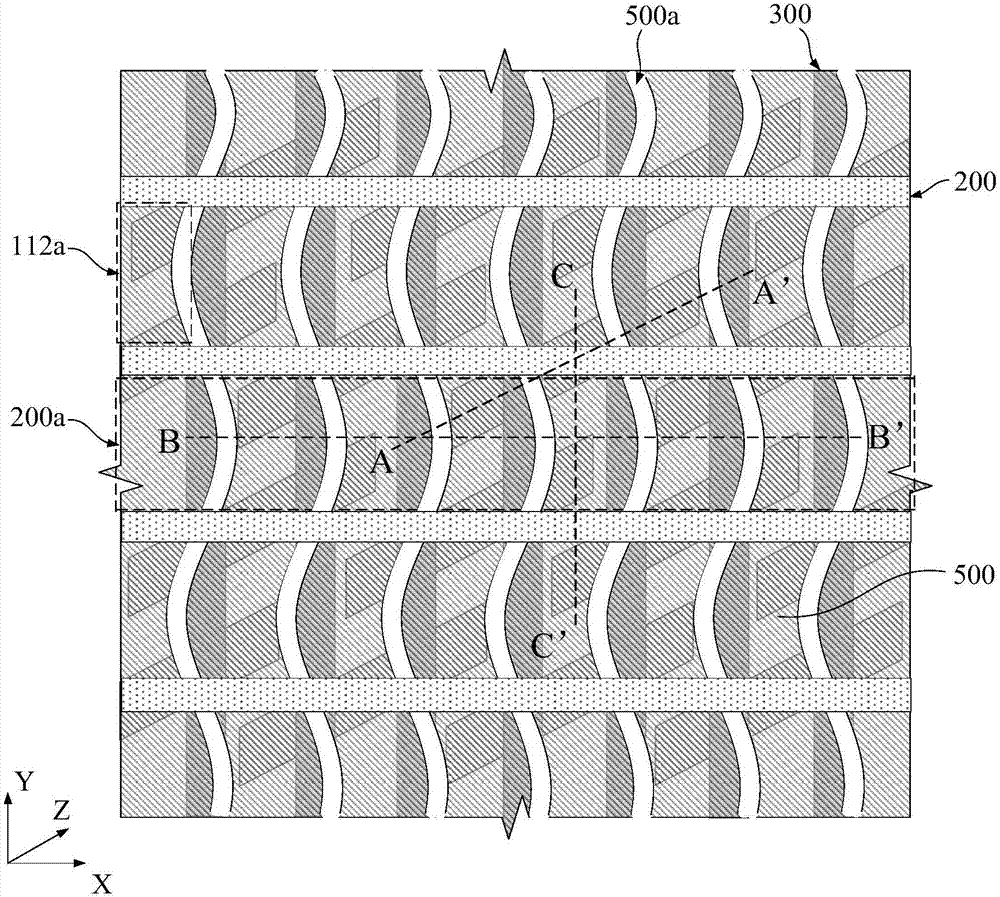

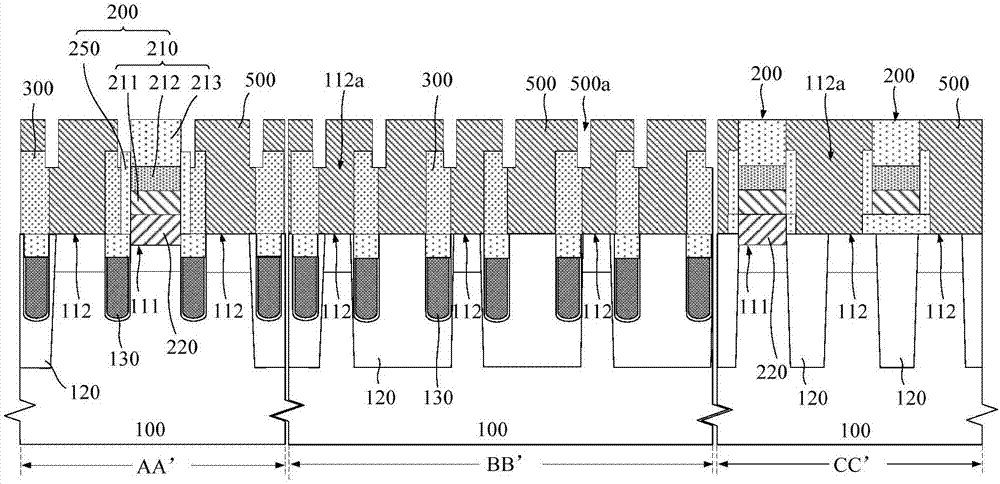

[0092] Figure 1ais a top view of the memory in Embodiment 1 of the present invention, Figure 1b for Figure 1a Shown is a schematic cross-sectional view of the memory in Embodiment 1 of the present invention along the directions AA', BB' and CC'.

[0093] combine Figure 1a and Figure 1b As shown, the memory includes: a substrate 100 , a plurality of first isolation barriers 200 formed by bit lines 210 , a plurality of second isolation barriers 300 and a plurality of node contacts 500 .

[0094] Wherein, a plurality of active regions 110 are formed on the substrate 100, and one end of each active region 110 includes a node contact region 112, and the node contact regions 112 are connected to each other through the node contact 400. to a storage capacitor (not shown).

[0095] continue to refer Figure 1a As shown, in this embodiment, a plurality of node contact regions 112 are formed in one active region 110, and a bit line contact region 111 is also formed in the active ...

Embodiment 2

[0111] The present invention also provides a method for forming a memory, the forming method can form a plurality of node contacts staggered along the extension direction of the bit line as described above, which is beneficial to increase the electrode surface area of the subsequently formed capacitor, Or the denseness of capacitor arrangement can be increased without changing the electrode surface area of the capacitor.

[0112] figure 2 It is a schematic flow chart of the method for forming a capacitor in Embodiment 2 of the present invention, as figure 2 As shown, the forming method of the capacitor includes:

[0113] Step S110, providing a substrate, in which a plurality of active regions are formed, and one end of each active region includes a node contact region;

[0114] Step S120, forming a plurality of bit lines on the substrate, the bit lines extending along the first direction are mainly used to form a plurality of first isolation barriers, and the distance ...

Embodiment 3

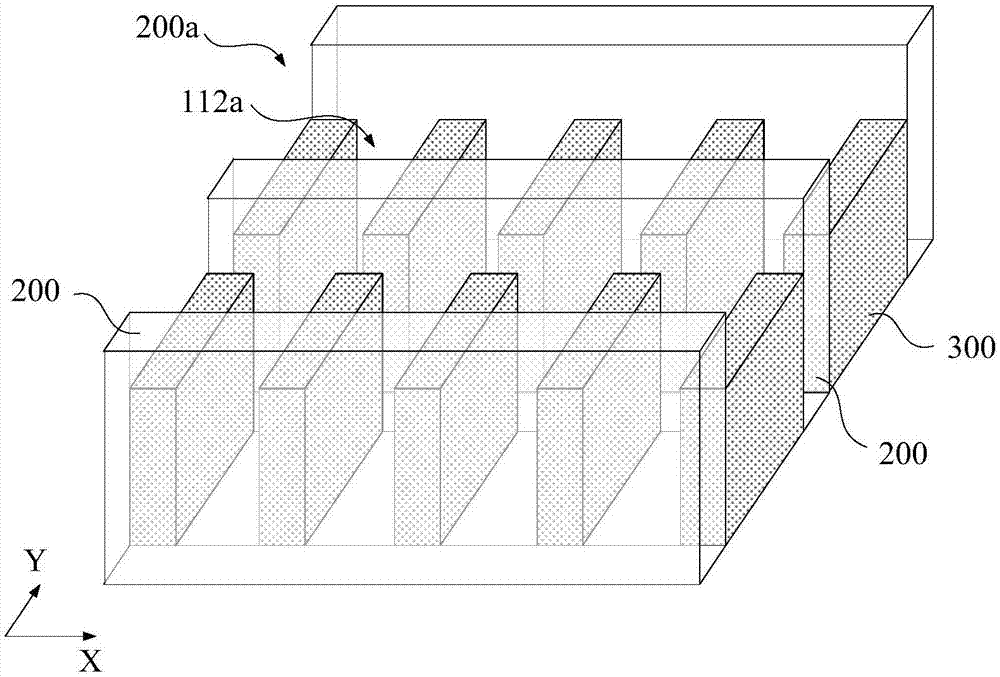

[0182] In a semiconductor device, a conductive contact is usually used to lead out the contact area and realize electrical connection with other components formed subsequently. In small-sized semiconductor devices, the components above the conductive contacts can be densely arranged in order to realize the subsequent formation. At this time, the distribution of the conductive contacts near the top can be adjusted to further improve the follow-up. The arrangement of the resulting components.

[0183] Specifically, the semiconductor device provided by the present invention includes:

[0184] a substrate having a plurality of contact regions formed therein;

[0185] A plurality of first isolation barriers are formed on the substrate and extend along a first direction, and the intervals between two adjacent first isolation barriers define an area extending along the first isolation barriers. the groove;

[0186] a plurality of second isolation barriers formed on the substrate a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More