Three-dimensional vertical memory readout circuit and readout method thereof

A readout circuit, vertical type technology, applied in the direction of static memory, digital memory information, information storage, etc., can solve the problem of long readout time of the readout circuit, achieve a wide range of applications, reduce misreading, reduce The effect of reading time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

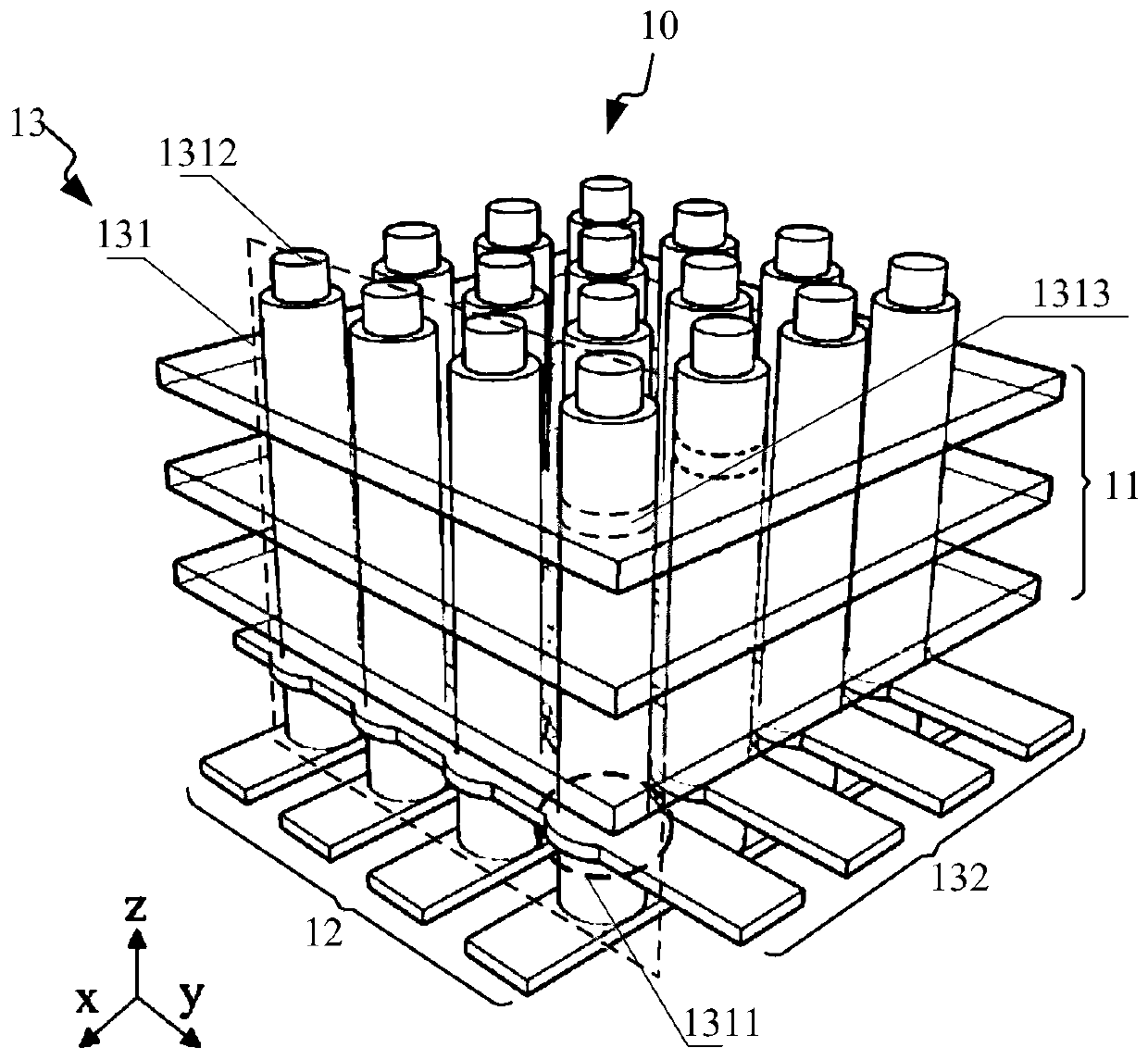

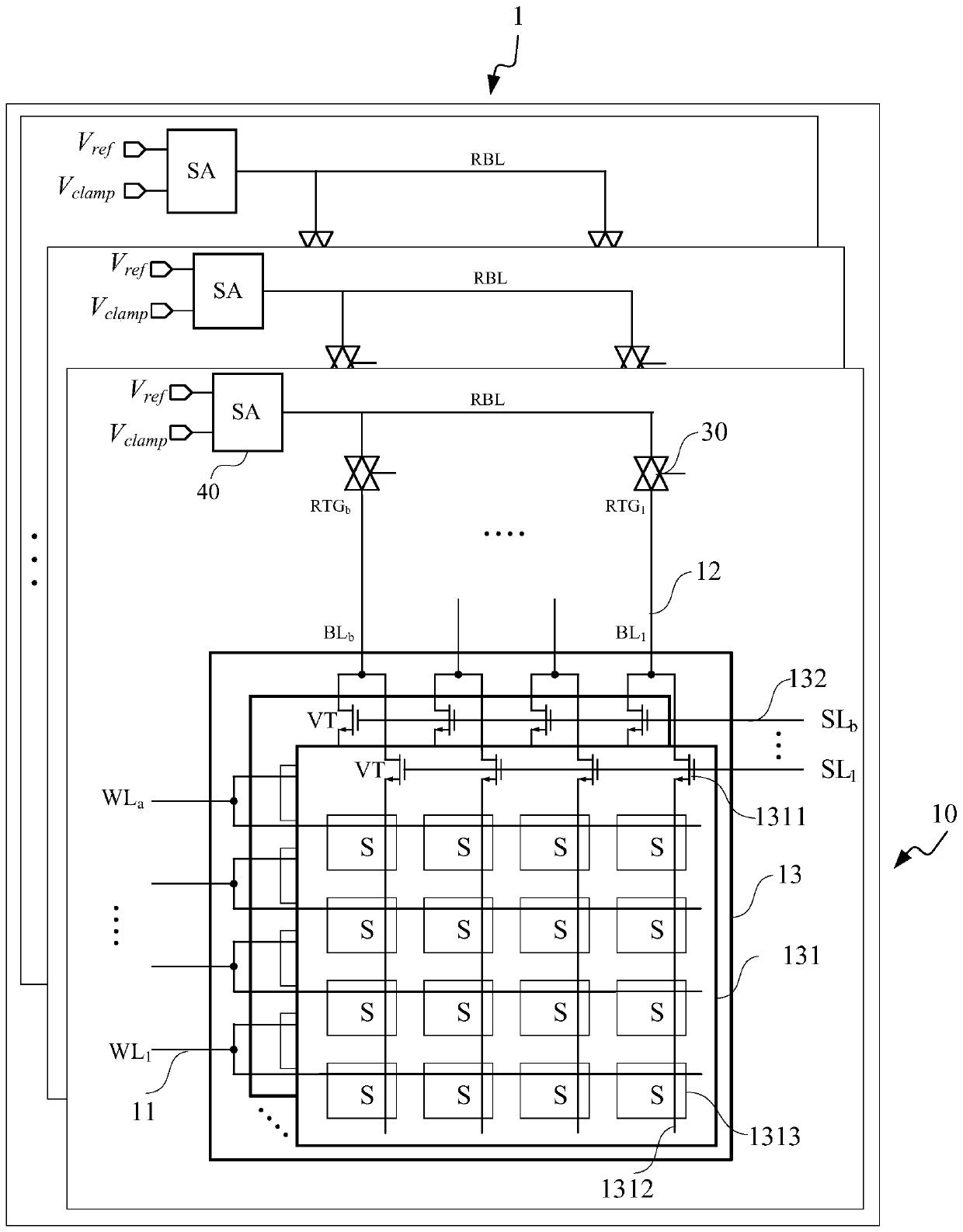

[0097] Such as image 3 and Figure 4 As shown, this embodiment provides a three-dimensional vertical memory readout circuit, and the three-dimensional vertical memory readout circuit 1 includes:

[0098] A three-dimensional vertical memory 10, said three-dimensional vertical memory 10 comprising at least one three-dimensional vertical memory sub-array 13 connected to at least one word line 11 in the horizontal direction and connected to at least one bit line 12 in the vertical direction, said The three-dimensional vertical memory sub-array 13 includes at least one array page 131 and a source line 132 connected to the array page 131, wherein the array page 131 includes the word line 11 in the horizontal direction, and passes through the first line in the vertical direction. The vertical transistor 1311 is connected to at least one local bit line 1312 corresponding to the bit line 12, and the memory cell 1313 located at the intersection of the word line 11 and the local bit li...

Embodiment 2

[0139] Such as Figure 3 to Figure 7 As shown, this embodiment provides a readout method of the three-dimensional vertical memory readout circuit as described in Embodiment 1, and the readout method includes:

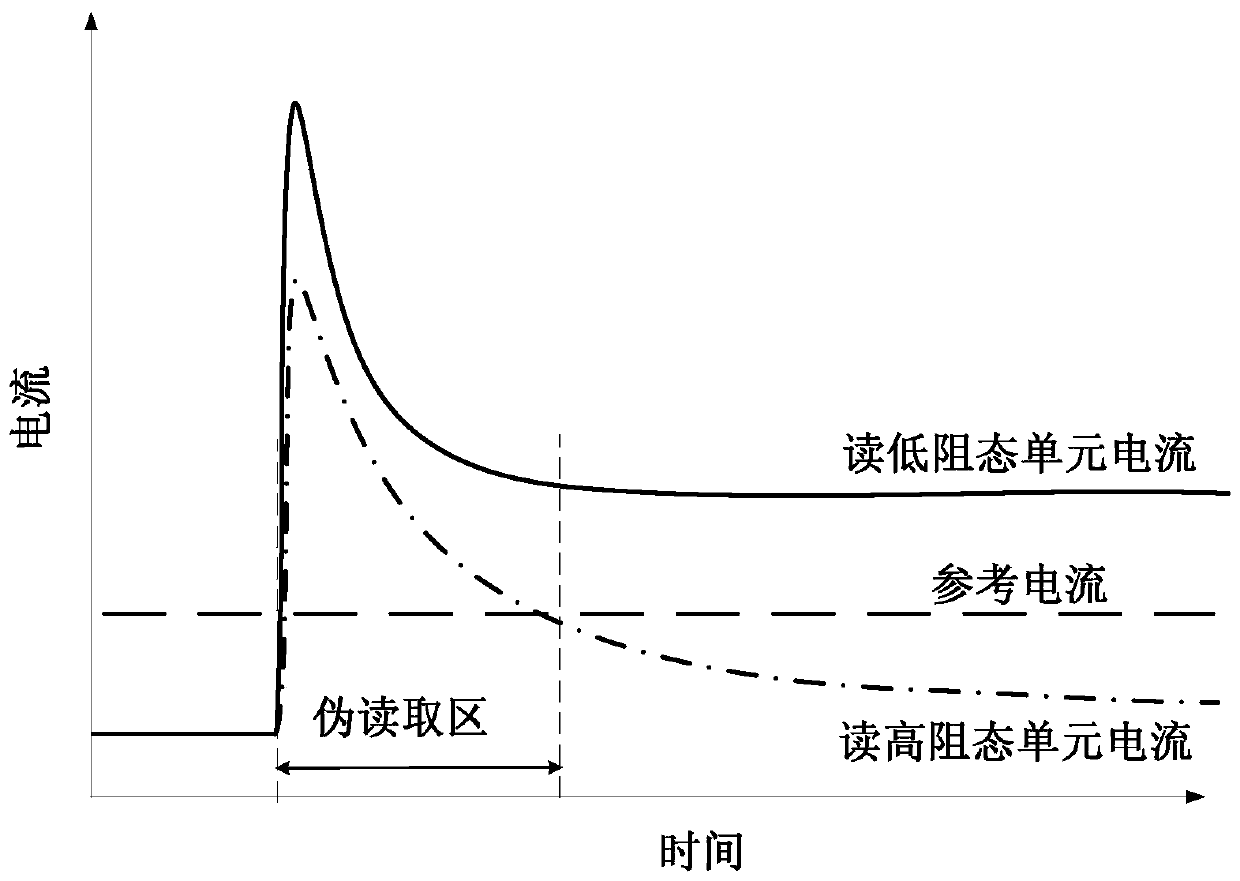

[0140] Selecting a source line, a word line and a bit line, connecting the selected memory cells in the three-dimensional vertical memory sub-array to a sense amplifier, and the sense amplifier reads the read current of the selected memory cells; at the same time , the read reference circuit starts to work to generate a dynamic read reference current;

[0141] The sense amplifier compares the read current of the selected memory cell with the read reference current, and reads out the data stored in the selected memory cell according to the comparison result;

[0142] Wherein, the parasitic parameters of the bit line and the leakage on the bit line, the leakage on the word line, the parasitic parameters of the vertical transistor, and the parasitic parameters of the read...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More