A three-dimensional memory readout circuit and readout method

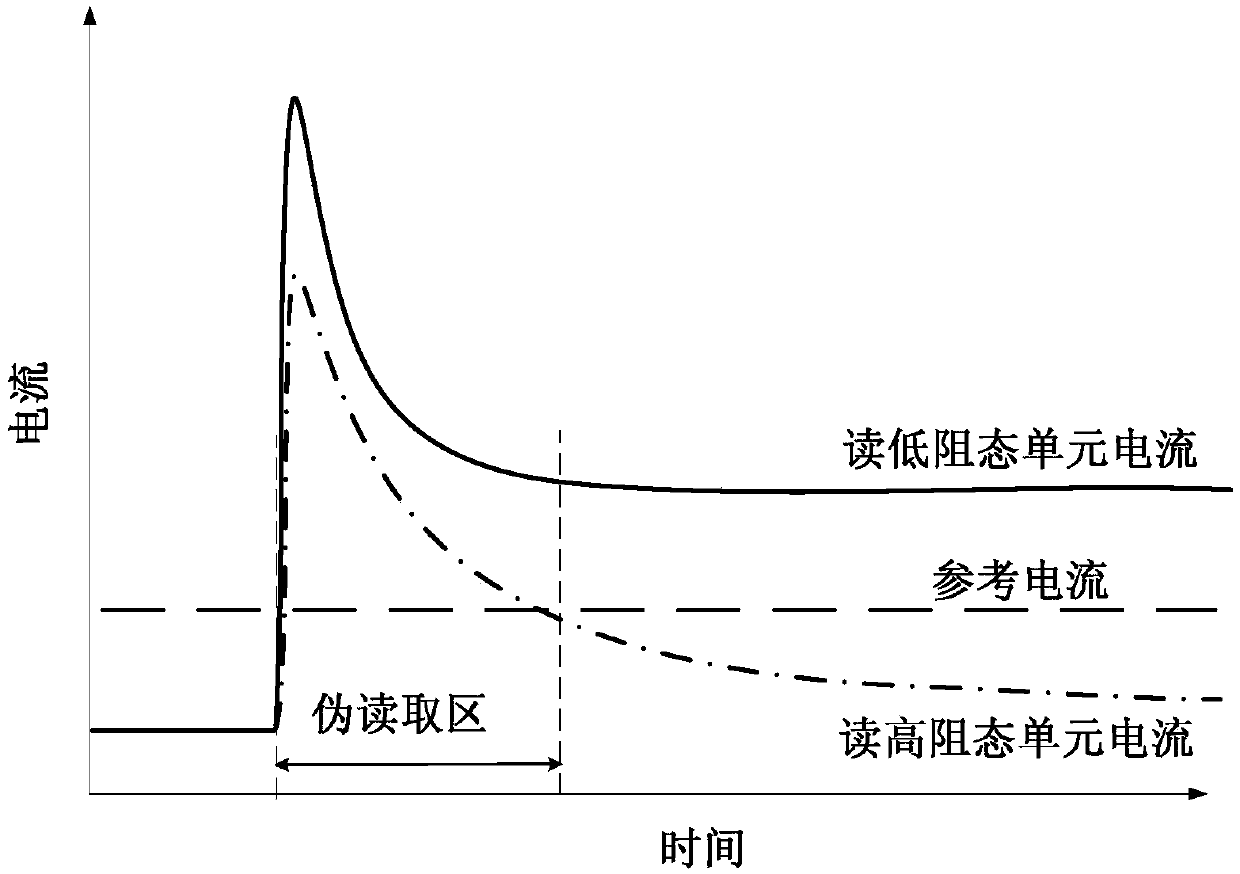

A readout circuit and three-dimensional storage technology, which is applied in the field of integrated circuits, can solve problems such as long readout time, high complexity, and misreading, so as to reduce readout time, eliminate false readouts, and reduce misreadouts Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

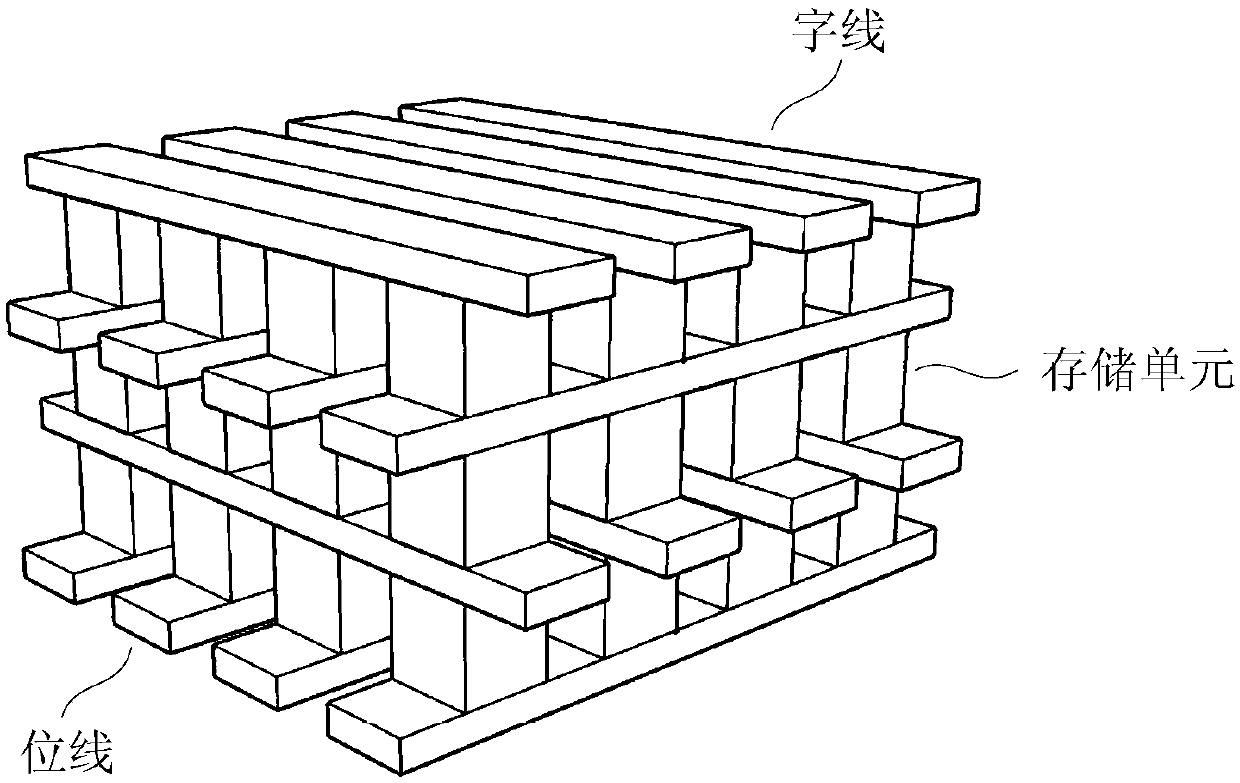

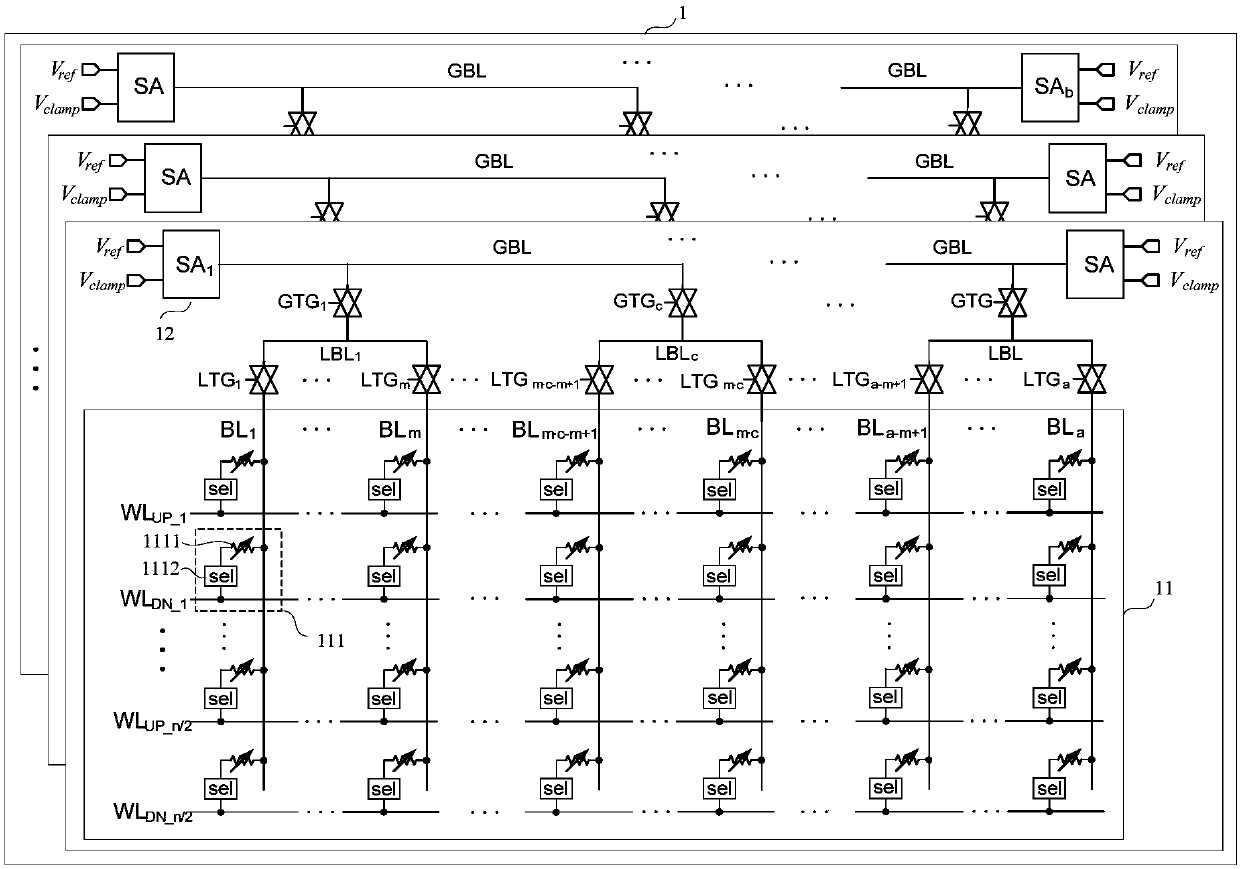

[0085] Such as Figure 3 ~ Figure 5 As shown, the present invention provides a three-dimensional memory readout circuit, which includes a three-dimensional memory cell array 1 and a read reference circuit 2 .

[0086] Such as image 3 As shown, the three-dimensional memory cell array 1 includes at least one three-dimensional memory cell sub-array 11 and a plurality of sense amplifiers 12 corresponding to the three-dimensional memory cell sub-array, and each bit line in the three-dimensional memory cell array 1 respectively passes through the transmission gate It is connected with the corresponding sense amplifier 12; the sense amplifier 12 is connected with the read reference circuit 2 and the corresponding memory cell, and compares the read reference current with the current read in the selected memory cell to generate the selected memory cell The read voltage signal of the cell.

[0087] Specifically, such as image 3 As shown, in this embodiment, the three-dimensional me...

Embodiment 2

[0107] Such as Figure 6 As shown, this embodiment provides a three-dimensional memory readout circuit, the structure of the three-dimensional memory readout circuit is similar to that of Embodiment 1, the difference is that the three-dimensional memory readout circuit further includes: connected to the reference The word line matching module between the word line W1' and the unselected bit line DESBL is used to provide the leakage on the word line to match the leakage of the storage cells on the word line in the three-dimensional memory cell array 1 .

[0108] Specifically, such as Figure 6 As shown, the word line matching module 28 includes (a-1) memory cells connected in parallel, where a is the number of bit lines connected to the same word line in the three-dimensional memory cell array 1 .

[0109] Correspondingly, the first clamping transistor 26 is based on the reference resistance value, the bit line parasitic parameters and the leakage current provided by the bit l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More