FPGA-based CRC parallel operation IP core

An operation module and matrix operation technology, which is applied in the field of data verification and can solve the problems of not supporting generator polynomials, not supporting calling CRCIP cores, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

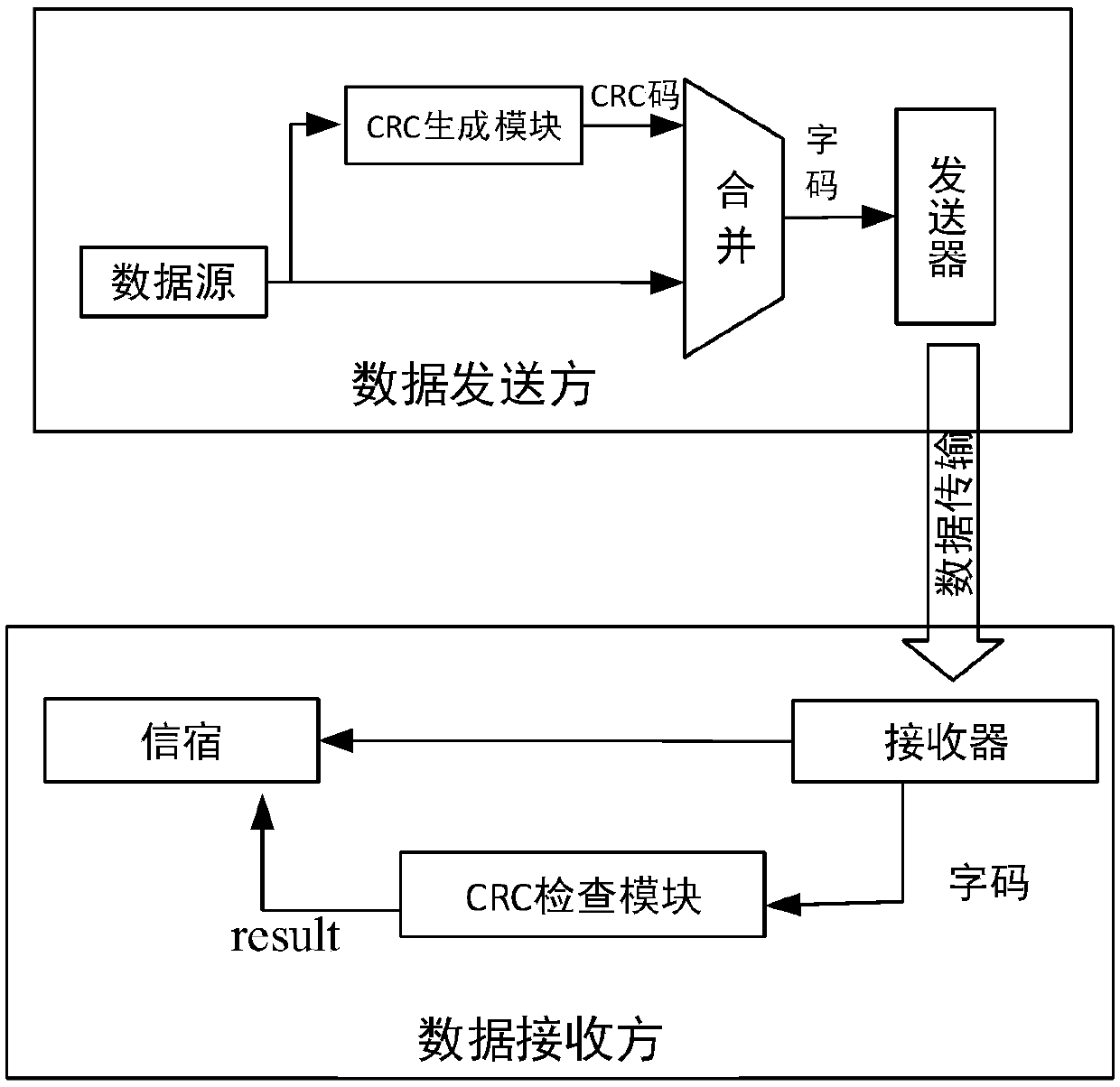

[0089]An FPGA-based CRC parallel operation IP core, which can support all generator polynomials, can configure init, refin, refout, xorout and other parameters, and can choose 8bit, 16bit, 32bit and other common parallel processing bit widths in the industry. The circuit will be based on Different generator polynomials calculate the corresponding feature matrix, and give the corresponding CRC operation results according to different configurations of users.

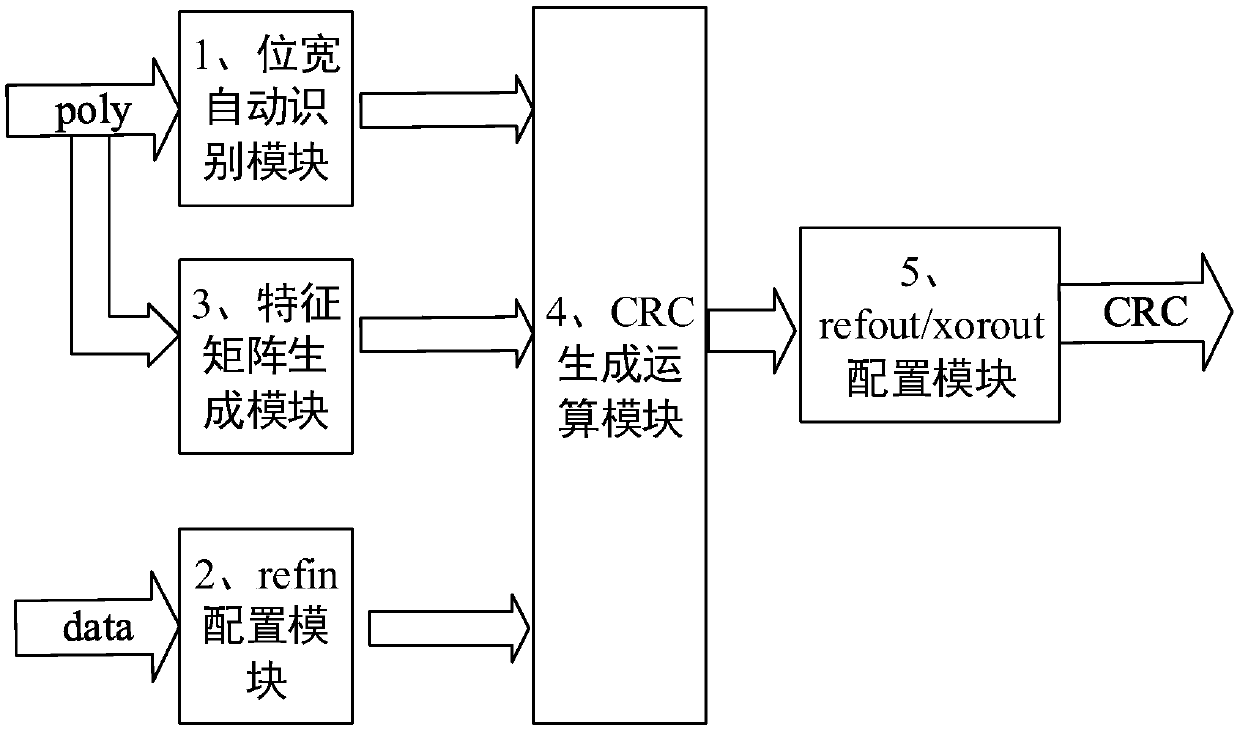

[0090] The CRC parallel computing circuit proposed in this embodiment includes the following 6 modules:

[0091] 1) CRC bit width automatic identification module

[0092] The CRC bit width automatic identification module will identify the input 33-bit representation generator polynomial binary number value, and determine the bit width of the calculated CRC according to the position of the first data in the data that is 1 in the data, and the polynomial binary number The poly and the initial value init are shifted to the ...

Embodiment 2

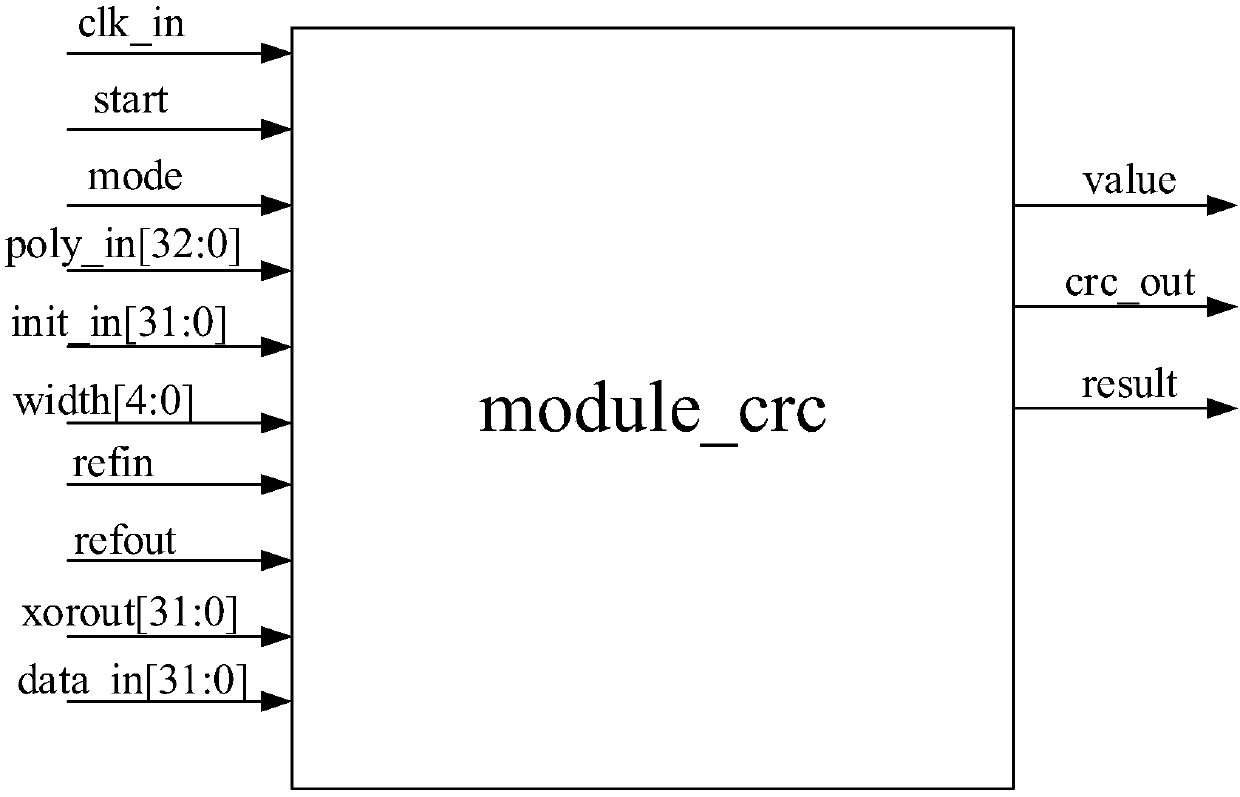

[0139] refer to figure 1 , the IP core proposed in this embodiment contains 13 interface signals in total, including 10 input signals and 3 output signals. The meanings of the specific interface signals are as follows:

[0140] clk_in: the system clock running on the IP core, controlling all operations such as data sampling and processing;

[0141] start: The start signal for CRC to start calculation. When start is high, the data_in interface signal line will be sampled at the rising edge of the clock, and a series of operations will be performed. When start is low, sampling will stop.

[0142] mode: This embodiment includes two modes of CRC operation, one is the CRC generation mode, which is used to generate the CRC check code of the data, and the other is the CRC check mode, which is used to check whether the data is wrong, when the mode is 1 When the CRC generation mode is selected, the function of the CRC generator is realized; when the mode is 0, the CRC check mode is se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com