JTAG debugging device and JTAG debugging method

A debugging method, a technology of safe configuration, applied in measurement devices, detection of faulty computer hardware, functional testing, etc., can solve problems such as inability to run, inability to realize JTAG port reopening, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

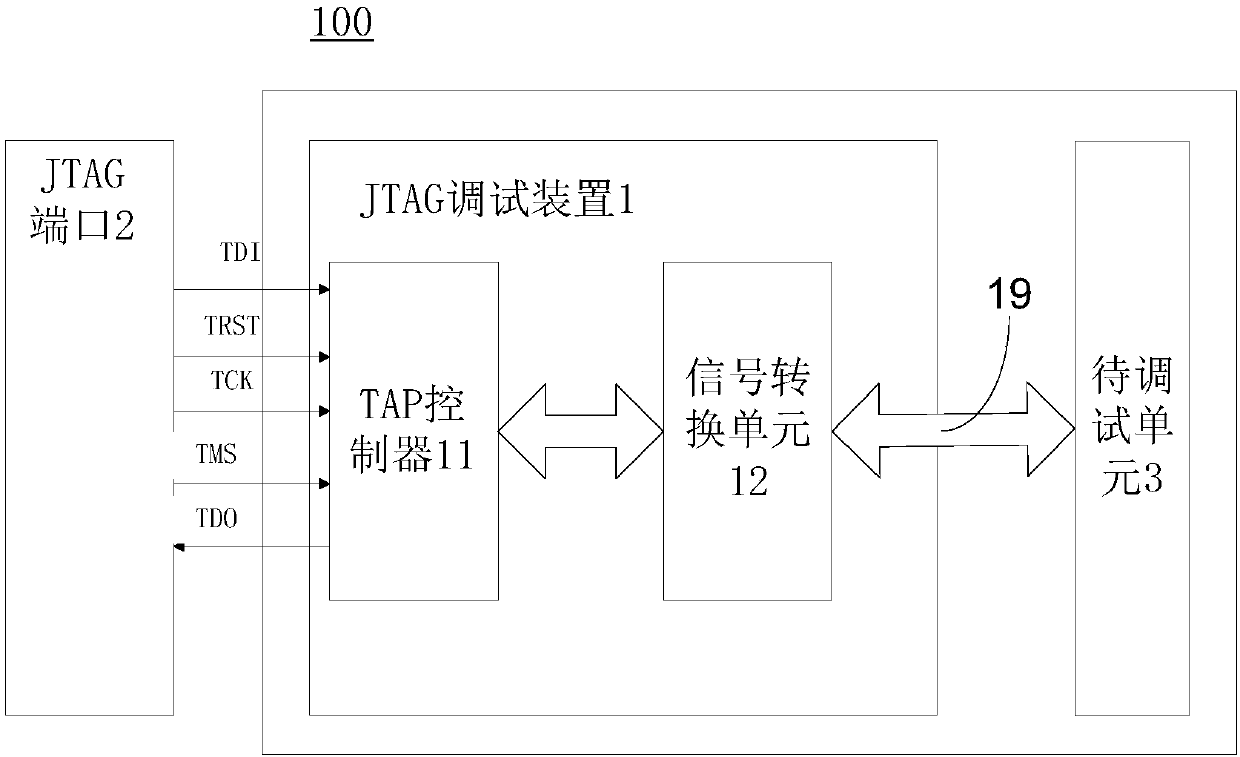

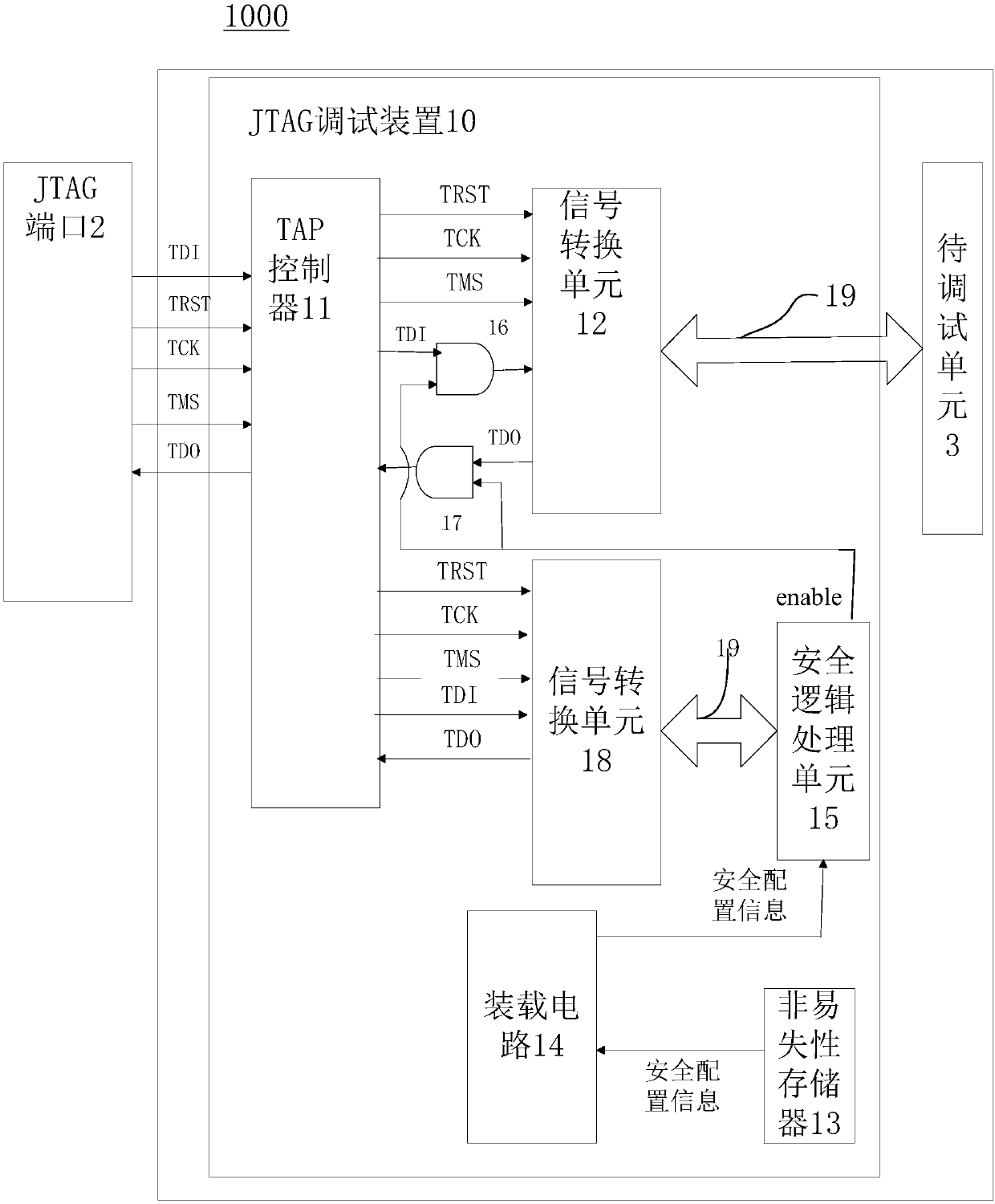

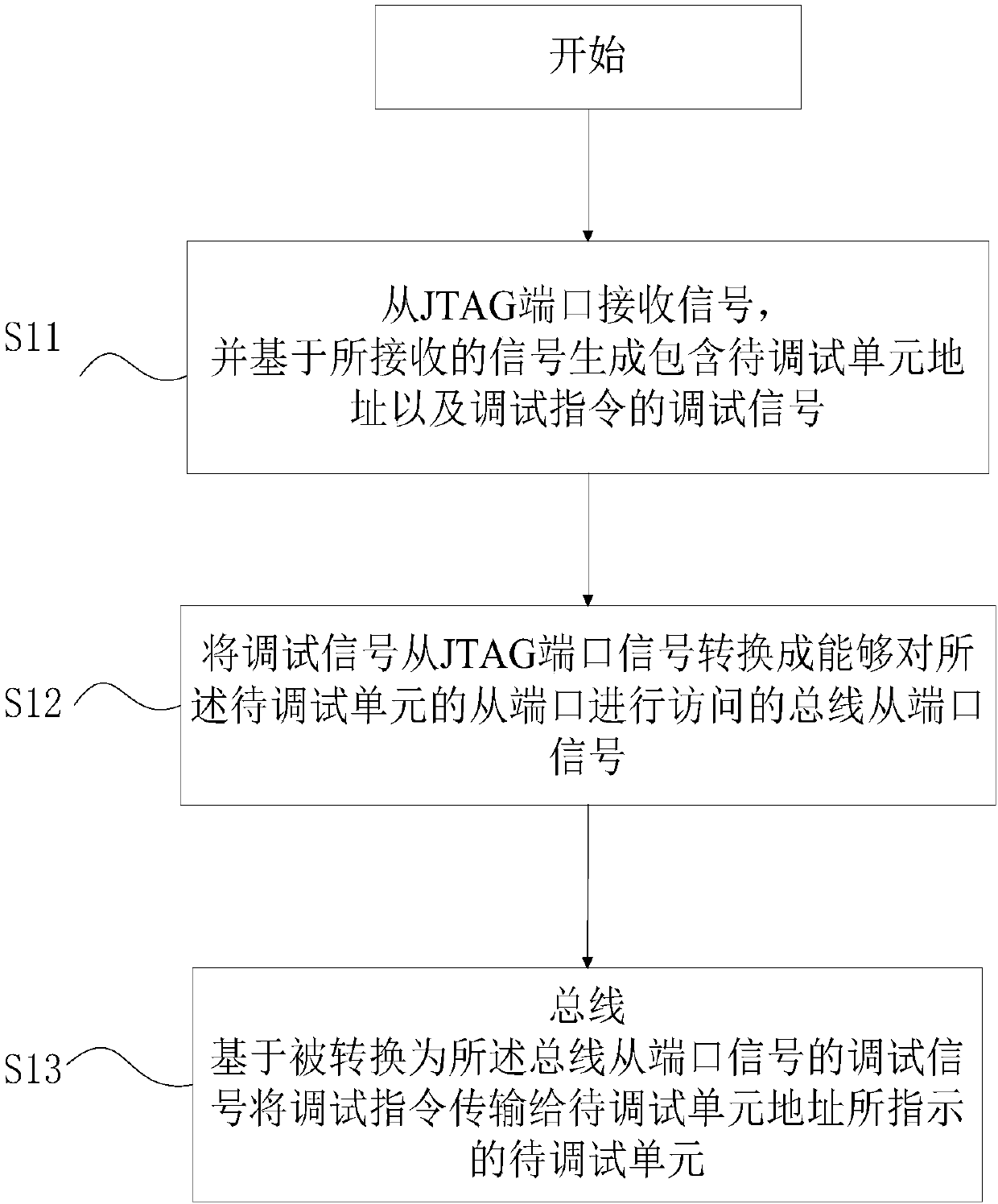

[0027] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention more clear, the following will describe the technical solutions in the embodiments of the present invention in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments are part of the present invention Examples, not all examples. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0028] Features and exemplary embodiments of various aspects of the invention will be described in detail below. In the following detailed description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be apparent, however, to one skilled in the art that the present invention may be practiced without some of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More