Data processing method among multiple FPGA chips and conversion device

A data processing and conversion device technology, applied in data exchange network, digital transmission system, error prevention, etc., can solve the problems of no multiple chip connections, complexity, large interface signal width, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0092] The specific implementation manners of the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific implementation manners described here are only used to illustrate and explain the embodiments of the present invention, and are not intended to limit the embodiments of the present invention.

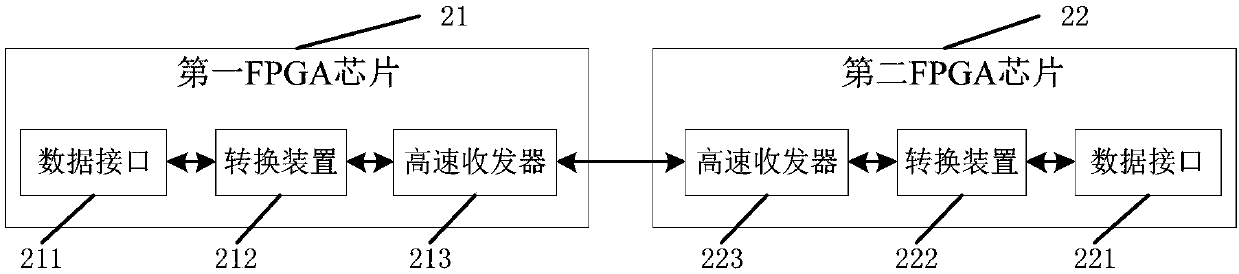

[0093] When logically dividing a large ASIC chip, it is necessary to cut between main functional components according to the flow direction of data. In this way, the signal interface between the cut modules is relatively simple, and data transmission across FPGA chips is easy. In general, data interfaces are divided into the following types:

[0094] (1) Data interface with flow control

[0095] In ASIC chip design, if the data interface between two modules has a flow control function, it generally adopts a credit value-based flow control mechanism. Under this flow control mech...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More