Method and device for power supply control of FPGA accelerator card auxiliary power supply, and medium

An auxiliary power supply and power supply control technology, applied in the field of FPGA development, can solve problems such as low efficiency, auxiliary power safety hazards, insufficient power supply to support normal work, etc., to achieve the effect of improving flexibility and reducing waste

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

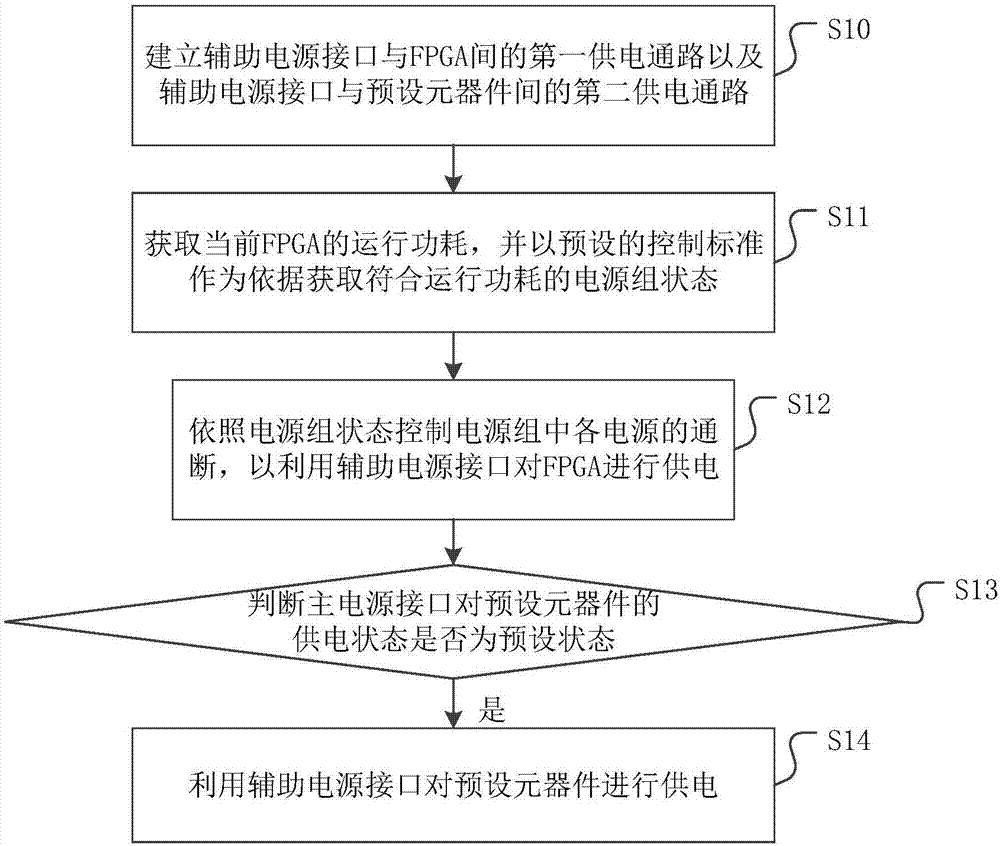

[0040] figure 1 It is a flowchart of a power supply control method for an FPGA accelerator card auxiliary power supply provided by an embodiment of the present invention. Please refer to figure 1 , the specific steps of the power supply control method of the FPGA accelerator card auxiliary power supply include:

[0041] Step S10: Establishing a first power supply path between the auxiliary power interface and the FPGA and a second power supply path between the auxiliary power interface and preset components.

[0042] Wherein, a power supply group is included in the first power supply path, and the power supply group is composed of N power supplies connected in parallel, and the on-off of each power supply is controllable; wherein, N is a positive integer greater than 1.

[0043] It should be noted that the auxiliary power interface is a power supply interface activated when the power consumption required by the FPGA accelerator card cannot be met by the main power interface,...

Embodiment 2

[0053] Based on the above embodiments, as a preferred implementation manner, the preset components specifically include a circuit fan and a linear voltage regulator.

[0054] It should be noted that circuit fans are usually used to cool down components including FPGAs, so as to relatively reduce their additional power consumption at high temperatures. Linear voltage regulators are usually used to supply power to certain low-power components. By connecting certain logic components and supplying power to the logic components, the predetermined control logic of the logic components can be executed.

[0055] This embodiment provides an application scenario. The ES1030 logic chip is connected to the ES1030 logic chip through the linear voltage regulator LDO. Provide power supply to ensure the normal operation of the FPGA. In addition, a TL331 chip can also be added as a comparator for judging whether the preset conditions are met before power-on or power-off. This application scen...

Embodiment 3

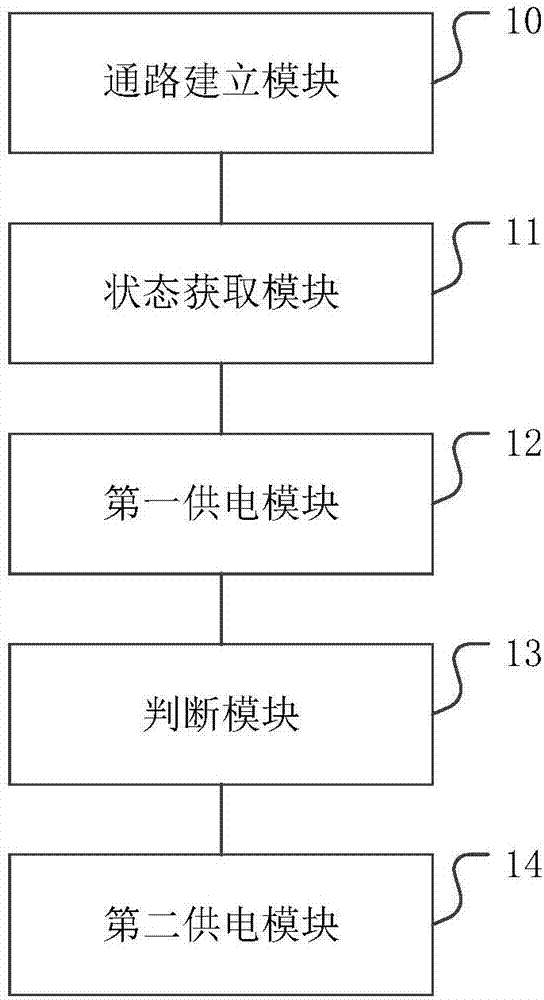

[0071] The embodiment of a power supply control method for an FPGA accelerator card auxiliary power supply has been described in detail above, and the present invention also provides a power supply control device for an FPGA accelerator card auxiliary power supply, because the embodiment of the device part and the method part The embodiments correspond to each other, so for the embodiments of the device part, please refer to the description of the embodiments of the method part, and details will not be repeated here.

[0072] figure 2 A structural diagram of a power supply control device for an FPGA accelerator card auxiliary power supply provided by an embodiment of the present invention. Such as figure 2 As shown, a power supply control device for an FPGA accelerator card auxiliary power supply provided by an embodiment of the present invention includes:

[0073] The path establishment module 10 is configured to establish a first power supply path between the auxiliary p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More