A mram readout circuit using low voltage pulses

A readout circuit, low-voltage pulse technology, applied in the direction of information storage, static memory, digital memory information, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The preferred embodiments of the present invention are described in detail below, so that the advantages and features of the present invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

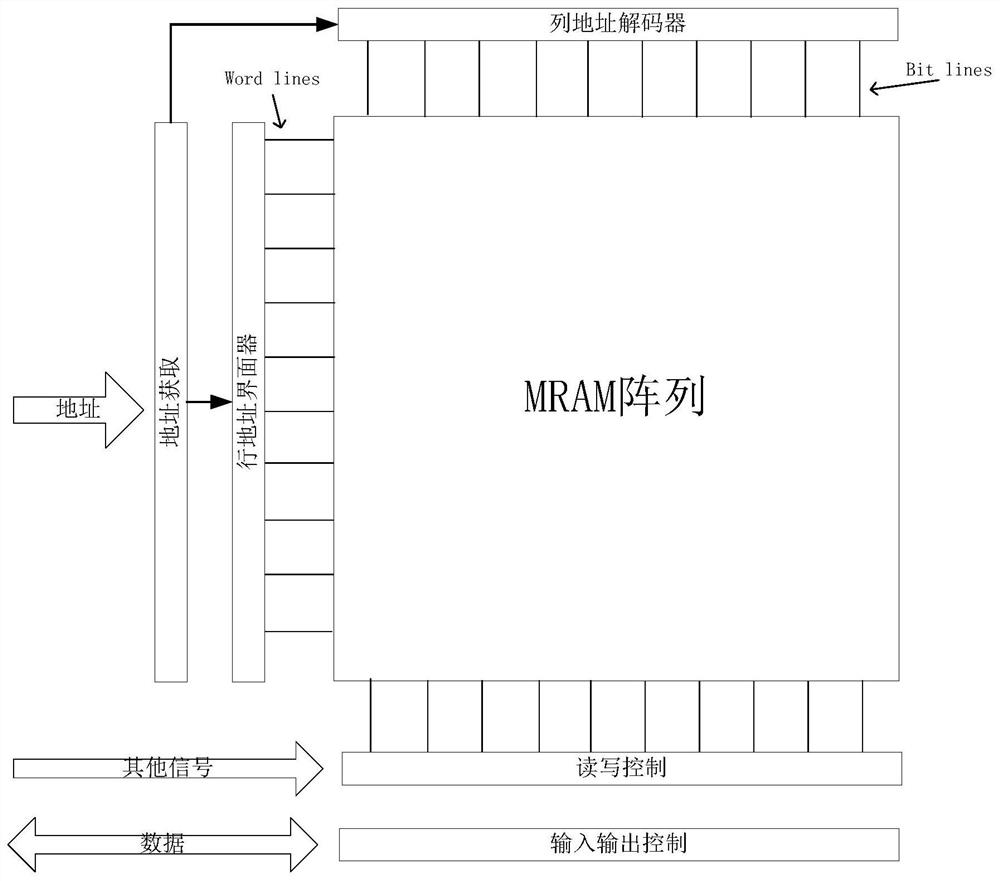

[0033] Such as Figure 5 As shown, an MRAM readout circuit using low-voltage pulses includes a plurality of equivalent MOS transistors arranged in a row, a reference unit combination and a comparator.

[0034] A plurality of equivalent MOS transistors arranged in a row are connected in parallel and divided into two groups, the first group is Pb1, Pb2...Pbk, and the second group is Pax (x=1, 2,...).

[0035] The reference cell combination consists of k reference cells connected in parallel, some of the k reference cells are configured in the P state, and the rest are configured in the AP state, and the reference cells are divided into multiple columns and placed in the MRAM memory cell array.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More