A device and method for adjusting transistor substrate voltage and correcting on-chip non-uniformity

A technology of substrate voltage and non-uniformity, which is applied in measurement devices, radiation pyrometry, optical radiation measurement, etc., can solve the problems of low circuit expansion performance and large noise contribution, so as to improve circuit performance, reduce noise contribution, Improve the effect of application range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

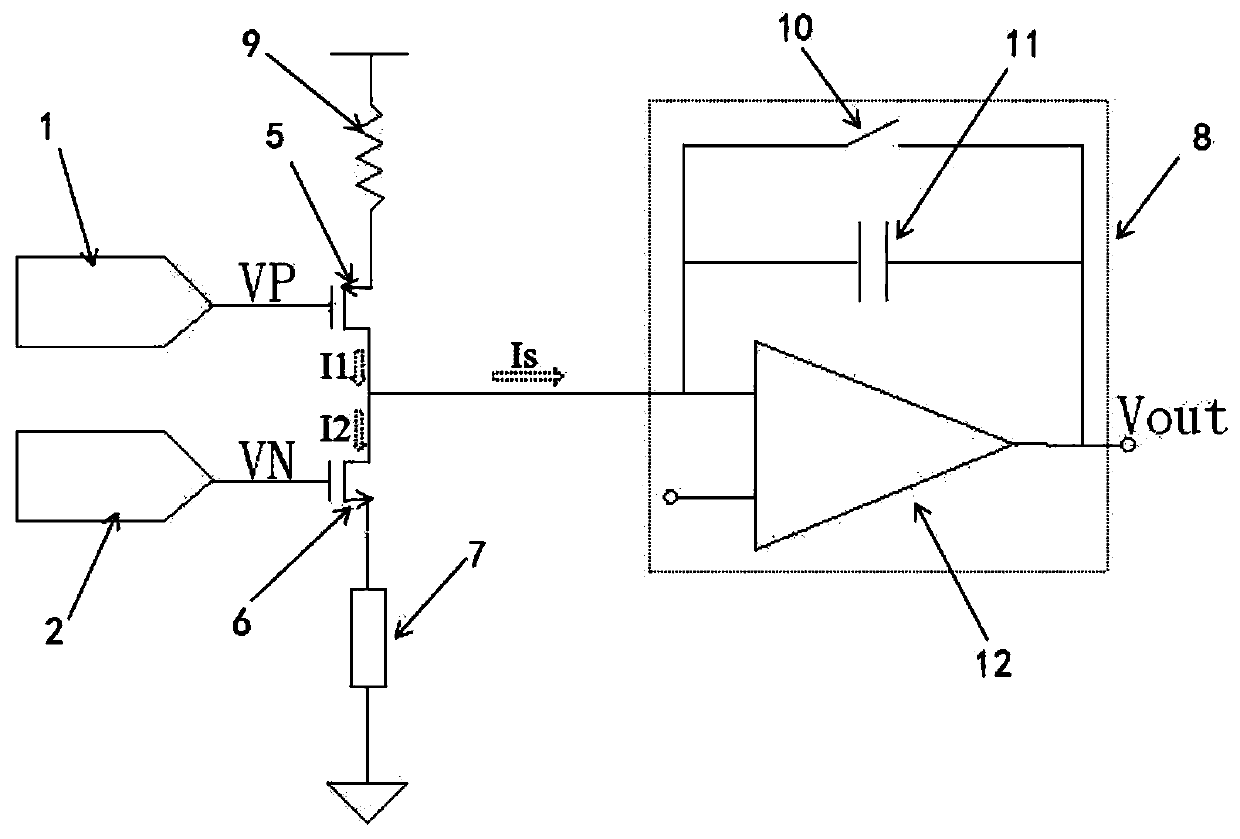

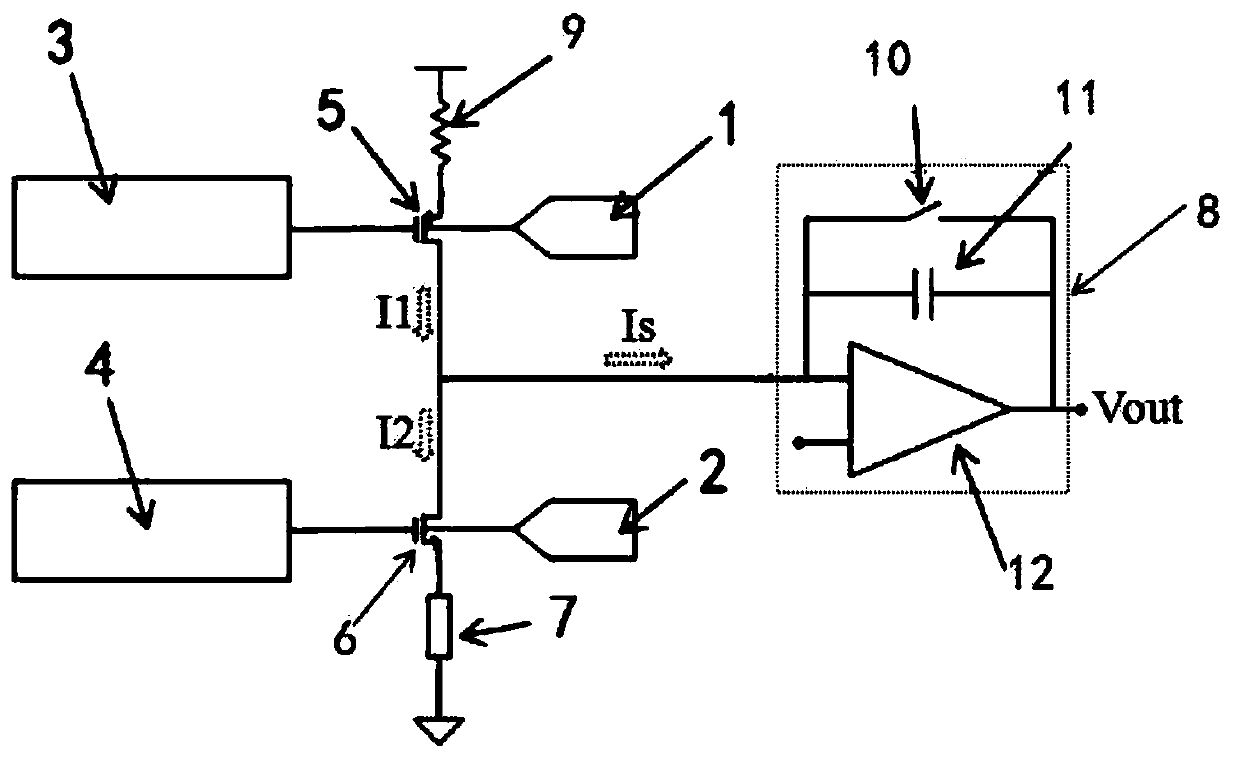

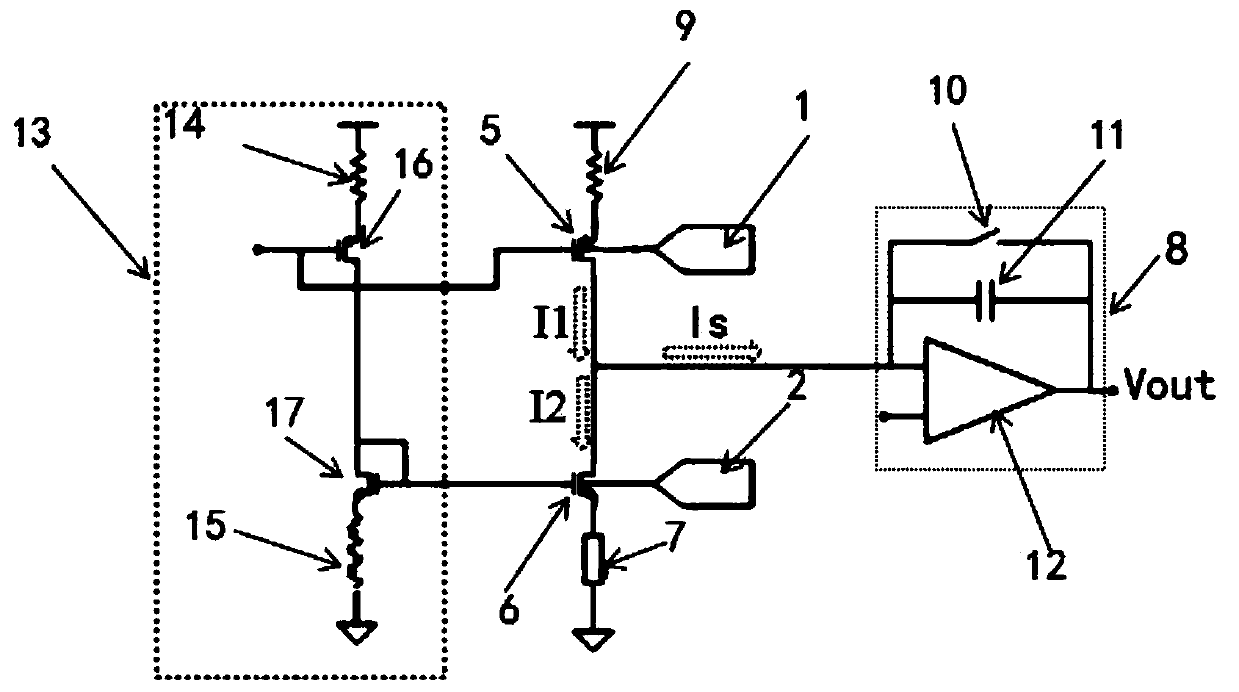

[0030] Such as figure 2 As shown, a structural schematic diagram of adjusting transistor substrate voltage to correct on-chip non-uniformity, including: a first analog-to-digital converter 1, a second analog-to-digital converter 2, a PMOS transistor 5, an NMOS transistor 6, and a sensor detection element resistance array 7. Integrating circuit 8, non-photosensitive resistor 9, functional module circuit 13, wherein, PMOS tube is a P-channel field-effect transistor, and NMOS tube is an N-channel field-effect transistor; the drain of NMOS tube 6 is connected to sensor detection element resistance array 7 , the source is respectively connected to the drain of the PMOS transistor 5 and the integration circuit 8; the sou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More