Manufacture method of optical voltage/electric field sensor wafer capable of suppressing piezoelectric resonance

An electric field sensor, optical voltage technology, applied in the manufacture/assembly of piezoelectric/electrostrictive devices, piezoelectric/electrostrictive/magnetostrictive devices, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

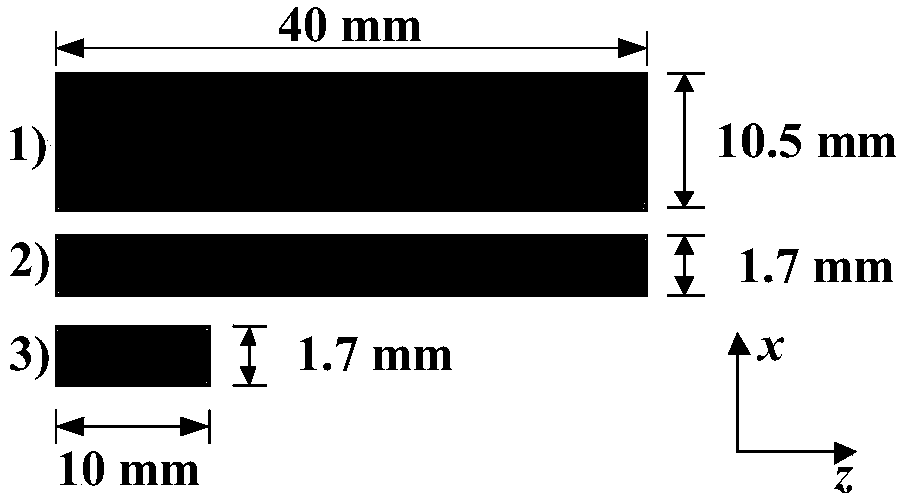

[0047] Embodiment 1: the first kind of scheme of the present invention is applied to the making of the common path interference sensor chip that can suppress piezoelectric resonance under the lightning wave condition, and the common path interference sensor that is made of this chip is used under the lightning wave condition in the power grid line, The frequency of the electric field is f min ~ f max (The present embodiment is 50Hz~1MHz) voltage / electric field measurement, the width direction of wafer is perpendicular to light source transmission direction; The method comprises the following steps:

[0048] S1: Select a parallelogram test wafer with the same material as the wafer to be produced, and the width of the test wafer is W 0 (the present embodiment is 5.6mm);

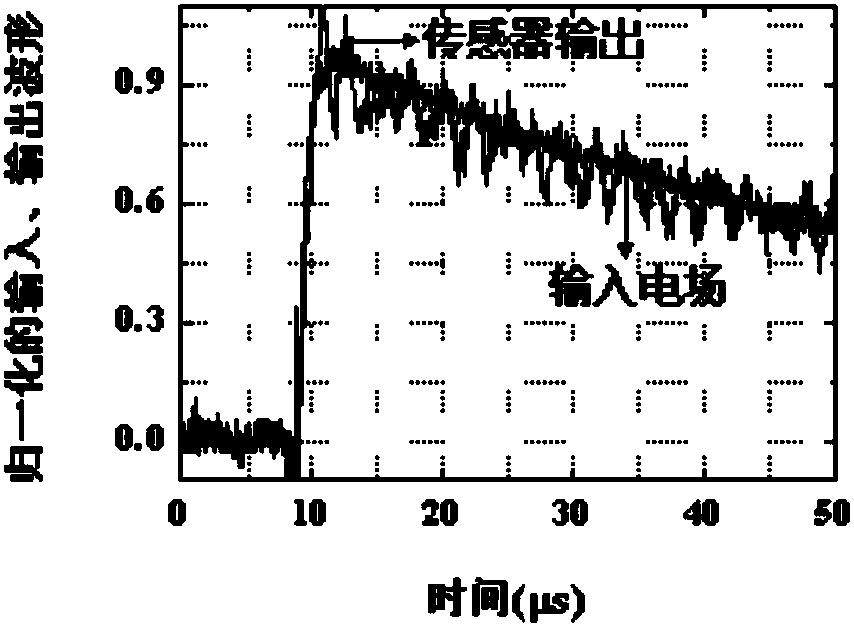

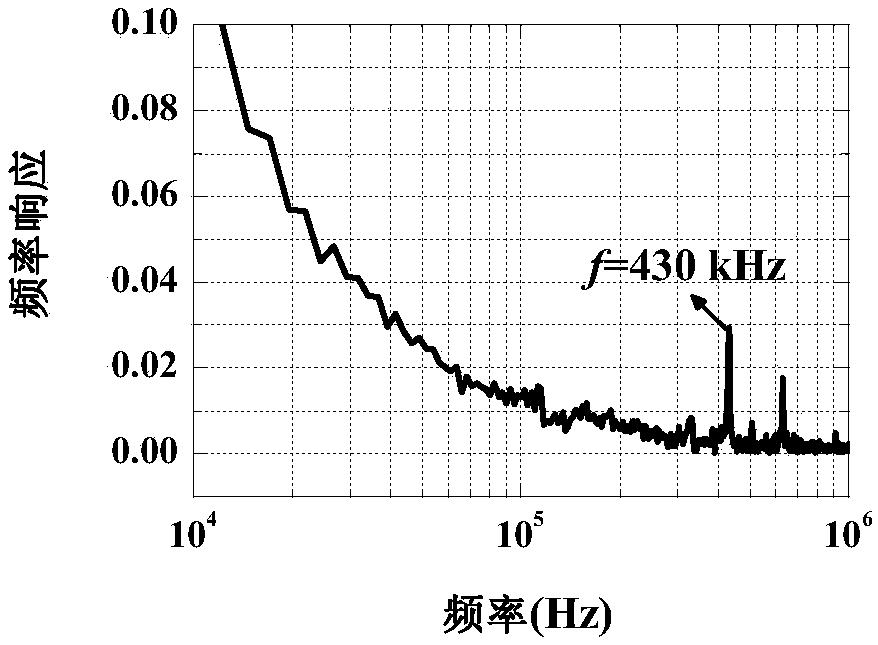

[0049] S2: The frequency range of the electric field on the test wafer is f min ~ f max The frequency response test of the electric field, measured the piezoelectric resonance fundamental frequency of the t...

Embodiment 2

[0054] Embodiment 2: The second kind of scheme of the present invention is applied to the making of the common path interference sensor chip that can suppress piezoelectric resonance under the lightning wave condition, and the common path interference sensor that this chip forms is used for under the lightning wave condition in the power grid line, electric field frequency is f min ~ f max (The present embodiment is 50Hz~1MHz) voltage / electric field measurement, the width direction of wafer is perpendicular to light source transmission direction; The method comprises the following steps:

[0055] S1: Select a parallelogram test wafer with the same material as the wafer to be produced, and the width of the test wafer is W 0 (the present embodiment is 5.6mm);

[0056] S2: The frequency range of the electric field on the test wafer is f min ~ f max According to the electric field frequency response test, the piezoelectric resonance fundamental frequency of the wafer is f 0 (...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More